一種基于基準電壓的高速IO

許 迪 孫長江 羅堯宇

(深圳市國微電子有限公司,廣東 深圳 518057)

一種基于基準電壓的高速IO

許 迪 孫長江 羅堯宇

(深圳市國微電子有限公司,廣東 深圳 518057)

本論文提出一種通過基準電壓來減小延時的IO設計方法,設計出具高速特性的IO模塊,從而滿足高速SRAM產品的使用需求。該模塊主要的設計思路為:通過基準電壓提供一個中間態電壓,通過中間態電壓快速響應,減小IO的延時。通過HSPICE仿真表明,這款電路能滿足200M hz SRAM需求,并通過流片,驗證此結構是可行的。

IO;高速;翻轉速度

1 引言

為滿足高端存儲器的芯片的高速時序要求,其對IO的延時亦有較高的要求。一般來講,適當地提升驅動能力可以有效減少IO的延時。但是提高驅動能力會帶來一系列副作用,如更高的功耗,更大的地彈及噪聲,需要占用更大的面積。本文中設計出一種基于基準電壓的IO結構,利用基準電壓使IO在電平轉換的時候進行高速翻轉,在盡量減小驅動能力的同時,可以滿足高速的需求。

2 總體電路

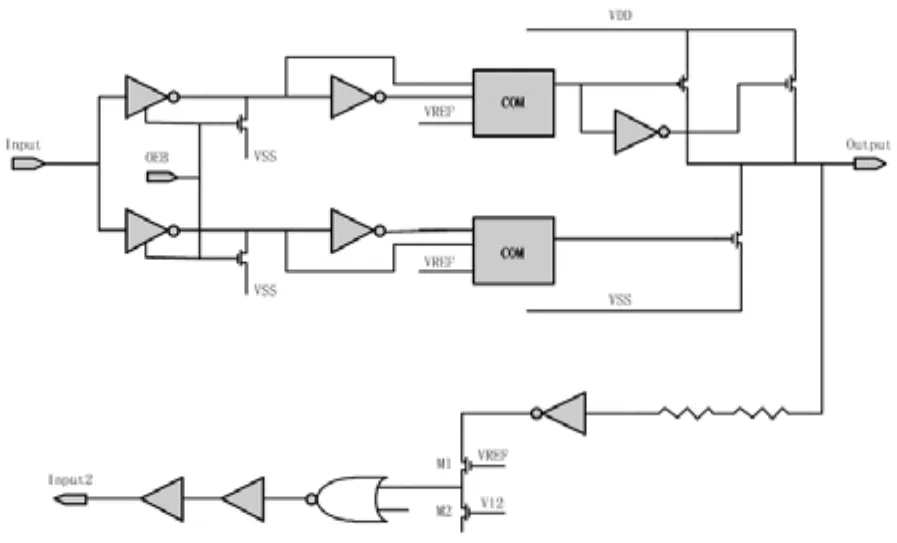

總體電路可以分為兩部分,一部分為IO模塊,另一部分為帶隙基準。其中IO模塊提供高低電平的轉換以及ESD保護。帶隙基準模塊為IO提供一個基準電壓,協助IO進行高速翻轉。其中帶隙基準為常用結構,在此文中不再詳細介紹。本文重點介紹IO模塊部分,其中可以分為輸入部分以及輸出部分。其總體結構圖如圖1所示。

圖1 總體IO結構

3 輸入部分

輸入部分主要完成將外部信號輸入到芯片內部的任務,同時將外部的信號電壓轉換為內部的信號電壓。在本論文中,外部信號的電壓為3.3V/2.5V,內部信號的電壓為1.2V。電壓的轉換主要由兩個N管構成,如圖2所示,其中M 1管的柵極接基準電壓,為2V,M 2管的柵極接1.2V電壓。

當輸入信號為高時,M 1漏極為3.3V,M 1管導通,由于M 2管寬長比遠遠小于M 1管寬長比,故M 2的導通電阻比M 1的導通電阻大很多,因此其分壓較大,但是由于M 1管的柵極接VREF電壓,為保證其導通,M 1的源極最高電壓不能高于VREF-Vthn。至此,輸入信號為高時的電壓轉換完成[1]。

當輸入信號為低時,M 1的漏極為0V,由于M 1管柵極接VREF電壓,M 2管的柵極接1.2V電壓,處于打開狀態,故M 2的漏極電荷會通過M 1管和M 2管釋放出去,迅速拉低到0V。至此輸入信號為低時的電壓轉換完成。

圖2 輸入部分

4 輸出部分

輸出部分主要完成將內部信號輸出到芯片外部的任務,同時將內部信號的電平轉換為外部信號所需的電平。在輸出部分,主要包含兩大部分,分別為電壓轉換部分及驅動部分。其中電壓轉換部分將內部1.2V電壓轉換為2.5V/3.3V電壓,驅動部分主要增強輸出的驅動能力,以滿足驅動大型負載的要求。

圖3 輸出部分

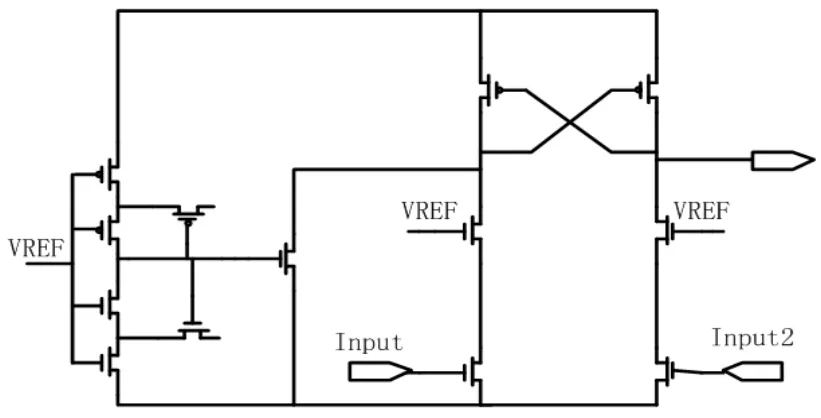

電壓的轉換部分主要由一個帶有基準電壓的比較器完成,其結構如圖4所示,比較器的兩端由N管組成,并通過上面的N管組成cascode結構,提高放大增益倍數,在N管的上面是由P管組成的正反饋系統,由于正反饋的作用,當兩個P管的漏極電壓稍微發生差分變化時,會將差分變化迅速放大。因此比較器的響應速度非常高[2]。

通過比較器之后的電壓為2.5V/3.3V,用此電壓來進行驅動部分的驅動管開關。當輸入電壓為高時,上面P驅動管的柵極電壓被拉為低電壓,P驅動管打開,上面N驅動管的柵極電壓被拉為高電壓,N驅動管打開,兩個管子同時對輸出充電,下面的N驅動管的柵極電壓被拉為低,N驅動管關閉,因此輸出電壓將被拉高。當輸入電壓為低時,情況正好相反,上面P驅動管的柵極電壓被拉為高電壓,P驅動管關閉,上面N驅動管的柵極電壓被拉為低電壓,N驅動管關閉,下面的N驅動管的柵極電壓被拉為高,N驅動管打開,對輸出放電,因此輸出電壓將被拉低。

圖4 比較器

5 仿真結果

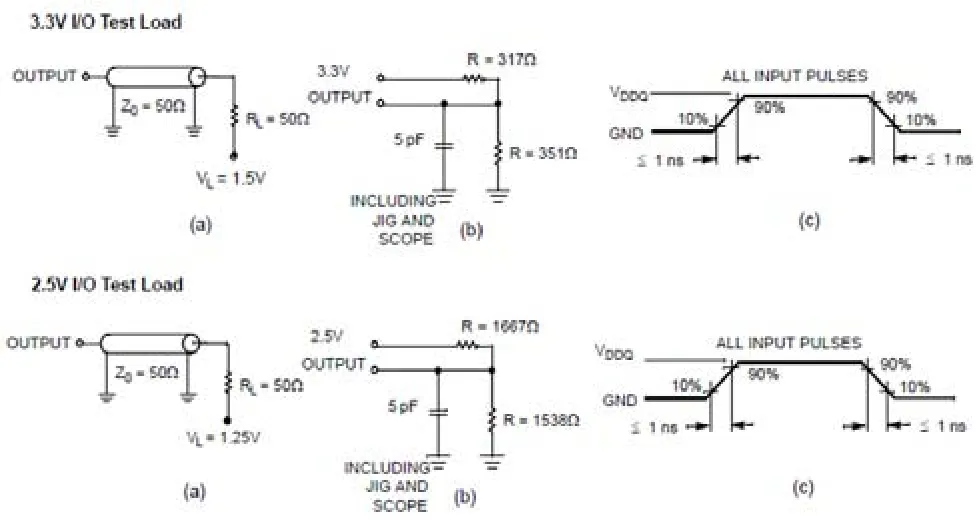

本結構通過版圖設計后,提取帶有寄生參數的后仿真網表,以求更加精確的仿真結果。其負載情況如圖5所示。

圖5 負載模式

輸入部分的負載:0.1pF

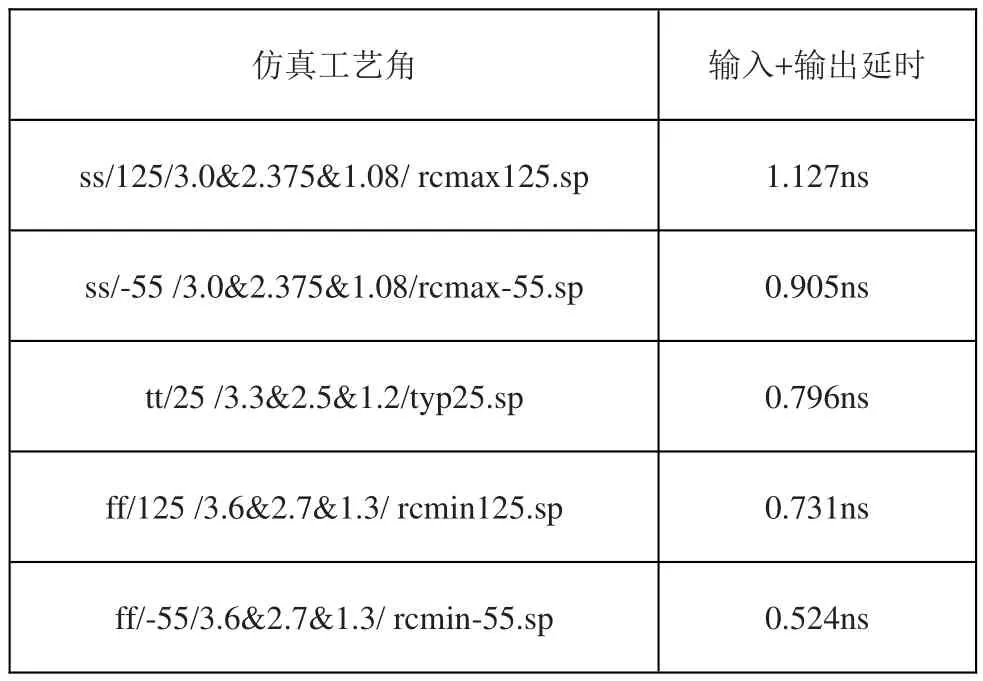

表1 (vref2=2V輸入:1.2V/250MHz/tr=500ps)

表2 (vref2=2V輸入:1.2V/250MHz/tr=500ps)

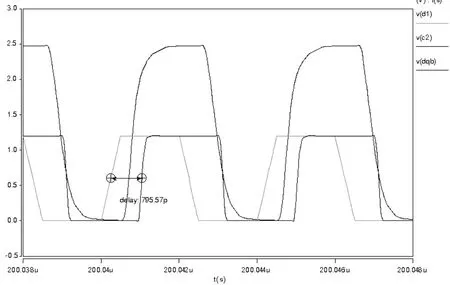

以下為延時波形示意圖,工藝角為tt。

圖6 3.3V電壓波形

圖7 2.5V電壓波形

從仿真結果可以看出,IO基本可以滿足1.2ns以內的延時需求。

6 結論

本論文通過提出一種基于基準電壓的IO結構,分析其輸入部分及輸出部分的工作原理,以降低IO的延時,通過此種結構,可以降低IO的延時,為SRAM等產品提供更大的時序空間。

[1]Behzad Razavi.模擬CMOS集成電路設計[M].北京:清華大學大學出版社,2005.

[2]Phillip E.Allen,DouglasR.Holbeng.CMOS模擬集成電路設計[M].北京:電子工業出版社,2007.

Design of the High Speed IO Based on Bandgap Reference Voltage

Xu Di Sun Changjiang Luo Yaoyu

(Shenzhen StateM icroelectronicsCo.,Ltd.,Shenzhen 518057,Guangdong)

This paper introducesa designmethod through the bandgap voltage to reduce the delay of IO,presentsa design of IO w ith high speed,whichmeets the requirementof high speed SRAM products.Themain design idea of thismodule is:With bandgap supplying am iddle stage voltage,themodule can response fast,which reduces the delay of IO.Through the HSPICE simulation results,the demand of 200Mhz SRAM can be satisfied by this circuit,and themodulehasbeen proved reliableby taping out.

yword】 IO;high speed;flip speed

TN432

A

1008-6609(2017)06-0045-03

許迪(1988-),男,遼寧大連人,碩士,工程師,研究方向為模擬集成電路設計。