一種全雙工射頻收發系統的設計與實現

謝作全 康 超 王宇

(上海航天電子技術研究所,上海 201100)

一種全雙工射頻收發系統的設計與實現

謝作全 康 超 王宇

(上海航天電子技術研究所,上海 201100)

隨著通信技術的進步,射頻無線通信的技術取得了迅猛發展,無線通信技術也日趨成熟和穩定,射頻收發系統的通用化和小型化成為一個重要的發展方向。本文對基于軟件無線電技術的射頻收發原理進行介紹,并對幾種常用的方案進行了分析,對比了各方案集成化、小型化的優缺點,最后使用ADI生產的一款集成式寬帶捷變收發器,構建硬件平臺,實現一種簡易的全雙工多通道的射頻收發系統。

射頻通信;全雙工;軟件無線電;FPGA

1 概述

近年來,隨著射頻無線通信技術的不斷發展,射頻無線通信已經廣泛地應用于我們日常的生活中,如個人無線通信、無線基站、衛星通信、全球衛星定位系統等。而軟件無線電技術(SDR)作為新型的射頻無線通信體系結構,減少了模擬環節,把數字處理盡量地靠近天線,利用相同的硬件平臺,只需要通過軟件的更新,就可以實現不同碼速率,不同調制方式,不同編碼方式。但由于軟件無線電技術成本相對較高,目前更多地應用于軍工等少數高端領域。

目前ADI公司推出了AD936x系列射頻捷變頻收發器,集成式的RF收發器AD936x包括混頻器、頻率合成器、模擬濾波、數據轉換器和其他功能。AD936x的推出使基于軟件無線電技術的無線通信系統的實現更加簡易,本文將利用AD9361+FPGA的硬件框架,構建一個小型化的全雙工射頻收發系統。

2 工作原理

軟件無線電的中心思想是構建一個通用化、模塊化、標準化及可重構的硬件平臺,將數模模數轉換器(ADC,DAC)盡可能地靠近天線,采用相同的射頻模擬前端,只通過修改軟件的方法,來實現不同的通信系統。

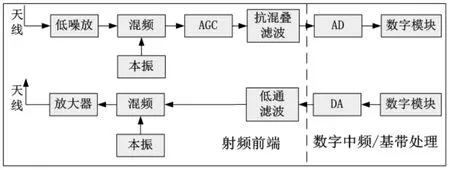

基于軟件無線電技術的射頻無線通信框架已經比較成熟,一般采用射頻收發前端和數字中頻/基帶處理模塊實現。從功能角度上看,整個系統可以分為收發鏈路兩部分,接收鏈路包括低噪放、接收本振、下變頻、AGC、ADC及數字接收機;發射鏈路包括數字基帶、本振、上變頻、放大器幾部分。如圖1所示:

圖1 射頻無線通信系統框圖

射頻通信系統之間最大區別之一在于射頻收發前端和數字中頻/基帶處理模塊的接口信號頻率不同,根據頻率范圍的不同,可劃分為三種:零中頻、普通中頻和高中頻方案。下面就各種方案逐一進行分析:

2.1 零中頻方案

以接收鏈路為例,零中頻方案如圖2所示。天線之后的接收信號經低噪放放大之后,與正交的兩路本振信號進行相乘產生兩路正交的基帶信號,本振信號可以等于載波頻率或僅與載波頻率相差一個很小的頻差(如1MHz以內)。經過后續AGC及濾波之后,由兩片AD芯片對IQ兩路信號進行模數轉換,并送至后續的數字模塊進行處理。

圖2 零中頻方案

2.2 普通中頻方案

普通中頻方案如圖3所示。本振和接收的信號間有一定的頻率差,比較常用的有70MHz,從而混頻后的數據帶有一定的中頻載波信號。信號經過后續的處理及模數轉換后,在數字模塊中利用數字IQ分離。

圖3 普通中頻方案

2.3 高中頻方案

高中頻的方案可以參考普通中頻的方案,區別在于本振和接收的信號間頻率差較高,比較常用的有180MHz或者更高中頻。

2.4 方案比較

以上三種方案各具優缺點,如表1所示:

表1 三種方案優缺點比較

從系統復雜程度來講,由于高中頻方案可以收發公用本振,并只有一個混頻通道,最為簡潔;零中頻方案需要兩個混頻通道、本振和AD,最為復雜;普通中頻介于兩者之間。而從靈活性和實現難易程度來看,零中頻對濾波器的帶寬、Q值,AD帶寬及采樣率的要求都較低,采樣時鐘選擇方便,無需與本振相干,不存在中頻中心頻點選擇問題,實現起來具有很高的靈活性和自由度。

ADI推出的AD936系列采用了零中頻的方案,集成了模擬濾波、混頻器、數據轉換器、發射和接收通道的頻率合成器以及包括可編程增益、直流偏置校準等數字域的其他功能,可實現射頻信號到零中頻的頻譜搬移,具備出色的靈活性和可配置性。下面我們將利用AD9361+FPGA的硬件框架,實現全雙工射頻收發系統。

3 方案設計

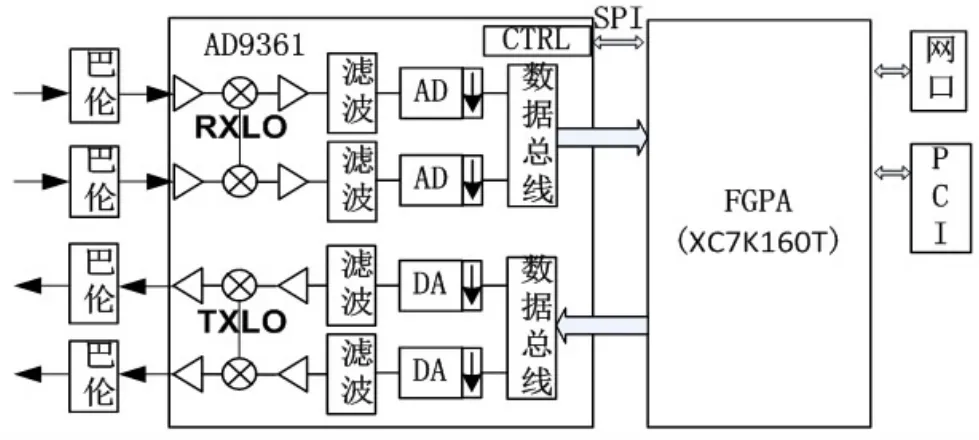

整個射頻收發系統基于軟件無線電技術,采用AD9361+ FPGA的硬件框架,搭配簡單外圍接口電路及供電模塊,在AD9361完成對射頻信號的頻譜搬移和數模模數轉換。在FPGA中實現數據的調制解調功能。FPGA選擇了XILINX公司K7系列的XC7K160T,該芯片可匹配AD9361的接口電路,而且具有豐富的內部資源和多種常用的對外接口。系統硬件框圖如圖4所示:

圖4 射頻系統硬件框圖

AD9361集成了射頻收發前端的所有功能以及ADC和DAC模塊,可實現兩路射頻信號的收發。接收時,前端的射頻信號經過巴倫轉化為差分信號后輸入給AD9361,在AD9361實現射頻信號的放大、混頻和濾波,將輸入的射頻信號搬移到零中頻(可設置一定的小頻率差),經過ADC的模數轉換后通過數字接口傳輸給FPGA,完成后續的數字處理。發射時,FPGA將IQ兩路的數據發送給AD9361,在AD9361中實現數模轉換以及濾波、放大、混頻等功能,最后通過巴倫將差分信號轉為單端輸出。

FPGA通過SPI接口通過對AD9361中的寄存器的讀寫實現對AD9361的配置,AD9361作為一款寬幅的射頻捷變頻收發器,具備70MHz~6GHz的可調頻率范圍,還有200kHz~ 56MHz的通道帶寬,以及可編程的濾波器,而且所有的配置只需要修改FPGA中的配置程序即可完成。

基于軟件無線電技術,AD9361作為射頻收發前端,實現了射頻信號從射頻到基帶數字信號的轉換,在FPGA中可對模數轉化后的數字數據進行后續處理,通過調用不同的調制解調模塊,即可實現不同碼速率、不同帶寬、不同調制方式的信號的調制解調,例如比較常用的BPSK,QPSK,FSK,MSK等調制方式。由于A9361和FPGA都具有可修改性,整個射頻收發系統具有很強的可配置性和靈活性。

4 結語

本文對基于軟件無線電技術的射頻通信系統的原理進行了研究,并分析了實現幾種方案集成化的優缺點,并基于AD936X+FPGA硬件框架搭建了射頻收發系統,這種具有很強靈活性的射頻收發系統,可適用于各種場景和領域中,具有廣闊的應用前景。

[1]楊小牛,樓才義.軟件無線電原理與應用[M].北京:電子工業出版社,2001.

[2]韓剛,張睿,李建東.軟件無線電接收機的一種實用結構[J].西安電子科技大學學報,2001,28(4):538-542.

[3]田耘.無線通信FPGA設計[M].北京:電子工業出版社,2008.

[4]邵善友,楊家瑋.軟件無線電發射機的FPGA實現[J].電訊技術,2005,45(4):124-128.

Design and Implementation of a FullDuplex RFTransceiver System

Xie Zuoquan Kang Chao Wang Yu

(ShanghaiAerospace Electronic Technology Research Institute,Shanghai201100)

With the progressof communication technology,RFw ireless communication technology hasmade the rapid development.Wireless communication technology hasbecomemoreandmoremature and stable.Universalandminiaturization of RF transceiver system have become the important development directions.In this paper,the principle of RF transceiver based on Software Defined Radio technology is introduced,several common schemes are analyzed,and the advantages and disadvantages of them iniaturization and integration of each schemeare compared.Finally an integrated radio frequency(RF)Agile transceivermade by ADIis used to construct thehardware platform and realizea simple fullduplex RF transceiversystem.

RF communication;fullduplex;SDR;FPGA

TN838;TN851

A

1008-6609(2017)06-0031-03

謝作全(1986-),男,浙江溫州人,碩士研究生,工程師,研究方向為遙測通信系統。