針對(duì)FPGA的IDL—Verilog編譯器的設(shè)計(jì)與實(shí)現(xiàn)

吳湛+王玲+吳宇

摘 要: 軟件通信體系結(jié)構(gòu)規(guī)范(SCA)規(guī)定采用CORBA中間件來實(shí)現(xiàn)運(yùn)行在不同處理器上的波形組件之間的相互通信,然而目前缺少能夠有效支持FPGA上CORBA 中間件的IDL編譯器。為此設(shè)計(jì)實(shí)現(xiàn)了一種IDL?Verilog編譯器,該編譯器能夠支持用戶自定義的任意IDL文件,并根據(jù)FPGA波形組件功能需要,自動(dòng)生成運(yùn)行在FPGA上的ORB核心、FPGA組件框架代碼,從而真正實(shí)現(xiàn)FPGA組件與GPP組件的統(tǒng)一CORBA通信。介紹IDL?Verilog編譯器的整體結(jié)構(gòu),并對(duì)該編譯器的設(shè)計(jì)與實(shí)現(xiàn)進(jìn)行詳細(xì)闡述,最后對(duì)編譯器進(jìn)行測(cè)試。結(jié)果表明,該編譯器能夠正確解析IDL文件,并實(shí)現(xiàn)從IDL到Verilog語言的映射,自動(dòng)生成的一系列目標(biāo)文件使FPGA真正具備CORBA通信能力。

關(guān)鍵詞: 軟件通信體系結(jié)構(gòu); CORBA; FPGA; IDL編譯器

中圖分類號(hào): TN915?34; TP314 文獻(xiàn)標(biāo)識(shí)碼: A 文章編號(hào): 1004?373X(2017)14?0018?05

Abstract: The software communications architecture (SCA) norm stipulates that the CORBA middleware should be used to realize intercommunication between the waveform components running in the different processors, but there is no IDL compiler which can support the CORBA middleware on FPGA effectively. Therefore, an IDL?Verilog compiler was designed, which can support any IDL files defined by users themselves, and generate the ORB core and FPGA component framework code running on FPGA automatically according to the functional requirements of FPGA components, so as to realize the CORBA communication between FPGA components and GPP components. The whole structure of IDL?Verilog compiler is introduced. The design and implementation of the compiler are expounded in detail. Some tests for the compiler were carried out. The results show that the IDL?Verilog compiler can parse the IDL files correctly, implement the mapping from IDL to Verilog language, and generate the target files automatically to make FPGA really have the ability of CORBA communication.

Keywords: software communication architecture; CORBA; FPGA; IDL compiler

0 引 言

軟件無線電(Software Defined Radio,SDR)是一種基于通用硬件平臺(tái)依靠軟件實(shí)現(xiàn)其功能的無線電通信技術(shù),其體系結(jié)構(gòu)是通過軟件通信體系架構(gòu)(Software Communication Architecture,SCA)來定義的[1?2]。SCA采用CORBA中間件來實(shí)現(xiàn)其所需的分布式計(jì)算環(huán)境[3?4],其硬件平臺(tái)通常包含通用處理器(GPP)、數(shù)字信號(hào)處理器(DSP)、可編程門陣列(FPGA)等。雖然CORBA(公共對(duì)象請(qǐng)求代理體系結(jié)構(gòu))中間件技術(shù)在GPP上已經(jīng)廣泛應(yīng)用,但在DSP,F(xiàn)PGA等專用處理器上實(shí)現(xiàn)起來較為困難,目前只有OIS公司開發(fā)的ORBexpress FPGA[5]和Prismtech公司開發(fā)的集成電路ORB(ICO)[6]實(shí)現(xiàn)了FPGA上的CORBA通信,但考慮到國(guó)防安全問題,不允許在我國(guó)軍事領(lǐng)域中使用[7]。基于以上考慮,為了實(shí)現(xiàn)FPGA上的CORBA通信,研發(fā)了支持FPGA處理器的CORBA中間件產(chǎn)品FPGA?ORB。

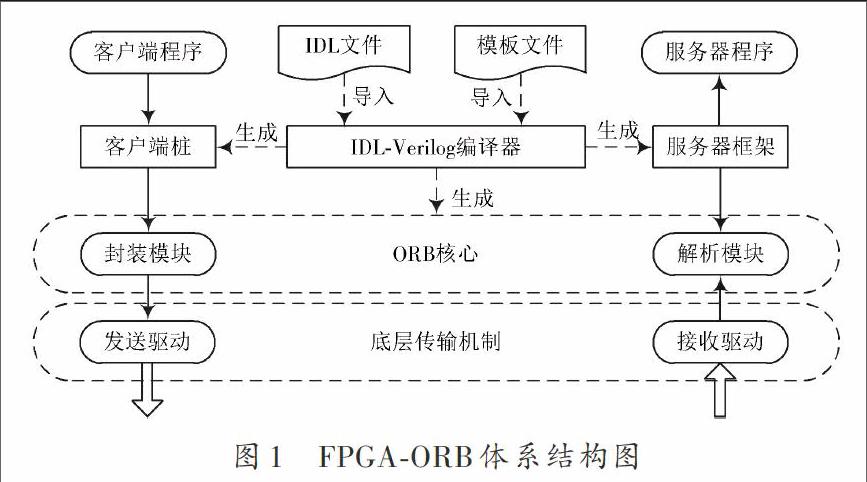

FPGA?ORB中間件主要包括運(yùn)行在FPGA處理器上的ORB核心、客戶端樁和服務(wù)器框架以及運(yùn)行在PC機(jī)上的IDL?Verilog編譯器,其體系結(jié)構(gòu)如圖1所示。其中,ORB核心用于實(shí)現(xiàn)客戶端請(qǐng)求和服務(wù)器對(duì)象之間的連接,客戶端的ORB核心接收被調(diào)用操作的參數(shù)并將其組碼為網(wǎng)絡(luò)可接收的格式,服務(wù)器的ORB核心將來自網(wǎng)絡(luò)的操作參數(shù)解組,然后送給服務(wù)器來執(zhí)行所調(diào)用的操作。客戶端樁用于將客戶端的請(qǐng)求編碼,通過客戶端的ORB發(fā)送到服務(wù)器,并把返回的結(jié)果解碼后送給客戶端。服務(wù)器框架負(fù)責(zé)把客戶端通過ORB發(fā)過來的請(qǐng)求解碼,通過對(duì)象操作實(shí)現(xiàn),然后把結(jié)果編碼后通過服務(wù)器ORB發(fā)送給客戶端。客戶端調(diào)用的接口和服務(wù)器實(shí)現(xiàn)的接口是通過接口描述語言(Interface Definition Language,IDL)來定義的,但是與某一種具體編程語言不同,IDL 是一種純說明性語言,它只能夠給出該接口的定義和每個(gè)操作要求的參數(shù)而不牽涉到具體的實(shí)現(xiàn)[8?9],因此要用IDL?Verilog編譯器對(duì)IDL文件進(jìn)行編譯,然后根據(jù)解析得到的IDL文件信息修改模板文件代碼,最后生成Verilog語言實(shí)現(xiàn)的ORB核心、客戶端樁和服務(wù)器框架。可見,IDL?Verilog編譯器是FPGA?ORB的關(guān)鍵模塊,本文主要論述IDL?Verilog編譯器的設(shè)計(jì)與實(shí)現(xiàn)。

1 IDL?Verilog編譯器的設(shè)計(jì)與實(shí)現(xiàn)

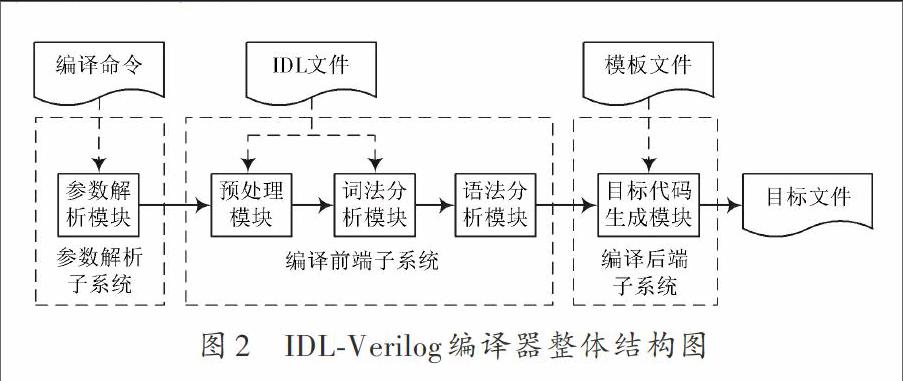

本文設(shè)計(jì)的IDL?Verilog編譯器劃分為三個(gè)子系統(tǒng):參數(shù)解析子系統(tǒng)、編譯前端子系統(tǒng)、編譯后端子系統(tǒng),其具體結(jié)構(gòu)如圖2所示。其中,參數(shù)解析子系統(tǒng)用于完成對(duì)用戶編譯命令的解析,存儲(chǔ)編譯器控制信息;編譯前端子系統(tǒng)用于完成對(duì)輸入IDL文件的解析,并生成一棵抽象語法樹;編譯器后端子系統(tǒng)用于完成對(duì)編譯前端子系統(tǒng)生成的抽象語法樹的遍歷,并提取相關(guān)信息完成對(duì)輸入模板文件的修改,然后生成目標(biāo)文件。這種設(shè)計(jì)方式帶來的好處是,可以保持參數(shù)解析子系統(tǒng)和編譯前端子系統(tǒng)的代碼不變,僅僅通過改變編譯后端子系統(tǒng)的代碼就可以實(shí)現(xiàn)針對(duì)不同處理器和開發(fā)語言的IDL編譯器,這樣就大大增強(qiáng)了IDL編譯器的通用性。下面分別對(duì)三個(gè)子系統(tǒng)進(jìn)行詳細(xì)的闡述。

1.1 參數(shù)解析子系統(tǒng)

參數(shù)解析子系統(tǒng)的作用是通過解析處理用戶輸入的命令參數(shù)以獲取控制命令信息來實(shí)現(xiàn)對(duì)編譯器的控制。文中設(shè)計(jì)的IDL?Verilog編譯器需要輸入的命令參數(shù)包括:源文件名、包含文件路徑、輸出目標(biāo)代碼文件路徑、模板文件路徑、參數(shù)傳遞文件路徑以及幫助查詢命令。

1.2 編譯前端子系統(tǒng)

編譯器前端子系統(tǒng)主要由預(yù)處理模塊、詞法分析模塊和語法分析模塊組成。下面分別對(duì)三個(gè)模塊進(jìn)行詳細(xì)的闡述。

1.2.1 預(yù)處理模塊

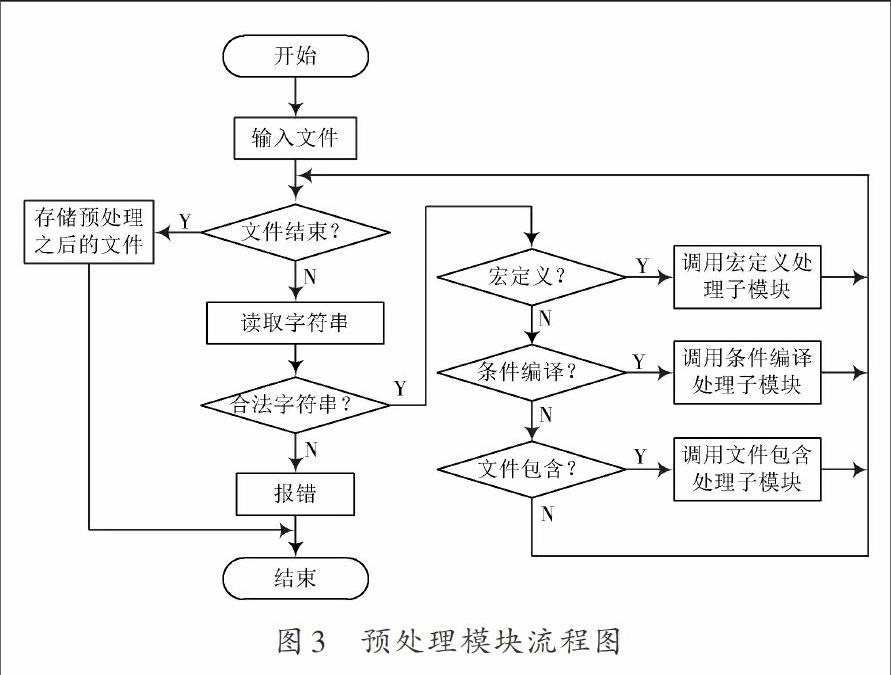

預(yù)處理模塊的主要作用是對(duì)輸入的IDL文件進(jìn)行預(yù)處理,以方便詞法分析模塊、語法分析模塊進(jìn)行后續(xù)處理。其主要功能子模塊包括:源文件包含處理子模塊、宏定義處理子模塊和條件編譯處理子模塊。

(1) 源文件包含處理子模塊。源文件包含處理子模塊用來對(duì)源文件當(dāng)中的“#include”語句進(jìn)行解析,提取輸入源文件中的包含文件;然后以包含文件的絕對(duì)路徑作為輸入文件遞歸調(diào)用預(yù)處理模塊;最后按由外向內(nèi)和由前向后的原則存儲(chǔ)包含文件的絕對(duì)路徑。IDL?Verilog編譯器將按照存儲(chǔ)的包含文件的絕對(duì)路徑的先后順序?qū)ο嚓P(guān)文件逐一進(jìn)行解析處理。

(2) 宏定義處理子模塊。宏定義處理子模塊用來對(duì)源文件和包含文件當(dāng)中的“#define”語句進(jìn)行解析,將宏定義中的宏名存儲(chǔ),用于預(yù)處理模塊當(dāng)中條件編譯的判斷處理,而并不進(jìn)行宏定義替換。在語法解析模塊中,則會(huì)提取完整的宏定義信息,然后將基本數(shù)據(jù)類型的標(biāo)識(shí)符和已存儲(chǔ)的有效宏名進(jìn)行匹配,如果匹配成功,則將該標(biāo)識(shí)符替換為宏定義的字符串。

(3) 條件編譯處理子模塊。條件編譯處理子模塊用來對(duì)源文件和包含文件當(dāng)中的“#ifdef”,“#if defined”等語句進(jìn)行解析,具體方法就是將參數(shù)解析模塊存儲(chǔ)的預(yù)定義變量名和預(yù)處理模塊存儲(chǔ)的宏名作為依據(jù),對(duì)條件編譯語句進(jìn)行判斷,找出需要編譯的語句。

為了確保源文件和包含文件內(nèi)容的不變性,預(yù)處理模塊為每個(gè)源文件和包含文件都新建一個(gè)與之對(duì)應(yīng)的臨時(shí)文件。將預(yù)處理之后的源文件和包含文件存入與之對(duì)應(yīng)的臨時(shí)文件。詞法分析模塊、語法分析模塊對(duì)源文件和包含文件的后續(xù)處理就轉(zhuǎn)化為對(duì)臨時(shí)文件的解析。當(dāng)所有解析處理結(jié)束之后,IDL?Verilog編譯器會(huì)刪除預(yù)處理模塊生成的臨時(shí)文件。

預(yù)處理模塊具體執(zhí)行流程圖如圖3所示。

1.2.2 詞法分析模塊

詞法分析模塊是 IDL?Verilog 編譯器前端子系統(tǒng)的關(guān)鍵模塊之一。該模塊按從左往右的順序?qū)υ次募M(jìn)行掃描,在掃描的過程中會(huì)跳過空格和換行符并刪除注釋,將若干連續(xù)字符拼接成一個(gè)符合IDL語言的構(gòu)詞規(guī)則的標(biāo)識(shí)符并提取,然后將提取的標(biāo)識(shí)符交給語法分析模塊進(jìn)行后續(xù)處理,其具體過程如圖4所示。

1.2.3 語法分析模塊

語法分析模塊采用“邊檢查、邊存儲(chǔ)、邊轉(zhuǎn)換”的方式來對(duì)輸入文件進(jìn)行語法解析:每當(dāng)語法分析模塊從輸入文件中檢查到一種語法成分時(shí),則調(diào)用相對(duì)應(yīng)的語法解析函數(shù)對(duì)該語法成分進(jìn)行解析;接著按照IDL語言的語法規(guī)則來對(duì)語法成分進(jìn)行解析和檢查,并在解析和檢查過程中,將該語法成分的信息存儲(chǔ);將Verilog語言不支持的函數(shù)參數(shù)類型轉(zhuǎn)換為基本數(shù)據(jù)類型,當(dāng)函數(shù)參數(shù)類型為結(jié)構(gòu)體時(shí),則將其按結(jié)構(gòu)體成員的數(shù)量拆分為基本數(shù)據(jù)類型,當(dāng)函數(shù)參數(shù)類型為別名時(shí),則將其與存儲(chǔ)的別名信息對(duì)比,找出其原始基本數(shù)據(jù)類型。其具體執(zhí)行流程圖如圖5所示。最終,一個(gè)IDL文件經(jīng)預(yù)處理模塊、詞法分析模塊和語法分析模塊會(huì)生成一棵抽象語法樹,該抽象語法樹存儲(chǔ)了完整的IDL文件信息[10]。每棵抽象語法樹可能包含十棵子樹,這十棵子樹分別存儲(chǔ):包含文件信息、宏定義信息、常量信息、結(jié)構(gòu)體信息、別名信息、異常信息、枚舉信息、聯(lián)合信息、接口信息、模塊信息。

語法分析流程如下:

(1) 判斷文件是否結(jié)束,如果是則執(zhí)行第(6)步,否則繼續(xù)執(zhí)行第(2)步。

(2) 從文件中讀取一個(gè)字符串。

(3) 判斷該字符串是否為合法字符串,如果為合法字符串,則執(zhí)行第(4)步,否則執(zhí)行第(5)步。

(4) 判斷字符串,如果字符串為函數(shù),則調(diào)用函數(shù)解析接口進(jìn)行函數(shù)信息提取和存儲(chǔ),并將函數(shù)參數(shù)的數(shù)據(jù)類型轉(zhuǎn)換為基本數(shù)據(jù)類型存儲(chǔ),然后返回第(1)步繼續(xù)執(zhí)行;如果字符串為文件包含、屬性、異常和用戶定義的數(shù)據(jù)類型(宏定義、別名、常量、結(jié)構(gòu)、枚舉、聯(lián)合),則調(diào)用相應(yīng)的解析函數(shù),完成相應(yīng)信息的提取和存儲(chǔ),然后返回第(1)步繼續(xù)執(zhí)行;如果字符串為接口,則提取接口名和繼承接口信息并存儲(chǔ),然后返回第(1)步繼續(xù)執(zhí)行;如果字符串為模塊,則提取并存儲(chǔ)模塊名,然后返回第(1)步繼續(xù)執(zhí)行;如果字符串不是上面提到的任一字符串,則返回第(1)步繼續(xù)執(zhí)行。

(5) 報(bào)告錯(cuò)誤文件名字、錯(cuò)誤行數(shù)和錯(cuò)誤類型。

(6) 結(jié)束。

1.3 編譯后端子系統(tǒng)

編譯后端子系統(tǒng)主要包括目標(biāo)代碼生成模塊。目標(biāo)代碼生成模塊是IDL?Verilog編譯器最后一個(gè)關(guān)鍵模塊。這一模塊的主要作用是通過遍歷語法分析模塊生成的抽象語法樹來提取接口信息,然后根據(jù)提取的信息完成對(duì)模板文件的修改來生成目標(biāo)文件。

為了方便生成目標(biāo)代碼,本文為每一個(gè)需要更改的FPGA?ORB模板文件內(nèi)容都做了注釋標(biāo)記,目標(biāo)文件生成函數(shù)會(huì)從抽象語法樹中提取相應(yīng)信息對(duì)模板文件中的標(biāo)記內(nèi)容進(jìn)行修改,并生成目標(biāo)文件,這樣就大大減少了目標(biāo)代碼生成模塊的工作量。生成的目標(biāo)文件按功能可以劃分為:ORB模塊、IOR解析模塊、選擇器模塊、客戶端樁模塊、服務(wù)器框架模塊、組件接口模塊,其結(jié)構(gòu)如圖6所示。

(1) ORB模塊。該模塊主要用于GIOP報(bào)文頭、請(qǐng)求報(bào)文頭、應(yīng)答報(bào)文頭的解析和封裝。

(2) IOR解析模塊。該模塊用于解析應(yīng)答報(bào)文中的對(duì)象引用(IOR),獲取相應(yīng)的對(duì)象密鑰(objectkey)。

(3) 選擇器模塊。該模塊為選擇器模塊,用于報(bào)文發(fā)送和接收選擇。

(4) 客戶端樁模塊。該模塊包含多個(gè)客戶端樁子模塊,其數(shù)量與組件端口數(shù)量相同,其主要作用是對(duì)請(qǐng)求報(bào)文中的函數(shù)參數(shù)進(jìn)行封裝以及對(duì)應(yīng)答報(bào)文中的函數(shù)參數(shù)進(jìn)行解析。

(5) 服務(wù)器框架模塊。該模塊包含多個(gè)服務(wù)器框架模子模塊,其數(shù)量與組件端口數(shù)量相同,其主要作用是對(duì)請(qǐng)求報(bào)文中的函數(shù)參數(shù)進(jìn)行解析以及對(duì)應(yīng)答報(bào)文中的函數(shù)參數(shù)進(jìn)行封裝。

(6) 組件接口模塊。該模塊采用硬件抽象層(HAL)的接口規(guī)范[11],其主要作用是實(shí)現(xiàn)FPGA組件端口和FPGA?ORB之間的數(shù)據(jù)傳遞。

2 IDL?Verilog編譯器測(cè)試

本文對(duì)IDL?Verilog編譯器的測(cè)試主要分為本地測(cè)試和CORBA通信測(cè)試兩個(gè)方面。

(1) IDL?Verilog編譯器本地測(cè)試。IDL?Verilog編譯器本地測(cè)試主要是測(cè)試IDL?Verilog編譯器對(duì)IDL文件的解析處理能力。因?yàn)檩斎氲腎DL文件是無法窮舉的,本文采用了等價(jià)類測(cè)試的方法來測(cè)試[12]。通過將輸入的文件中的語句劃分成能夠覆蓋IDL語法各種情況的等價(jià)類,并對(duì)每個(gè)等價(jià)類完成了測(cè)試。由于各等價(jià)類的測(cè)試步驟相同,本文僅選用了一個(gè)測(cè)試用例來介紹本地測(cè)試的過程。測(cè)試的IDL文件test.idl如圖7所示,該IDL文件經(jīng)IDL?Verilog編譯器編譯之后生成的目標(biāo)文件如表1所示。測(cè)試表明,IDL?Verilog編譯器能夠?qū)崿F(xiàn)對(duì)輸入IDL文件的正確解析,并成功生成目標(biāo)文件。

(2) CORBA通信測(cè)試。CORBA通信測(cè)試主要是測(cè)試表1中的目標(biāo)文件能否配合的FPGA?ORB實(shí)現(xiàn)FPGA上的CORBA通信。

立足于實(shí)驗(yàn)室的測(cè)試條件,搭建一個(gè)如圖8所示的測(cè)試平臺(tái)。該測(cè)試平臺(tái)主要由GPP和FPGA組成,其中,GPP主要用來運(yùn)行核心框架和GPP波形組件A,F(xiàn)PGA用來運(yùn)行FPGA波形組件B。GPP采用 TAO進(jìn)行CORBA通信,F(xiàn)PGA采用表1中目標(biāo)文件組成的FPGA?ORB進(jìn)行CORBA通信,GPP ORB與FPGA ORB之間實(shí)際通過ELBC總線相連。

測(cè)試平臺(tái)的通信過程如圖9所示,上電之后,F(xiàn)PGA組件B也能像GPP組件A一樣通過FPGA?ORB向核心框架中的域管理器進(jìn)行注冊(cè),然后域管理器對(duì)組件A進(jìn)行初始化、端口連接和參數(shù)配置以完成整個(gè)波形組件的初始化;最后組件A和組件B可以通過各自的中間件向?qū)Ψ桨l(fā)送函數(shù)調(diào)用請(qǐng)求,并返回調(diào)用結(jié)果。測(cè)試表明,IDL?Verilog編譯器生成的目標(biāo)文件成功地實(shí)現(xiàn)了FPGA與GPP之間的CORBA通信。

3 結(jié) 語

本文根據(jù)IDL語言的語法規(guī)則,使用C語言實(shí)現(xiàn)了IDL?Verilog編譯器。該編譯器采用模塊化的設(shè)計(jì)方法,將整個(gè)編譯器按功能劃分為不同的子模塊,可以通過改變其子模塊實(shí)現(xiàn)不同的語言映射,大大提高了IDL編譯器的通用性。同時(shí)該編譯器生成的目標(biāo)文件能夠正確完成IDL語言到Verilog語言的映射。IDL?Verilog編譯器目前已經(jīng)調(diào)試通過,并作為FPGA?ORB重要組成部分實(shí)現(xiàn)了FPGA上CORBA通信。

參考文獻(xiàn)

[1] JOHNSON C R, Jr, SETHARES W A.軟件無線電[M].北京:機(jī)械工業(yè)出版社,2008.

[2] 粟欣,許希斌.軟件無線電原理與技術(shù)[M].北京:人民郵電出版社,2010.

[3] 崔小鵬,胡中豫,張豪.SCA中CORBA與硬件抽象層技術(shù)研究[J].現(xiàn)代電子技術(shù),2011,34(6):32?35.

[4] 李雅萍,楊尚森,李陽.CORBA技術(shù)在SCA系統(tǒng)中的應(yīng)用[J].計(jì)算機(jī)工程與設(shè)計(jì),2008,29(16):4200?4203.

[5] BECKWITH W, DELLER S, GTHOMPSON J. Hardware communications infrastructure supporting location transparency and dynamic partial reconfiguration: US 2008/0229326 A1 [P]. 2008?09?18.

[6] Prismtech. Prismtech openfusion CORBA products [EB/OL]. [2013?12?10]. http://www.prismtech.com/sectionitem.

[7] 高宏偉.SCA系統(tǒng)中針對(duì)FPGA處理器的中間件關(guān)鍵技術(shù)研究與實(shí)現(xiàn)[D].長(zhǎng)沙:國(guó)防科技大學(xué),2011.

[8] HENNING Michi, VINOSKI Steve.基于C++ CORBA高級(jí)編程[M].北京:清華大學(xué)出版社,2007.

[9] 韋樂平.CORBA語言映射[M].北京:電子工業(yè)出版社,2001.

[10] AHO A V.編譯原理[M].北京:機(jī)械工業(yè)出版社,2009.

[11] 王金波.基于SCA的硬件抽象層連接設(shè)計(jì)及其在DSP/FPGA上的實(shí)現(xiàn)[D].長(zhǎng)沙:國(guó)防科技大學(xué),2005.

[12] 李穎,胡明.基于C語言實(shí)現(xiàn)的IDL編譯器[J].計(jì)算機(jī)技術(shù)與發(fā)展,2013,23(3):5?9.