Virtex5 FPGA GTP_DUAL硬核兩個收發器獨立使用的實現

呂波+張涌+石永彪+黃侃

摘 要: 在Xilinx的Virtex5系列FPGA中,基于高速串行通信技術的GTP_DUAL硬核包含了兩個收發器,而Xilinx提供的Aurora IP軟核代碼如果只例化一個通道,將占用整個硬核資源,造成另外一個通道不能再被使用,致使FPGA資源利用率降低。通過對Aurora IP軟核代碼分析,在GTP封裝代碼中對未使用的通道添加和修改相應信號,并追加時鐘模塊、發送模塊和接收模塊等,實現了一個GTP_DUAL中兩個收發器的獨立使用,從而提高了FPGA資源利用率,降低了開發成本。該方案已在某重大軍工項目中得到了應用。

關鍵詞: Virtex5 FPGA; GTP硬核; 串行通信; 收發器; Aurora協議

中圖分類號: TN911?34; TN79+1 文獻標識碼: A 文章編號: 1004?373X(2017)14?0124?04

Abstract: In Xilinx Virtex5 FPGA, the GTP_DUAL hardcore based on high?speed serial communication technology (Rocket IO) contains two transceivers. When the Aurora IP code provided by Xilinx is instantiated with a single channel, it will occupy the whole hardcore resources, and make the other channel no longer used and the utilization of FPGA resources reduced. Based on analysis of the Aurora IP code, some corresponding signals are added and modified in the unused channel in the GTP packaging code, and then clock module, sending module, receiving module and so on are added for independent application of the two transceivers in GTP_DUAL hardcore, utilization improvement of FPGA resources and reduction of development cost. The scheme has been applied to a major military defense project.

Keywords: Virtex5 FPGA; GTP hardcore; serial communication; transceiver; Aurora protocol

0 引 言

由于傳統的并行I/O技術走線多、PCB布線難、信號間串擾大等缺陷而無法突破自身的速度瓶頸,正在被擁有更高傳輸速率且只需少量信號線的高速串行技術所取代[1]。Xilinx公司為使其FPGA芯片與串行傳輸技術更好地結合以滿足市場需求,在Virtex系列FPGA中,集成了基于高速串行通信技術硬核(Rocket I/O)的多個GTP或GTX收發器模塊,并在此硬核基礎上開發了一款可自由使用且相對簡便的點對點鏈路層Aurora協議[2] ,該協議支持的通信碼率高達3.75 Gb/s。

在Virtex5平臺上,原來的GTP收發器被集成了兩個GTP收發器通道的GTP_DUAL所取代,其優點在于兩個收發器共享一些資源,減少了資源占用面積和功耗。然而,在Aurora工程中,由于例化單通道時占用了整個硬核資源而導致另外一個GTP通道不能再被使用,使GTP_DUAL的利用率大大降低。比如,筆者所在研究室參與研發的某重大軍工項目,其中對于紅外分系統設備中的視頻接口板,首先從紅外成像儀接收紅外圖像數據,并通過GTP收發器通道分別向一塊綜合處理板和四塊信號處理板發送圖像數據進行處理,最后將處理后的圖像數據輸出到視頻顯示設備上顯示,這樣一塊視頻接口板至少需要7個GTP收發器通道。結合當前使用的FPGA芯片,內嵌4個GTP_DUAL,雖然含有8個GTP收發器通道,但由于不能單獨使用,最多只能連接四塊電路板。所以一般來講,需要進行追加芯片數量,或者使用包含更多GTP_DUAL收發器通道的芯片,這無疑增加了開發成本和系統開發難度。

為此,本文針對上述缺陷,在Virtex5硬核和Aurora協議的基礎上,提出一種改進方案。通過對Xilinx提供的Aurora IP軟核代碼進行修改,使兩個GTP收發器能夠獨立使用并可以傳輸不同的協議數據,以提高FPGA資源利用率和降低系統成本。目前,該改進方案已經應用到了一些重大工程項目中。

1 GTP_DUAL硬核模塊

GTP_DUAL高速串行硬核在發送端將時鐘與數據合并傳輸,在接收端提取時鐘和數據,解決了并行傳輸帶來的時鐘抖動和偏斜的問題,提高了數據傳輸速率,發揮了FPGA邏輯配置靈活和片內互聯電磁性能優異的特點,實現了高性能、低成本的設計[3]。

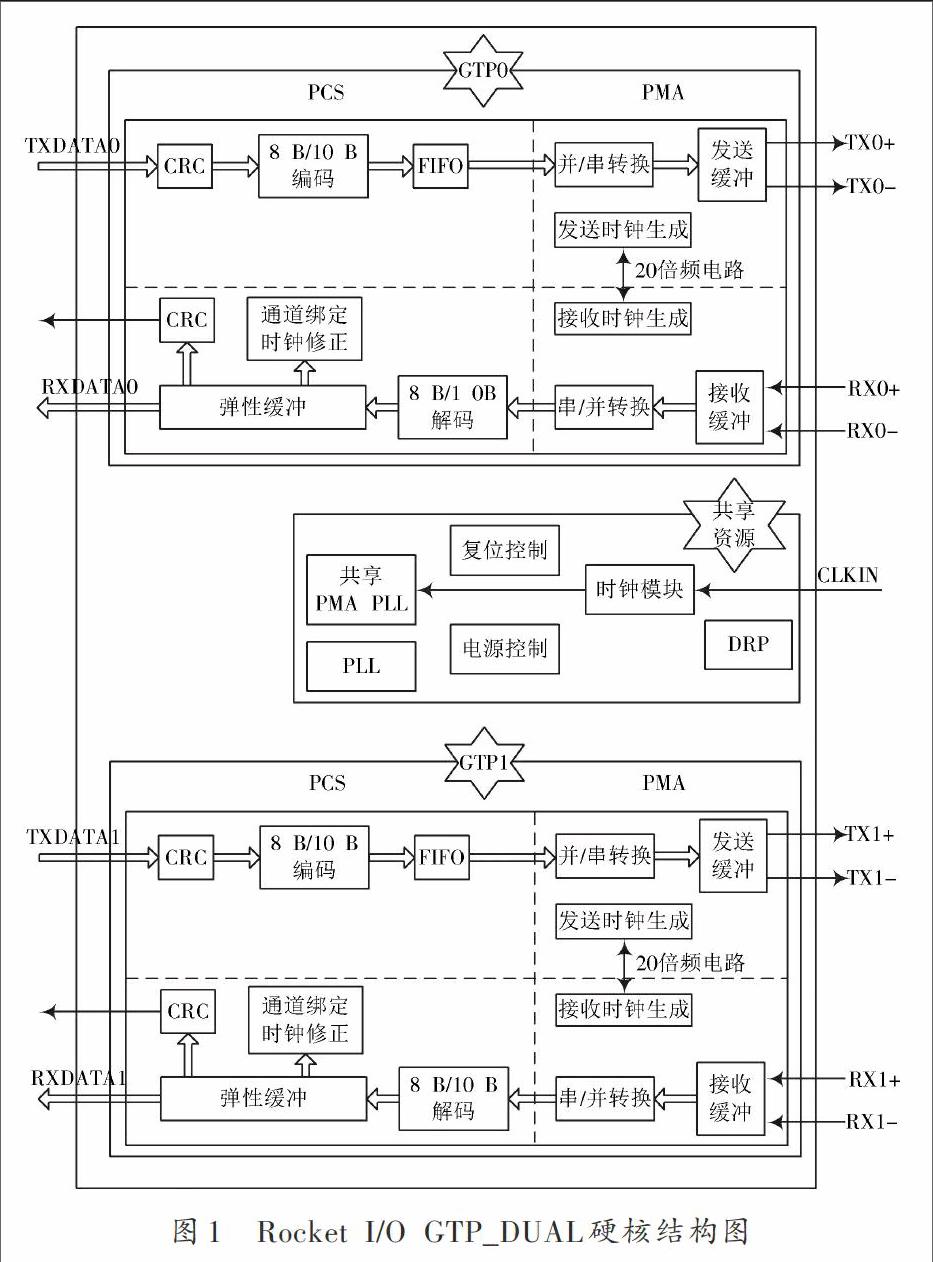

在Virtex5系列FPGA中,一個GTP_DUAL硬核結構圖如圖1所示[4]。

兩個GTP收發器GTP0和GTP1分別具有各自獨立的發送模塊和接收模塊,并且共享包括PLL、高速串行時鐘、復位控制和電源控制等重要資源,不占用FPGA其他邏輯與片上存儲資源,從而減少了資源占用的面積和功耗[5]。

每個收發器由物理媒質適配層(PMA)和物理編碼子層(PCS)兩部分組成[6]。從應用上講,GTP_DUAL硬核處于數據傳輸協議的物理層,實現最基本的數據通信。其工作過程為,在發送端按照一定的計算規則產生CRC校驗碼并插入到預發送的并行數據中,經過8 B/10 B編碼寫入發送FIFO,最后通過并/串轉換器將其轉換成差分數據發送出去。在接收端將接收的串行差分數據首先恢復出用于串并轉換的時鐘信號,并在comma檢測和對齊模塊的作用下,將數據進行對齊和串/并轉換,最后將轉換后的并行數據經過8 B/10 B解碼和CRC模塊校驗并行輸出[7]。

2 Aurora IP核雙收發器獨立使用

2.1 Aurora協議及其IP核

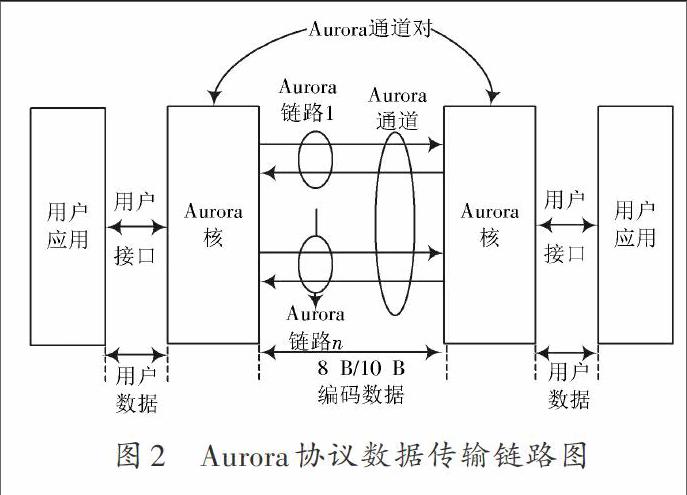

Aurora協議是一個開放、免費的鏈路層協議,可為私有上層協議或標準上層協議提供透明接口的串行互聯協議,可用來進行點到點的串行數據傳輸,具有傳輸數據高效和簡單易用的特點,為系統設計人員提供了所需要的靈活性[8]。

Aurora IP核是在Aurora協議和高速串行收發器GTP_DUAL硬核基礎上研發出來的。該IP核包含了GTP_DUAL模塊,且提供了簡單的用戶接口,極大地方便了信號的可操作性[9]。通過使用Aurora IP核,用戶不必對復雜的GTP_DUAL硬核部分進行操作,而只要處理好與Aurora IP核的用戶接口即可。如圖2所示,Aurora IP核可以方便地實現器件間的單通道通信或多通道綁定通信。

在實際應用中,可能需要GTP0和GTP1傳輸不同的數據,但在當前Xilinx實現中,例化一個GTP通道的Aurora IP核后,再例化另外一個,則綜合布線時會提示GTP_DUAL硬核資源已被使用而不能通過。所以本文通過生成一個單通道的參考用Aurora IP核實例,并修改相關代碼以達到兩個收發器能獨立使用且傳輸不同數據的目的。

2.2 Aurora IP核實例結構

為了便于說明實現過程,本文通過Xilinx公司開發的軟件工具CORE Generator 14.4,生成Aurora IP核的一個實例作為基礎[10],并將參數設置為全雙工模式、單通道、線速度為1.25 Gb/s,輸入參考時鐘為100 MHz,用戶時鐘62.5 MHz,發送和接收位寬都為16 b,采用幀模式的數據傳輸,所選通道為GTP_DUAL_X0Y4的GT0。其硬件設計工具ISE 14.4的實例層次結構如圖3所示。

實例TOP層下面有6個模塊,分別為clock_module,standard_cc_module,reset_logic,frame_gen,frame_check和aurora_module。其中前3個模塊用于提供時鐘、時鐘補償和復位等功能,frame_gen模塊用于數據發送,frame_check用于數據接收,這5個模塊都屬于應用層,用戶可以根據實際情況進行修改。aurora_module模塊為物理層和鏈路層,實現GTP_DUAL硬核雙收發器的功能,也是整個邏輯程序的核心部分,一般不允許用戶修改。

2.3 Aurora IP核實例修改

由第2.2節可知,aurora_module模塊實現的是GTP_DUAL硬核模塊功能,是整個邏輯程序的關鍵,其一個GTP收發器邏輯結構如圖4所示。aurora_module模塊包括了5個部分,分別為TX LocalLink,RX LocalLink,Aurora_Lane,Global_Logic和GTP_Wrapper。其中,TX LocalLink模塊的功能是通過LocalLink鏈路接口將用戶數據轉化為Aurora 8 B/10 B數據,然后送入Lane;RX LocalLink模塊的功能是通過Lane將接收到的數據轉化為LocalLink鏈路數據,并發送給用戶接口;Aurora_Lane模塊的功能是一個GTP收發器傳輸通道的連接,包括Lane初始化、特殊字符的產生、錯誤檢測譯碼等;Global_Logic模塊功能包括通道綁定、通道識別、通道錯誤管理和Idle空字符生成等;GTP_Wrapper模塊封裝了GTP_DUAL兩個收發器的硬核功能模塊,Xilinx只提供了該硬核的接口,具體實現邏輯屬于Xilinx的商業機密。

由于生成實例時系統參數選擇為單通道,收發器選擇GTP0,所以在GTP_Wrapper模塊中,GTP0收發器的相關信號接口已被使用,而GTP1收發器的相關信號,有的信號被空置,有的信號與一個XX_unused的寄存器連接,有的信號被連接至tied_to_ground_i或者tied_to_vcc_i。因此,實現GTP_DUAL雙收發器的獨立使用,就必須將GTP1收發器的相關信號建立起來。

綜合以上分析,實現兩個收發器獨立使用必須同時將GTP0和GTP1兩個收發器從GTP_Wrapper模塊中連接出來,而TX LocalLink,RX LocalLink,Aurora_Lane和Global_Logic四個模塊是GTP_DUAL硬核與用戶接口之間的數據轉換過程,故將這4個模塊綁定形成一個大模塊,并例化兩個分別與兩個GTP收發器連接。最終實現GTP_DUAL硬核GTP雙收發器的aurora_module模塊結構框圖如圖5所示。

實例修改的具體實現過程如下:

(1) 修改GTP_Wrapper模塊。對GTP_Wrapper邏輯進行整理分析,把GTP0接口、GTP1接口和共享模塊接口各自的信號及其相關狀態和控制信號進行歸整,將GTP1模塊的相關信號參照GTP0模塊通過追加、修改、刪除等操作建立起來,并添加到輸入/輸出接口中。

(2) 添加aurora_transmission_unit模塊。該模塊由TX LocalLink,RX LocalLink,Aurora_Lane和Global_Logic四個子模塊組成,主要作用是作為用戶接口和一個GTP收發器的數據傳輸通道。

(3) 修改aurora_module模塊:該模塊由兩個aurora_transmission_unit模塊和一個GTP_Wrapper模塊組成,主要作用是將每個GTP收發器與其各自的數據傳輸通道連接起來。

(4) 修改用戶層reset_logic模塊。該模塊的主要目的是將板上的復位按鈕進行消抖,并把消抖后的復位等信號傳輸給各個GTP收發器。由于復位按鈕只有一個,所以在此模塊中添加一個復位信號,用于GTP1收發器。

(5) 修改TOP頂層模塊。TOP頂層模塊實現的是整個系統功能,所以每個GTP收發器獨立地與外界進行數據接收和發送,就需要配套的時鐘模塊clock_module、時鐘補償模塊standard_cc_module和用于數據接收和發送的用戶接口模塊frame_gen和frame_check。這四個模塊用戶可以根據自己實際需要進行修改。

通過以上步驟修改后的GTP_DUAL雙收發器獨立數據傳輸的結構如圖6所示。

2.4 系統測試

本測試系統以實驗室自行設計的兩塊信號處理板為測試平臺,其測試方案如圖7所示。通過兩根單纖雙向傳輸型光纖將GTP_DUAL_X0Y4的兩個GTP收發器連接起來,在全雙工模式下相互通信。在每一個傳輸通道中,兩邊各自在frame_gen程序中分別發送一定數據,并通過光纖傳輸,由frame_check程序接收后,并檢測數據,如果接收數據正確,則點亮一個LED燈,表示通信成功。

測試結果實物圖如圖8所示,由圖8可以看出兩個LED燈均已點亮,表示兩路光纖通信正常,程序的修改達到預期目標。圖9和圖10分別通過ChipScope[11]抓取兩塊信號處理板的數據信號。圖9是信號處理板1通過GTP0和GTP1發送的測試數據。圖10是信號處理板2通過GTP0和GTP1接收信號處理板1的測試數據。可見數據發送和接收都正常。

3 結 語

在實際工程中,經常需要傳輸多路高速數據,而Virtex5為了節省資源,將2個GTP收發器通過共享資源合并成1個GTP_DUAL,當所需通道多于GTP_DUAL個數時,一般需要升級芯片或追加芯片數量,增加了成本。另外,如果GTP_DUAL只使用一路GTP收發器,將造成另外一路不能被使用,這又導致資源浪費。針對這些情況,并根據GTP_DUAL硬核和Aurora協議相關知識,本文對Xilinx公司提供的Aurora IP核進行修改,以達到每個GTP收發器通道都能獨立傳輸數據。根據實驗結果以及在某軍工項目上的應用表明,本文實現的修改方法達到了提高FPGA資源利用率的目的,降低了系統開發的成本。

參考文獻

[1] 杜旭,于洋,黃建.基于FPGA的高速串行傳輸接口的設計與實現[J].計算機工程與應用,2007,43(12):94?96.

[2] 李維明,陳建軍,陳星锜.基于Aurora協議的高速通信技術的研究[J].電子技術應用,2013,39(12):37?40.

[3] 曾瀚,周國忠.多路高速光纖圖像傳輸系統設計及實現[J].半導體光電,2013,34(2):326?329.

[4] Xilinx Inc.Virtex5 FPGA RocketIO GTP transceiver user guide UG196(v2.1) [EB/OL]. [2012?12?03]. http://www.xilinx.com.

[5] 李大鵬,陳長勝,王世奎,等.基于FPGA的高速串行傳輸接口研究與實現[J].航空計算技術,2008,38(2):100?103.

[6] 李敏,徐建城,李鍵.基于Rocket I/O接口的高速互連應用研究與實現[J].現代電子技術,2012,35(6):11?14.

[7] 蘇秀妮,陳建春,那彥.基于RocketIO自定義傳輸協議在高速串行通信中的設計與實現[J].微電子學與計算機,2013,30(9):90?93.

[8] 張琳琳,張涌.Aurora協議在紅外告警系統中的應用[J].科學技術與工程,2012,12(21):5308?5311.

[9] 岳振,呂波,張涌,等.基于Aurora協議的高速圖像傳輸和通信平臺設計[J].電子技術應用,2014,40(8):7?9.

[10] Xilinx Inc. LogiCORE IP Aurora 8 B/10 B user guide UG353(v5.3) [EB/OL]. [2012?01?18]. http://www.xilinx.com.

[11] Xilinx Inc. ChipScope Pro tutorial: using an IBERT core with ChipScope Pro Analyzer UG811 (v13.1) [EB/OL]. [2014?04?28]. http://www.xilinx.com.