基于S5PV210的LCD轉VGA技術研究

馮莉

摘 要 以VGA接口時序為標準,采用ARM芯片S5PV210為CPU,通過D/A 芯片 SDA7123的信號轉換,實現了嵌入式系統領域LVDS轉VGA的方案設計。系統的實現,一方面通過配置S5PV210芯片的LCD控制器,使得LVDS接口產生數字信號,另一方面通過 D/A 芯片SDA7123將數字信號轉化為模擬信號,實現了VGA接口終端的正常視頻顯示。經驗證,該方案對于800×600、1024×768等不同分辨率的視頻信號,顯示效果良好,并具有占用系統資源少,效率高,可靠性好的優點,適合在嵌入式應用領域廣泛采用。

關鍵詞 VGA;S5PV210;時序;視頻D/A;LCD控制器;SDA7123

中圖分類號 TP3 文獻標識碼 A 文章編號 1674-6708(2017)188-0078-04

目前許多嵌入式微處理器都集成了LCD控制器,如Samsung公司的S5PV210、S3C6410及Atmel公司的ATSAMA5D3系列處理器等。雖然可以方便的接大屏幕的LCD顯示屏,但LCD顯示屏價格昂貴。而PC端的液晶顯示器,在日常生活中普遍存在,如果能夠合理利用此資源來作為顯示終端,不僅可以合理利用現有資源、節約系統成本而且體積小巧,便于攜帶。普通計算機的液晶顯示器大都采用VGA接口作為標準信號輸入接口,因此,本方案采用LVDS轉VGA的方案設計來滿足此要求。本方案通過分析VGA顯示時序和LCD顯示時序之間的關系,找到了問題的突破口,同時驗證了方案的可行性。

1 VGA 接口

VGA(Video Graphics Array)視頻圖形陣列是IBM于1987年提出的一個使用模擬信號的顯示標準。VGA接口共有15針,分成3排,每排5個孔,如圖1所示。

VGA接口信號為模擬信號,它傳輸的主要信號分為紅、綠、藍模擬信號以及行同步信號和場同步信號。其引腳定義如表 1所示。

2 VGA時序與LCD時序分析

VGA的時序分為行時序和場時序。行時序如圖2所示。

主要包括行總寬度、行消隱后肩(HBPD+1)、行消隱前肩(HFPD+1)、行同步脈沖(HSPW+1)、行顯示時序段(HOZVAL+1),它們之間的關系為:

行總寬度 = (HBVD+1) + (HFPD+1) + (HSPW+1) + (HOZVAL+1)

行時序各部分的作用如下:

HBPD:確定行同步信號和行數據傳輸前的一段延時,描述行數據傳輸前延遲時間內VCLK脈沖個數;

HFPD:確定行數據傳輸完成后到下一行同步信號到來的一段延遲時間,描述行數據傳輸后延遲時間內VCLK脈沖個數;

HSPW:確定行同步時鐘脈沖寬度,描述行同步脈沖寬度時間內VCLK脈沖個數;

HOZVAL:確定顯示的水平方向尺寸。

場時序如圖3所示。

主要包括場總寬度、場消隱后肩(VBPD+1)、場消隱前肩(VFPD+1)、場同步脈沖(VSPW+1)、場顯示時序段(LIINEVAL+1),它們之間的關系為:

場總寬度 = (VBVD+1) + (VFPD+1) + (VSPW+1) + (LIINEVAL+1)

列時序各部分的作用如下:

VBPD:確定幀同步信號和幀數據傳輸前的一段延時,是幀數據傳輸前延遲時間和行同步時鐘間隔寬度的比值;

VFPD:確定幀數據傳輸完成后到下一幀同步信號到來的一段延時,是幀數據傳輸后延遲時間和行同步時鐘間隔寬度的比值;

VSPW:確定幀同步時鐘脈沖寬度,是幀同步信號時鐘寬度和行同步時鐘間隔寬度的比值;

LINEVAL:確定顯示的垂直方向尺寸。

典型的LCD時序圖如圖4所示,通過與VGA時序進行比較,可以發現LCD掃描時序和VGA時序很相似,這就為通過LCD控制器產生VGA所需時序信號提供了可能性,同時也為LVDS轉VGA技術提供了理論依據。

要實現這種可能性,需要解決的問題主要有:

由于VGA接口的同步信號都是高電平有效而S5PV210的LCD接口同步信號是低電平有效,因此要解決兩者的電平轉換問題。

由于VGA接口的紅綠藍通道都為模擬量,而S5PV210的LCD控制器輸出為RGB數字信號,為了解決信號不匹配的問題,必須通過D/A轉換,將數字信號轉換成模擬信號。

針對轉換需求,本設計采用DS90CF364A芯片和D/A芯片SDA7123來解決此問題。

3 DS90CF364A和SDA7123芯片簡介

DS90CF364A接收器可將4路LVDS數據流轉換成并行的28位CMOS/TTL數據(24位RGB和4位Hsync、Vsync、DE及CNTL)。另外,DS90CF364A也可實現將3路LVDS數據流轉換成并行的21位CMOS/TTL數據(18位RGB和3位Hsync、Vsync及DE)。這兩種接收器的輸出都采用下降沿選通。一個上升沿或下降沿選通發送器(DS90C383A/DS90C363A)可以和一個下降沿選通接收器在無任何傳輸邏輯的情況下互操作。

相比上一代產品,DS90CF364A的輸出提供了一個更寬的數據有效時間,其結構框圖如圖5所示。

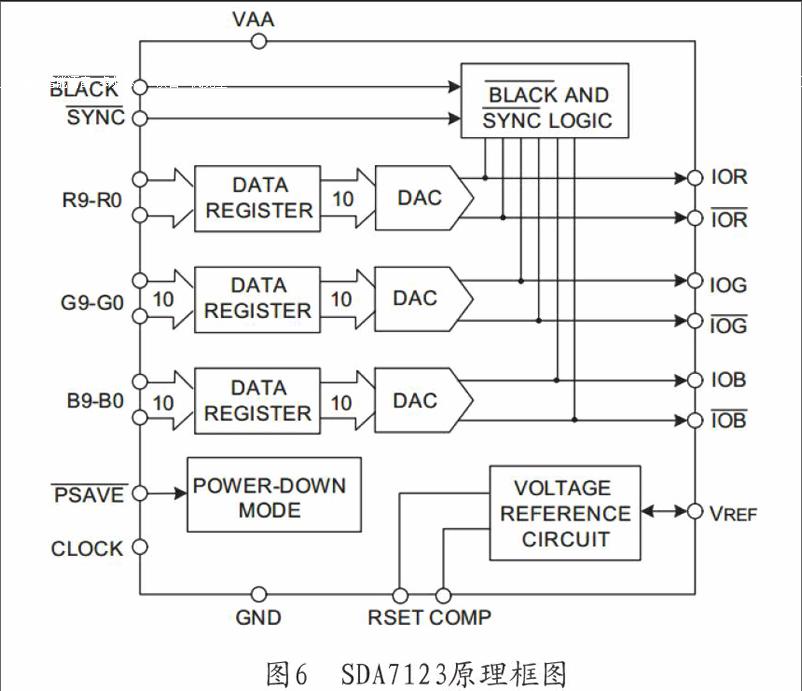

SDA7123是三路10位視頻D/A轉換器,分別完成R(紅)、G(綠)、B(藍)信號轉換,電流型輸出,綠通道可帶同步信號輸出。它的數據更新頻率MSPS為140MHZ,SDA7123內帶1.23V基準,工作溫度范圍寬(-40℃~+85℃)。適用于數字視頻系統、圖像處理、儀器、高精度顯示器、視頻信號重建等系統中,可與ADV7123替換使用。

其原理框圖如圖6所示。

SDA7123有三路獨立的10位輸入端口,可以在單電源5V下工作,也可以在單電源3.3V下工作。此外,SDA7123還有附加的兩個視頻控制信號:復合(同步信號)及(黑電平)。

4 LVDS轉VGA接口電路設計

為了實現LVDS到VGA的轉換,整體的硬件接口電路設計方法如下:

通過DS90CF364A芯片實現3路LVDS數據流到并行21位CMOS/TTL數據的轉換;

DS90CF364A芯片轉換后的21位CMOS/TTL數據中有18位屬于RGB數據,將此18位數據作為SDA7123芯片的輸入,最終完成LVDS到VGA接口的D/A轉換設計。

該轉換模塊的結構框圖如圖7所示。

5 S5PV210芯片LCD相應控制寄存器設置

VGA輸出支持多種分辨率顯示模式,不同的分辨率顯示模式對應的時序參數是不同的。因此,首先需要選定一個輸出分辨率;其次就是配置相應的LCD控制器,以產生對應的時序參數。本方案采用PC作為顯示輸出端,多數廠商的PC顯示器默認都支持分辨率VESA標準,因此本方案可以根據此標準來設置相應的LCD控制器參數,使得產生的VGA輸出可以在大多數品牌廠商生產的PC端正常顯示。

由于分辨率800×600、刷新頻率為60Hz的VGA顯示輸出在一些品牌PC端并不能得到很好的支持,因此本方案選擇分辨率1024×768、刷新頻率為75Hz、16位彩色的VGA顯示模式作為案例,來詳細分析LCD相應控制寄存器的設置步驟。根據VESA標準,可以獲得1024×768@75Hz下,行時序和場時序各部分的取值范圍,其取值范圍如表2所示。

下面根據表2的取值范圍,來設置LCD相應的控制寄存器。首先聲明,本案例的Src_clk (Frequency of Clock source)值為166 750 000Hz,因此,以下各個控制寄存器的取值都是在此基礎上進行設置的。

VIDCON0寄存器。

CLKVAL_F:確定VCLK和CLKVAL[7:0]之間的比率。當CLKVAL>=1時,VCLK=HCLK/(CLKVAL+1)。

本方案的HCLK=166.75MHz,VCLK=Pixel Clock=78.75MHz,因此CLKVAL需設置為1。

L1_DATA16:選擇間接i80接口(LDI1)數據輸出格式模式,本設計采用的是16bpp模式,因此設置L1_DATA16=000.

L0_DATA16:選擇間接i80接口(LDI0)數據輸出格式模式,設置L0_DATA16=000,選擇16位模式。

VIDTCON0寄存器。

VBPD:參考表2的數據可知,VBPD=(V Back Porch)/(Hor Total Time)=0.466ms/16.660us≈28;

VFPD:參考表2的數據可知,VBPD=(V Front Porch)/(Hor Total Time)=0.017ms/16.660us≈1;

VSPW:參考表2的數據可知,VSPW=(Ver Sync Time)/(Hor Total Time)=0.05ms/16.660us≈3;

VIDTCON1寄存器。

HBPD:由于VCLK=Pixel Clock=78.75MHz=12.6984ns,因此,參考表2的數據可知,HBPD=(H Back Porch)/(Pixel Clock)=2.235us/12.6984ns≈176;

HFPD:與上面類似,HFPD=(H Front Porch)/(Pixel Clock)=0.203us/12.6984ns≈16;

HSPW:與上面類似,HSPW=(Hor Sync Time)/(Pixel Clock)=1.219us/12.6984ns≈96;

VIDTCON2寄存器。

LINEVAL:由于本方案采用的是1024×768的分辨率,因此,LINEVAL=(Horizontal display size)-1=1023;

HOZVAL:HOZVAL=(Vertical display size)-1=767。

WINCON0寄存器。

BPPMODE_F:本方案采用的是16bpp(R:5-G:6-B:5)顯示模式,因此,BPPMODE=5。

通過以上設計,就可以實現LVDS轉VGA的信號輸出。本方案的硬件電路采用透傳模式,因此,只需設置好LCD控制器的相應寄存器,即可通過SDA7123的D/A轉換,實現將視頻或圖片信息輸出到VGA顯示屏上。

6 測試

通過本方案設計的硬件電路,將S5PV210的LVDS接口和顯示器的VGA接口連接起來,配置好相應的LCD控制寄存器,即可實現正常的視頻或圖片輸出。顯示圖像如圖8所示。

7 結論

本文提出了一種采用S5PV210的LCD控制器來實現VGA顯示的方法。通過分析比較LCD接口時序與VGA接口時序的相同點,論證了LVDS轉VGA接口的可行性。本設計通過配置LCD控制寄存器產生LVDS數字信號,然后通過DS90CF364A芯片將LVDS數字信號轉換成TTL信號,最終通過視頻D/A芯片SDA7123將TTL信號轉換成VGA接口所需的模擬信號。實驗結果表明,圖像通過LVDS-VGA轉換電路,在VGA接口的顯示屏上,顯示圖像良好,可以滿足廣大普通用戶的需求。該設計方案不僅成本低廉而且設置簡單,適合有此需求的工程廣泛采用。

參考文獻

[1]韋東山.嵌入式Linux應用開發完全手冊[M].北京:人民郵電出版社,2009:197-210.

[2]宋寶華.Linux設備驅動開發詳解[M].2版.北京:人民郵電出版社,2014:440-443.

[3]王國裕,尹偉,張紅升.嵌入式系統VGA顯示驅動實現[J].電子世界,2014(10):454-455.

[4]方鵬,張紅雨.基于ARM處理器S3C2440的VGA顯示技術[J].電子設計工程,2011,19(11):174-176.