基于28nm工藝下的LVDS發(fā)送器設計

羅慶紅,劉怡俊,葉劍科,陶永耀,陽昕,李邵川

(1.廣東工業(yè)大學,廣州 510006;2.炬芯(珠海)科技有限公司,珠海 519000;3.熠芯(珠海)微電子研究院有限公司,珠海 519000)

基于28nm工藝下的LVDS發(fā)送器設計

羅慶紅1,劉怡俊1,葉劍科1,陶永耀2,陽昕2,李邵川3

(1.廣東工業(yè)大學,廣州 510006;2.炬芯(珠海)科技有限公司,珠海 519000;3.熠芯(珠海)微電子研究院有限公司,珠海 519000)

在對LVDS發(fā)送器電路的基本原理與結構研究的基礎上,設計一種高速低電壓差分信號(LVDS)發(fā)送器電路。電路采用臺灣積體電路制造公司(TSMC)的28nm HKMG工藝設計實現,采用一種新型的數據同步采樣設計。仿真結果表明,該發(fā)送器電路在電源電壓為3.1V的工作條件下,有發(fā)送端匹配電阻存在的情況下,發(fā)送器在單端輸出擺幅400mV的情況下消耗平均功率為39mW。

廣東省和廣州市科技項目(No.2016B090904001、No.2016B090918126、No.2014B090901061、N2015B090901060、No.2015-B090908001、No.2014Y2-00211)

0 引言

隨著半導體技術的發(fā)展以及社會信息化的程度越來越高,芯片之間的通信頻率要求越來越高,傳輸的數據量也越來越大。此時傳統(tǒng)的傳輸技術遇到了挑戰(zhàn),芯片通信速度成為了一個瓶頸問題。20世紀90年代,LVDS接口技術的出現,為解決當前這一瓶頸問題提供了可能。LVDS(Low Voltage Differential Signaling)即低壓差分信號接口,具有傳輸速度高、抗噪聲能力強、功耗低、成本低等諸多優(yōu)點。目前,LVDS技術已得到廣泛的應用。

本文給出的LVDS發(fā)送電路是在 TSMC 28nm HKMG工藝下設計實現。首先介紹了發(fā)送器的規(guī)格方案,然后對系統(tǒng)設計的關鍵技術進行了闡述和仿真,隨后給出了發(fā)送器的仿真結果及分析。

1 LVDS發(fā)送系統(tǒng)設計規(guī)格

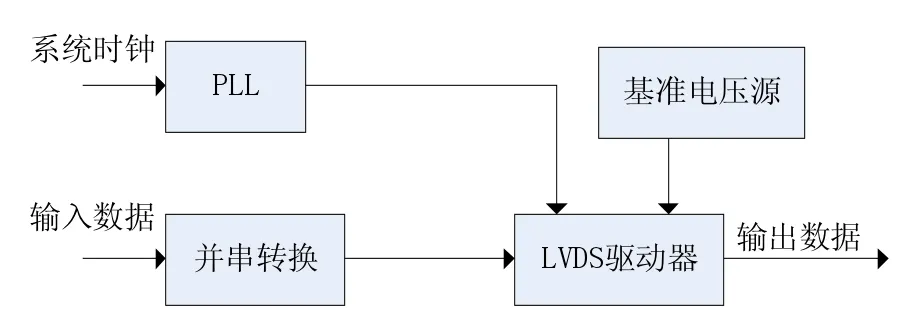

圖1所示為LVDS發(fā)送和接收基本架構,包括奇偶兩個通道,每個通道包括4組data lane和1組clock lane,其中data率和clock頻率的關系為7:1,且clock的占空比為57.6%。這里,clock表征像素時鐘,data為一個像素點對應的所有數據,包括色深以及 DE、VSYNC、HSYNC等,色深支持6bit和8bit。

下面給出單通道LVDS發(fā)送數據與RGB數據的映射關系,分為6位和8位色深兩種情況。對于6位色深,RGB數據為 3×6=18bit,再加同步信號(VSYNC、HSYNC)以及數據使能DE,一共21bit數據,所以只需要3個發(fā)送數據通道:TX0+/TX0-,TX1+/TX1-,TX2+/ TX2-,以及時鐘通道:TXCLK+/TXCLK-。對于8位色深,RGB數據為3×8=24bit,再加同步信號(VSYNC、HSYNC)以及數據使能DE,一共27bit數據,所以需要4個發(fā)送數據通道:TX0+/TX0-,TX1+/TX1-,TX2+/ TX2-,TX3+/TX3-,以及時鐘通道:TXCLK+/TXCLK-。

此外,還可以給出各種數據的映射功能,我們可以以此實現PCB的靈活走線。如果PCB走線連接到接收端的端口順序和發(fā)送端輸出的端口順序相反,那么不需要更改 PCB走線,只需要調整發(fā)送端發(fā)送數據的順序即可。

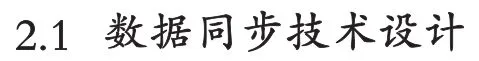

LVDS發(fā)送器電路由鎖相環(huán)、基準電壓源、并串轉換和驅動器這幾大模塊組成。如圖2所示,PLL模塊為電路提供精準時鐘,保證數據同步性,基準電壓源為驅動電路提供基準偏置電壓。

2 LVDS發(fā)送系統(tǒng)關鍵技術

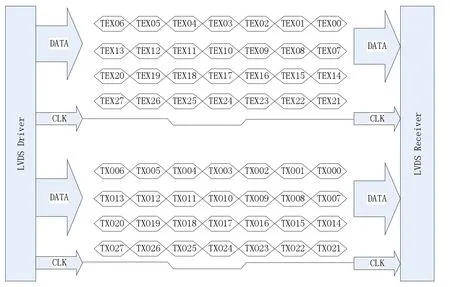

LCD控制器會同時向LVDS發(fā)送端送出輸入數據LVDSIN<34:0>和輸入時鐘信號CK_LVDS。為了能夠準確地對數字數據進行采樣,實現后續(xù)的模數接口轉換,需要合理安排采樣時序。

本設計中采用的方法如下:CK_LVDS用作內部同步鎖相環(huán)PLL的參考輸入,PLL輸出和它同步的時鐘信號CK1X和CK7X,用作發(fā)送電路的并串轉換時鐘。在數據同步設計中,具體做法是:采用CK7X對CK1X進行采樣,抓取三排之后輸出時鐘信號CKIN,然后用CKIN去采樣輸入數據LVDSIN<34:0>,由此可以實現安全采樣。

此外,考慮到輸入數據和輸入時鐘的時序關系,系統(tǒng)要求數據和時鐘在模數界面上要對齊,即時鐘偏移skew要小。本設計中給出skew約束,即data相比時鐘的skew為+-1ns范圍內。

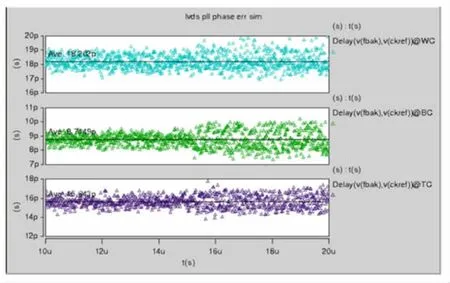

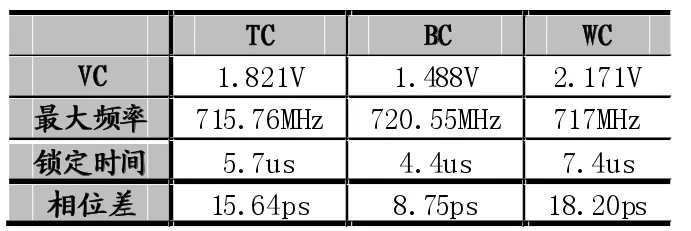

鎖相環(huán)(Phase Locked Loop,PLL)是LVDS接口系統(tǒng)中的關鍵模塊。在LVDS接口系統(tǒng)中,它為整個系統(tǒng)提供穩(wěn)定、精確的片內時鐘。PLL的鎖定過程仿真及相位誤差仿真如圖3、圖4所示,TC、BC、WC分別為芯片的三種工作環(huán)境。

圖2 發(fā)送器電路結構圖

圖3 PLL鎖定過程仿真

圖1 LVDS收發(fā)系統(tǒng)基本架構

圖4 PLL相位誤差仿真

圖6 LVDS發(fā)送電路仿真

PLL整體仿真結果如表1所示,三種工作環(huán)境下,PLL電壓最終都達到穩(wěn)定,說明鎖相環(huán)可以正常進入鎖定狀態(tài),鎖定時間都小于8us,相位誤差小于20ps。此設計滿足最初的設計標準。

表1 PLL整體仿真結果

圖5 發(fā)送器仿真模型

3 發(fā)送器電路仿真及功耗分析

發(fā)送器的仿真采用Agilent示波器和邏輯分析儀,仿真模型如圖5所示,輸出差分信號間跨接100歐姆的電阻 ,并分別接2pF的電容。

當數據頻率為700MHz,共電極電壓V_COM= 1.05V時,發(fā)送器仿真結果如圖6所示。圖6為輸出低壓差分信號瞬態(tài)波形圖,發(fā)送器在700MHz數字信號的輸入頻率下,完成數字信號到低壓差分信號的轉化,其電壓幅度為372mV,共模電壓為1.28V,符合 LVDS標準輸出。輸出信號眼圖張開大,輸出穩(wěn)定。

當設置芯片內部電壓1.8V,電源電壓3.1V時,計算得到平均功耗為39mW。

4 結語

本文介紹了一種基于HKMG 28nm工藝的LVDS發(fā)送器。該發(fā)送器電路采用新型的數據同步采樣設計,使數據采樣更準確,時序安排更合理。在電源電壓3.1V,芯片內電壓1.8V的條件下,平均功耗為39mW。本設計已經投入實際應用,其性能可靠、穩(wěn)定,可廣泛集成于28nm工藝的數據通信及信號處理等芯片內。

[1]Huang Xing-fa,Liang Li,Xu Kai-kai.A 0.35um CMOS 2.4 G b/s LVDS for High-Speed DAC.2009 IEEE 8th International Conference on ASIC

[2]Electrical Characteristics of Low-Voltage Differential-Signaling(LVDS)Interface Circuits,TIA/EIA-644.National Semiconductor Corp, ANSI/TIA/EIA,1996.

[3]莫遲,應建華,鄒望輝.LVDS高速數據驅動器電路設計與研究.華中科技大學學報(自然科學版),2003,10,31(10):13-15.

[4]Xu Jian,Wang Zhi-gong,Niu Xiao-kang.Design of High Speed LVDSTransceiver ICs[J].Journal of Semiconductors July,2010.

[5]矯逸書,周玉梅.千兆比特數據率LVDS接口電路設計[J].固體電子學研究與進展,2010,03.

Design of LVDS Transm itter Circuit Based on the 28nm Process

LUOQing-hong1,LIU Yi-jun1,YE Jian-ke1,TAO Yong-yao2,YANG Xin2,LIShao-chuan3

(1.Guangdong University of Technology,Guangzhou 51000;2.Actions(Zhuhai)Technology Co.Ltd.,Zhuhai 519000;3.Actions(Zhuhai)Microelectronics Research Institute Co.Ltd.,Zhuhai 519000)

Based on the research on the basic principle and structure of the LVDS transmitter circuit,designs a high-speed low voltage differential signal(LVDS)transmitter circuit.Designs the circuit by using 28nm HKMG process of Taiwan integrated circuitmanufacturing company (TSMC),uses a new type of data synchronization sampling design.The simulation results show that,in the power supply voltage is 3.1V working conditions,with the output swing of 400mV,the average power consumption of the transmitter circuit is 39mW.

羅慶紅(1988-),男,湖北襄陽人,碩士,研究方向為衛(wèi)星導航

2017-03-06

2017-05-02

1007-1423(2017)13-0038-04

10.3969/j.issn.1007-1423.2017.13.009

LVDS;數據傳輸;發(fā)送器;采樣;鎖相環(huán)(PLL)

LVDS;Data Transmission;Transmitter;Sampling;Phase-Locked Loop