單片FPGA的小型非制冷紅外機芯設計

顧 鑫, 曹丹華, 吳裕斌, 欒永昕, 王偉成

(1.華中科技大學 光學與電子信息學院,湖北 武漢 430074; 2.江蘇北方湖光光電有限公司,江蘇 無錫 214035; 3.南京大學 軟件學院,江蘇 無錫 210000)

單片FPGA的小型非制冷紅外機芯設計

顧 鑫1,2, 曹丹華1, 吳裕斌1, 欒永昕2, 王偉成3

(1.華中科技大學 光學與電子信息學院,湖北 武漢 430074; 2.江蘇北方湖光光電有限公司,江蘇 無錫 214035; 3.南京大學 軟件學院,江蘇 無錫 210000)

針對傳統的基于數字信號處理器(DSP)+現場可編程門陣列(FPGA)的非制冷紅外機芯平臺存在體積大、功耗大、實時性差、系統集成度低等不足,提出了一種基于單片FPGA的小型化非制冷紅外機芯平臺設計。針對25 μm非制冷紅外探測器,為滿足小型化、低功耗要求,平臺在采用先進的FPGA處理器和DDR3存儲器技術的同時,將硬件邏輯算法與NIOS Ⅱ軟核相結合,完成對紅外探測器的時序驅動、溫度控制、圖像的非均勻性處理、圖像增強以及各種人機接口控制。實驗結果表明:該系統成像質量較高,系統功耗小于2 W,系統延時小于0.5 ms,系統具有較強的可拓展性。

非制冷紅外機芯; 現場可編程門陣列; IP核; NIOS Ⅱ

0 引 言

非制冷紅外機芯[1]有著廣闊的應用前景,我國在此領域與國際先進水平還存在較大差距。國內單位在非制冷機芯開發的時候往往采用基于現場可編程門陣列(FPGA)+數字信號處理器(DSP)的處理架構[2,3],其中FPGA負責探測器的時序驅動、A/D數據采集和一些簡單的控制處理,DSP負責復雜圖像算法的運算。這種機芯由于采用了雙處理系統的架構存在體積和功耗過大的問題,同時還存在實時性較差、算法可移植性差等問題。這些弊端決定了該處理架構不適用于一些特別的定制領域,如手持便攜設備、高速圖像采集設備等。

FPGA是一種大規模可編程芯片,其本身存在著編程靈活、并行快速、模塊化可移植性高等特點。隨著芯片技術的發展FPGA內部又引入了NIOSⅡ軟核[4],這更是彌補和加強了其作為系統主芯片的軟硬件集成控制力。

本文采用單芯片的處理架構將探測器時序驅動、A/D釆集處理、非均勻性校正[5]、圖像處理、人機通信和I/O控制等功能全部集成在一塊FPGA芯片上,并采用分時復用的DDR3仲裁技術使多個圖像處理算法共享DDR3內存。實現緊湊化、小型化、低功耗機芯設計。系統實驗證明了該非制冷紅外機芯成像質量良好、功耗較低、實時性較好、體積較小。

1 非制冷機芯總體設計

非制冷紅外機芯由探測器,驅動模塊,FPGA控制模塊和電源模塊4部分組成,如圖1所示。

圖1 非制冷機芯組件整體設計

其中,探測器采用國產25 μm氧化釩探測器。FPGA控制模塊共有2片DDR3,其中一片作為NIOSⅡ運行的外部存儲器,另一片則用來存儲圖像及校正數據,FLASH用來存儲一些非均勻性參數以及其他需要掉電存儲的信息供開機后調用。硬件上,FPGA芯片選用 Cyclone 5系列的5CEFA7F31C7NES;DDR3選用MT41J18M16JT—125;FLASH芯片選用M25P64。整個系統中FPGA首先對探測器發送工作時鐘、積分時間、TEC參數、片上非均勻性校正(OCC)參數等配置及校正信號,為探測器正常工作提供正確的時序,在保證探測器能正常工作的情況下,對探測器送來的14 bit量化圖像信號進行紅外圖像算法處理,這些處理包括單點校正算法[6]、兩點校正算法[7]、盲元補償、直方圖均衡圖像增強[8]、非均勻性校正等。在完成各項時序控制和實時圖像處理后,紅外視頻信號將在PAL制模擬監視器上顯示。

2 FPGA的定制與交互設計

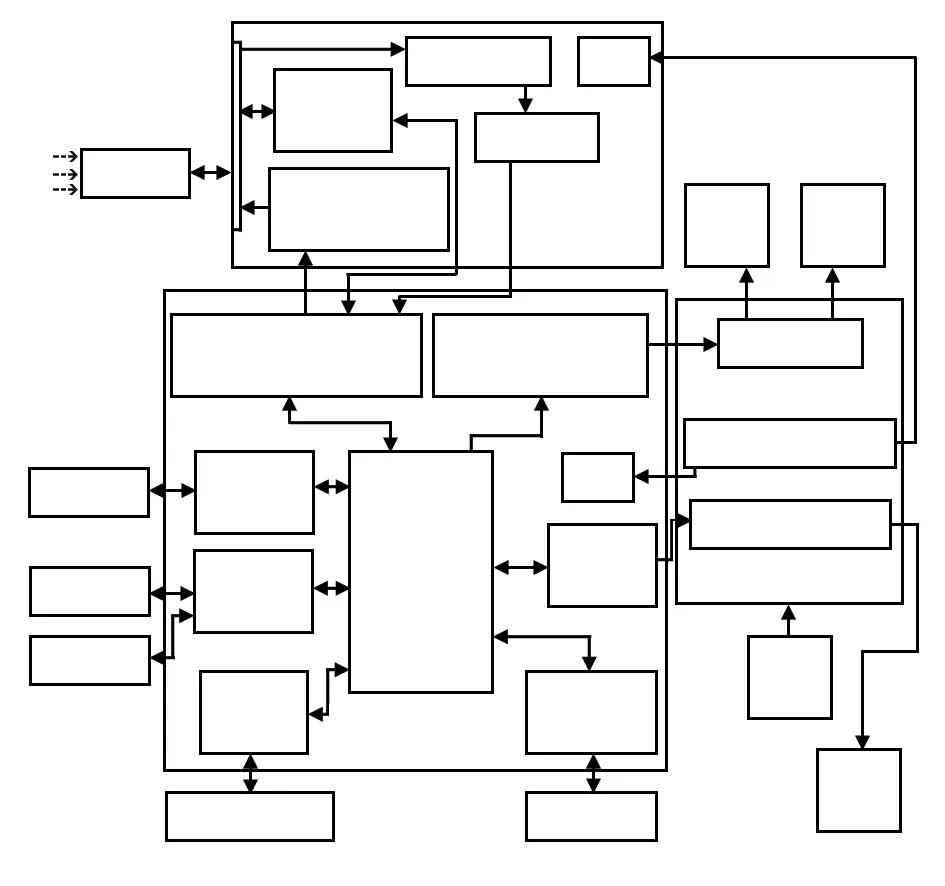

整個FPGA系統由NIOS Ⅱ,控制寄存器組和外部硬件3個部分組成,系統定制如圖2所示。

圖2 FPGA系統定制

NIOS Ⅱ為系統的控制核心,各個邏輯模塊為具體功能實現采用硬件邏輯語言(VHDL)滿足高實時性。控制寄存器組為獨立外設IP核,用來存儲各個邏輯模塊的數據和控制指令。NIOS Ⅱ與邏輯模塊之間通過Avalon總線與控制寄存器組進行數據傳遞和指令下達。人機控制按鍵部分采用I/O口經Avalon總線與NIOS Ⅱ交互。其他外部硬件也是通過各自IP核驅動NIOS Ⅱ讀寫。系統工作時NIOS II對傳來的串口指令、按鍵狀態進行存儲譯碼后轉入不同的流程語句處理,并調用各個功能邏輯模塊得到所需的輸出圖像。

比較發現,相比傳統的DSP+FPGA架構的系統而言,由于該系統圖像處理部分采用硬件邏輯語言設計,其實時性明顯要高于前者;同時系統采用FPGA內部集成的NIOS Ⅱ軟核作為中央控制器,提出了一種基于控制寄存器組的軟硬交互的控制方式,將眾多功能控制集成于一組寄存器,通過編址實現控制,具有較高的集成度和可控性。而以上功能僅需要一片芯片即可實現。

3 系統軟件設計

非制冷紅外機芯軟件設計包含2部分組成,其中對實時性要求較低的外部控制、以及數據初始化部分通過NIOS Ⅱ程序完成,對實時性要求較高的探測器時序驅動、圖像處理算法和通信部分通過硬件邏輯語言實現。

3.1 非制冷機芯FPGA邏輯程序設計

3.1.1 探測器時序驅動設計

探測器工作需要FPGA提供正確的時序,其中包括輸入時鐘(SCL)、幀使能信號(FS)、上電復位信號(Res_N)、配置信號(SDL,SDH)。像素時鐘6 MHz,探測器時鐘頻率(SCL)為像素時鐘頻率的6倍。FS為高電平期間,SDL配置圖像的行周期、積分時間。FS的下降沿為一幀圖像的開始,此時OCC圖像校正數據通過SDL和SDH輸入到探測器,每行輸入一次。上電后驅動模塊首先從DDR中獲得探測器配置參數,然后實時配置紅外探測器。驅動模塊具體設計如圖3所示。

圖3 探測器時序驅動模塊設計

驅動模塊正常工作前需要為每個像素點尋找最優的片上非均勻性校正(OCC),本文通過模塊內的算法,分析紅外數據“videodata”的均勻性,不斷調整OCC輸出直至“videodata”達到設定的均勻性指標。同時探測器時序驅動模塊也可以通過Avalon總線NIOS Ⅱ相連, NIOS Ⅱ讀取實時配置的OCC數據和所對應的圖像數據,通過串口傳至上位機,利用上位機軟件進一步分析OCC數據。

3.1.2 DDR3仲裁控制設計

傳統的DSP+FPGA設計往往常用SRAM或者是SDRAM,SRAM的讀寫速度最高為100 MHz,而SDRAM最高位167 MHz,較低的運行速度直接導致了紅外系統需要采用4片或更多存儲器芯片,增加了系統體積和功耗。如圖4所示本文采用DDR3的設計。

圖4 DDR3仲裁模塊控制流程

DDR3有較高的運行速度可達1 600 MHz,而紅外圖像處理的像素時鐘頻率較低為6 MHz,通過采用DDR3仲裁模塊設計可以協調各個圖像處理算法的讀寫需求,只需要一片就能滿足系統運行。仲裁模塊采用異步時鐘緩沖技術,各圖像處理模塊只需要對仲裁模塊提出訪問申請并給出數據、地址、時鐘等信號就能在周期內完成操作而不影響其他模塊的讀寫。

3.2 非制冷機芯NIOS Ⅱ軟核設計

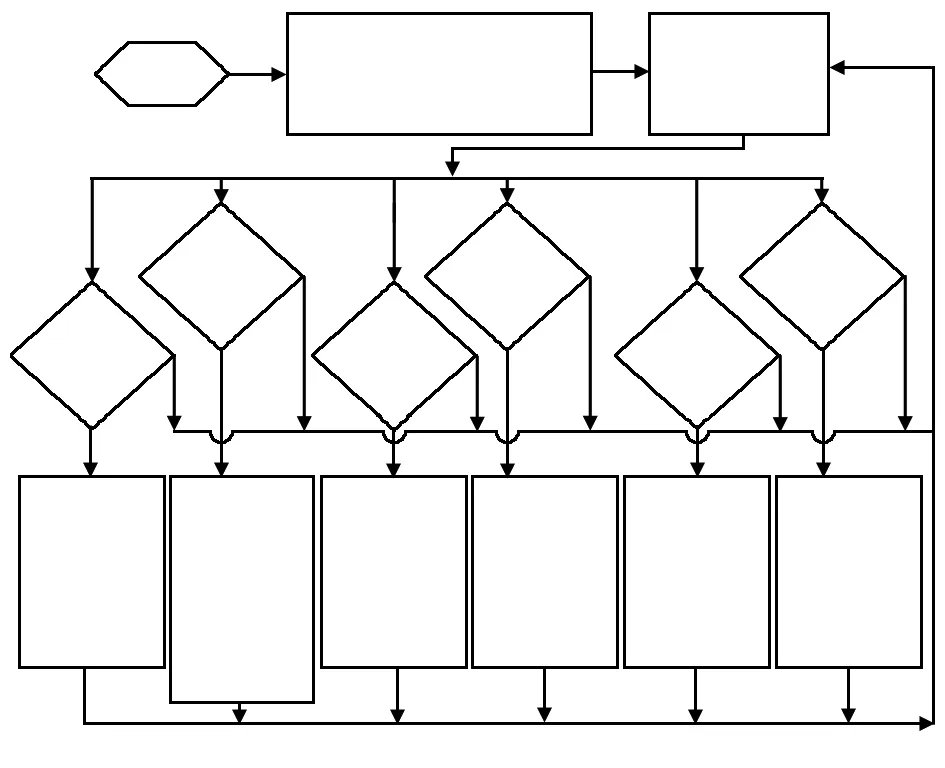

紅外機芯的NIOS Ⅱ配置通過Qsys軟件生成,Qsys是ALTERA最新一代的可視化SOPC[9]工具。NIOS Ⅱ程序通過不同地址設定讀取各個控制器和外部IP核的數據,并向其發送指令。NIOS Ⅱ主要功能流程如圖5所示。

圖5 NIOS II程序流程圖

NIOS Ⅱ在上電初始化時負責將探測器參數從Flash中寫入SDRAM;初始化完成以后,NIOS Ⅱ等待上位機指令,并根據指令調用各個功能邏輯模塊,更新圖像及圖像界面中的參數。

4 實驗結果及其分析

4.1 OCC

受材料、工藝影響國產非制冷紅外焦平面探測器的各個像元之間的非均勻性不如國外器件, 會影響系統成像質量,降低空間分辨率和溫度分辨率。國產探測器提供了一種前端校正手段,即OCC,通過每幀設定并發送OCC數據給探測器保證輸出響應的一致性。圖6為通過示波器得到的OCC配置前后的探測器每幀數據的電壓輸出響應(觀察背景為均勻黑體)。

圖6 探測器輸出波形

圖6中?,?采樣點的電壓差為電壓極差,觀察圖6(a)發現在OCC配置前探測器輸出電壓分布極差達到2.5 V,圖像均勻性較差。為了改善輸出響應的一致性,通過程序計算OCC校正數據并配置,使探測器輸出穩定在AD采樣區間內基準電壓值附近。圖6(b)為OCC配置后的一幀數據電壓輸出,其電壓分布極差得到了改善達到了460 mV。

4.2 紅外圖像處理

雖然OCC校正能保證一定的圖像非均勻性,但成像質量仍不高,為了提高圖像質量以及便于觀察,需要后期對探測器數據進行兩點校正、圖像增強等工作,成像效果如圖7和圖8所示。

圖7 兩點非均勻性校正

圖8 紅外圖像增強

觀察可以發現:兩點非均勻性校正算法去除了圖像中的非均勻豎條紋,圖像增強算法顯著加強了圖像邊緣的輪廓感。

4.3 機芯功耗和實時性測試

為了測試機芯的性能我們將FPGA機芯與基于DM642 DSP芯片的非制冷紅外機芯做了對比,其結果如表1所示。

需要指出的是,實時性是指圖像處理系統的延時量,具體值為圖像輸入信號與圖像輸出信號階躍點的時間差。通過對比可以發現:基于FPGA的紅外機芯無論是在體積、功耗還是實時性方面都優于傳統DSP機芯。

5 結 論

本文介紹了一種針對國產非制冷探測器的紅外機芯設計,設計采用以單片FPGA為核心的電路設計,通過SOPC技術及NIOSⅡ將驅動程序、圖像處理算法、應用程序與硬件接口有效結合,在功耗、體積、實時性上相對傳統DSP紅外機芯有較大優勢。實驗結果顯示,該紅外機芯有著較高的圖像均勻性和成像質量。該系統的完成對非制冷紅外機芯的國產化和小型化有著重要的意義。

[1] 馮 濤,金偉其,司俊杰.非制冷紅外焦平面探測器及其技術發展動態[J].紅外技術,2015(3):177-184.

[2] 王 磊,王寶珠,薛雙苓,等.基于DSP+FPGA的紅外熱成像偽彩色變換系統[J].制造業自動化,2013,35(7):149-152.

[3] 黃戰華,楊鶴猛,孫立彬,等.一種基于DSP+CPLD的低功耗實時紅外成像系統實現方法[J].光學技術,2012(1):14-18.

[4] 張天恒,葉 偉,王陽陽,等.基于SOPC的便攜式高精度頻率儀設計[J].儀表技術與傳感器,2015(5):34-37.

[5] 薛 慧.紅外焦平面陣列非均勻性校正方法研究[D].哈爾濱:哈爾濱工業大學,2007.

[6] 候良科,楊俊剛,鄧新浦,等.含運動目標的紅外圖像非均勻校正算法[J].傳感器與微系統,2015,34(8):142-148.

[7] 楊正宇.基于SoC的IRFPA非均勻性校正研究[D].成都:西華大學,2010.

[8] 陳 錢.紅外圖像技術及發展趨勢[J].紅外技術,2013,35(6):311-318.

[9] 劉紫燕,馮 亮,祁 佳.一種基于FPGA的實時視頻跟蹤系統硬件平臺設[J].傳感器與微系統,2014,33(7):98-102.

Design of miniaturized uncooled infrared movement based on FPGA

GU Xin1,2, CAO Dan-hua1, WU Yu-bin1, LUAN Yong-xin2, WANG Wei-cheng3

(1.School of Optical and Electronic Information,Huazhong University of Science and Technology; Wuhan 430074,China; 2.Jiangsu North Huguang Opto-Electronics Co Ltd,Wuxi 214035,China; 3.SoftWare Institute,Nanjing University,Wuxi 210000,China)

Aiming at problem that traditional uncooled infrared imaging system which based on DSP+FPGA has many disadvantages such as large volume,high power consumption,poor real-time performance,low system integration,and so on,a design of miniaturized uncooled infrared imaging system based on FPGA is proposed.The design aims at 25 μm uncooled infrared detector.The latest FPGA processor and DDR3 memory technology are adopted to meet the requirement of miniaturization and low power consumption.A novel solution of combination of hardware logic algorithm and NIOS Ⅱsoft core architecture is proposed.By this way,complete timing driving of infrared detector,temperature control,non-uniformity processing of image,image enhancement,man-machine interface control.Experimental results show the system owns characteristics of higher imaging quality,power consumption of system is less than 2 W,system delay is less than 0.5 ms and the system can be easy extended.

uncooled infrared movement; FPGA; IP core; NIOS Ⅱ

2016—06—08

10.13873/J.1000—9787(2017)06—0083—03

TN 216

A

1000—9787(2017)06—0083—03

顧 鑫(1979-),男,博士,高級工程師,主要從事模式識別、人工智能圖像處理等技術研究。