基于OMAP-L138的接口傳輸設計與實現

肖玉娟,李洋洋,廖世文

(廣州海格通信集團股份有限公司,廣州 510663)

基于OMAP-L138的接口傳輸設計與實現

肖玉娟,李洋洋,廖世文

(廣州海格通信集團股份有限公司,廣州 510663)

介紹基帶處理中使用的DSP(OMAP-L138)和FPGA的兩個接口設計。EMIFA時序參數靈活,使用方便,應用廣泛;UPP接口則應用于高速數據傳輸場合。這對C6000系列接口設計和應用具有普遍意義。

EMIFA;UPP;FIFO

0 引言

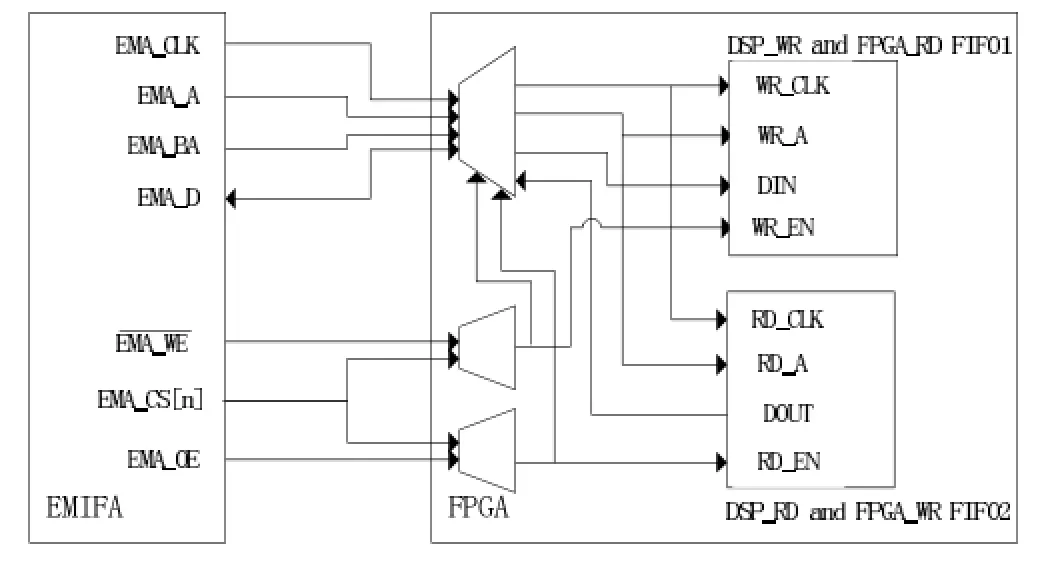

FPGA可用做DSP協處理器,或充當高速數據處理器件或高速數據橋接器件。由于EMIFA具有靈活的時序參數,只需要極少的FPGA邏輯,在這種情況下,只需最低限度的設計工作,使用標準FIFO就可以達到目的,所以Texas Instruments DSP平臺[1]中的外部存儲器接口(EMIFA)被廣泛用做連接到FPGA的接口。若對于寬帶信號的高速數據交互,則需要采用更高速率的UPP接口[2]。本文主要介紹這兩種接口設計及應用。

圖1 PLL0內部主要結構

1 EMIFA接口設計實現

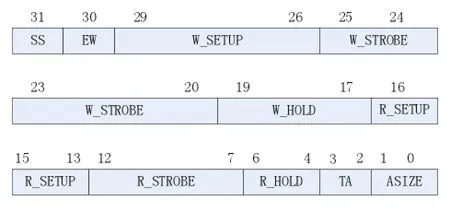

OMAPL138 EMIFA上的數據總線可以是16位寬,也可以是8位寬。OMAPL138晶振輸入24MHz,經過25倍的PLL乘法器后的頻率為600MHz。選擇DIV4.5分頻得到133.33MHz的EMIFA輸入時鐘源。產生EMIFA時鐘源的PLL0頻率配置如圖1所示。對于OMAPL138來說需要將片選、輸出時鐘、地址線、數據線、讀使能、寫使能等有關復用管腳設置為EMIFA的對應功能管腳,其次將EMIFA模塊的電源控制打開,最后配置如圖2所示的異步CSn配置寄存器(CEnCFG)對應支持CS2、CS3、CS4和CS5這四個存儲器空間。

圖2 異步CSn配置寄存器(CEnCFG)

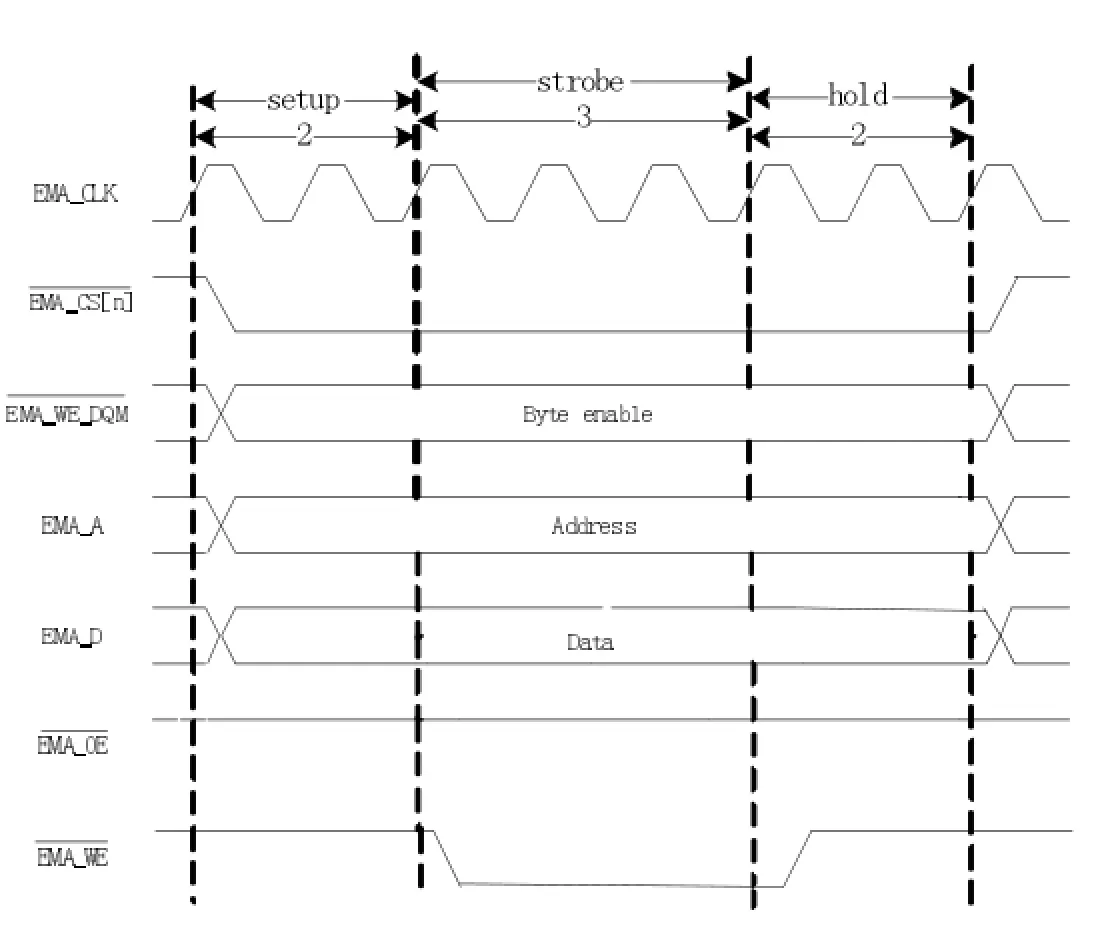

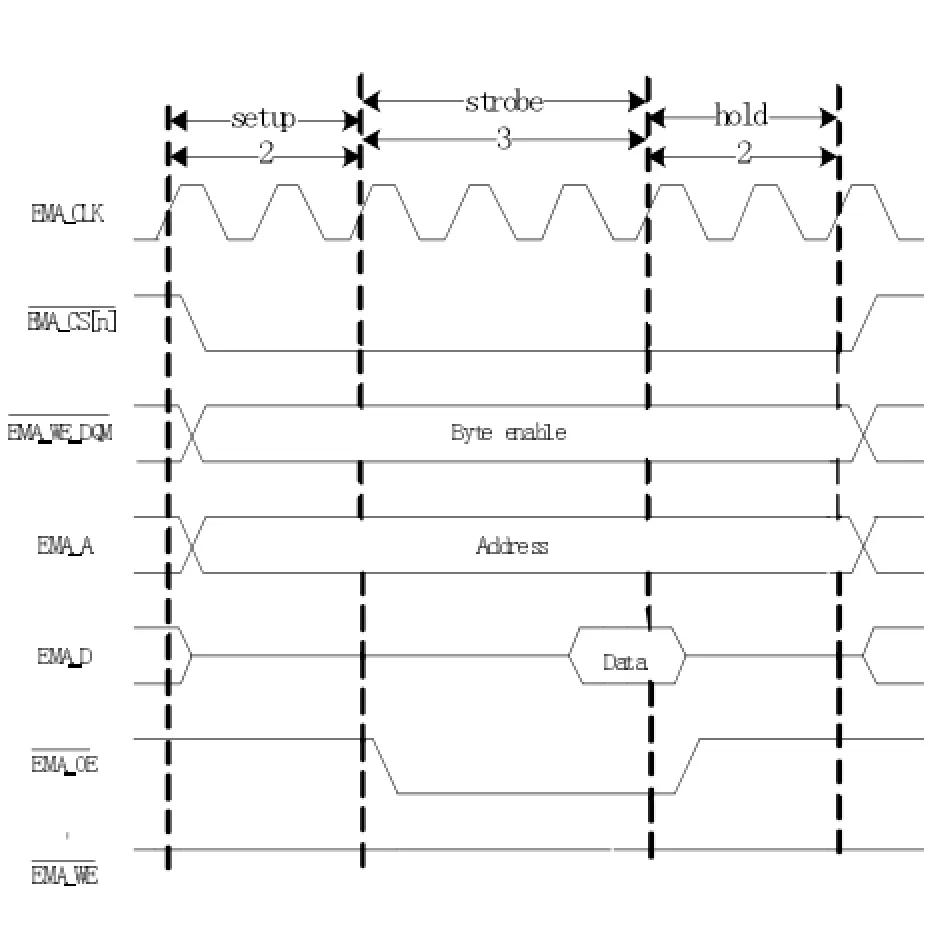

本設計使用了如圖3所示的雙口RAM的機制,默認讀寫的存儲深度為2000個16bit的數據。幀格式為:幀頭標志+幀長度+數據的格式。其中幀頭0x5555表示,0xAAAA表示。DSP下發數據到FPGA:由DSP這邊組幀發到FPGA端,當DSP把數據寫到W_RAM中后,更新幀頭標志為0xAAAA,地址0x0000,一旦FPGA監測到幀頭為0xAAAA,接著開始讀取W_RAM的數據,否則跳轉到上報數據狀態。FPGA讀完數據后,更新幀頭標志位0x5555,表示上一幀數據已經讀取完畢。FPGA上報數據到DSP:由FPGA這邊組幀上報到DSP端,當FPGA把數據寫到R_RAM中后,更新幀頭標志為0xAAAA,并發中斷,通知DSP讀走數據,DSP讀完數據后,更新該幀頭標志為0x5555,以便FPGA在上報下一幀數據的時候,通過檢測該標志。圖4所示為寫操作,EMIFA的異步CSn配置寄存器(CEnCFG)的設置方式使得當EMA_CS[n]為有效之后2個時鐘周期,異步寫使能(EMA_WE)成為有效,EMIFA給出數據。圖5所示為讀操作,CEnCFG寄存器設置為具有2個時鐘周期的建立延遲,3個帶選通脈沖的時鐘周期,2個保持周期終結一個讀操作。

2 UPP接口設計實現

通用并行端口UPP是一種多通道、高速并行接口,專為實現高速數據傳輸而設計。UPP模塊的設計有以下幾個優點:基于DMA的數據傳輸,在降低了CPU使用率的同時也節省了程序運行時間;兩個獨立的DMA為模塊本身私有,減少了對系統DMA資源的占用;控制信號較為簡單,簡化了與外部設備傳輸控制的步驟,降低了控制出錯幾率。UPP模塊包含一個DMA控制器,實現對兩個獨立數據通道的控制。DMA與系統存儲器之間數據交換位寬采用64bit設計,較普通訪問模式,DMA則具有很明顯的訪問速度優勢。每個DMA通道對應著一個獨立的物理通道,并且每個物理通道均可以配置成接收通道或者發送通道。兩個物理通道均最大支持16bit和最小8bit位寬的數據傳輸,滿足不同外設不同數據位寬傳輸的需求。UPP每個通道的只有很少的控制信號:START、ENABLE、CLOCK以及WAIT四個控制信號[3]。UPP支持兩種數據率傳輸方式:單倍數據率(Single Data Rate)即單時鐘沿傳輸數據,和雙倍數據率(Double Data Rate)即雙時鐘沿傳輸數據。通過CLOCK信號就設定UPP傳輸的速率,對于發送模式時鐘由OMAP-L138內部的PLL經過分頻產生,支持75.00MHz~4.69MHz范圍內的配置,支持150.00MB/s~4.69MB/s數據傳輸要求;對于接收模式則需由外部數據發送設備提供,但最大不得超過150MHz。

圖3 基于FIFO的EMIFA設計

項目中采用的是收發雙信道模式,信道A發,信道B收,收發都是單時鐘沿傳輸、8比特接口,忽略WAIT信號,START和ENABLE都是高電平有效,信號時序如圖6所示。發送的啟動是由FPGA控制發起,FPGA通過GPIO給DSP發8KHz的中斷,每來一個中斷后DSP判決發送數據;接收則直接利用UPP接收完成中斷來檢測DMA通道是否接收完數據,為了提高運行效率,其他中斷不響應,響應接收完成中斷后立即清中斷。發送時鐘分頻器CLKDIVA設置為5,由PLL1送來的發送時鐘為132MHz,因此經過分頻器后的發送引腳時鐘為(132/2)/(5+1)Mhz即11MHz。

圖4 異步寫入周期時域波形

圖5 異步讀取周期時域波形

圖6 UPP單時鐘沿傳輸信號時序圖

3 結語

在本文的項目中,與FPGA控制信息主要通過EMIFA通信來,因其對速率要求不高,但是對準確性有較高的要求。相對低速下的設計,完全可以滿足開發的需求。大量數據的收發則通過UPP完成。

[1]Texas Instrument Inc..OMAP-L138 technical referencemanual[Z].2009.

[2]TMS320C674X/OMAP-L1x Processor Universal Parallel Port(uPP)User’s Guide.June 2012.

[3]胡志國,范祝軍,何海菠.基于OMAP-L138的UPP接口的圖像數據實時傳輸的實現.自動化與儀器儀表,2013(03):149-150。

Design and Im p lem entation of Interface Transm ission Based on OMAP-L138

XIAO Yu-juan,LIYang-yang,LIAO Shi-wen

(Guangzhou HAIGE Communication Group Incorporated Company,Guangzhou 510663)

Introduces the two interfaces of DSP(OMAP-L138)and FPGA used in baseband processing.EMIFA timing parameters are flexible,easy to use,widely used;UPP interface is used in high-speed data transmission applications.This is of universal significance for the design and application of c6000 series interface.

EMIFA;UPP;FIFO

1007-1423(2017)12-0081-04

10.3969/j.issn.1007-1423.2017.12.021

肖玉娟(1986-),女,江西吉安人,碩士研究生,助理工程師,從事領域為衛星通信數字信號處理

2017-02-14

2017-04-12

李洋洋(1987-),男,河南漯河人,碩士研究生,工程師,從事領域為移動通信技術

廖世文(1985-),男,廣西柳州人,碩士研究生,工程師,從事領域為衛星通信數字信號處理