一種基于FPGA的硬件防火墻設計

唐澤坤+王修剛+宋偉+于珊珊+劉超

摘 要:本文提出了一種基于FPGA的硬件防火墻的實現方案,采用FPGA來實現百兆線速以上的防火墻設計。網絡數據在建立連接跟蹤后,由FPGA實現的快速處理板直接轉發,實現了網絡數據的線速處理,通用CPU在操作系統支持下,完成網絡數據連接跟蹤的創建、維護以及對網絡規則表的維護等工作。

關鍵詞:防火墻;FPGA;Verilog HDL;CPU

一、引言

防火墻是一種基本的網絡防護設備。它是一種設置在內部網和外部網之間的安全網關,通過安全策略和規則來控制外部用戶對內部資源的訪問,使外部網和內部網之間既保持連通性,又根據規則間接交換信息。防火墻所采用的硬件設備必須滿足網絡處理性能的需求。在早期網絡中,數據速率相對較低,協議也比較簡單,因此網絡設備通常以通用處理器配合分組處理軟件實現。然而,隨著數據速率的不斷提高和協議的日益復雜,通用處理器處理能力的增長逐漸落后于數據速率的增長,因此,基于通用處理器平臺的網絡產品開發者遇到了性能上的障礙。

本文針對目前防火墻的設計方式提出了一種基于FPGA的硬件防火墻的實現方案,采用FPGA來實現百兆線速以上的防火墻設計。傳統的基于x86等通用CPU的防火墻無法適應當前快速增長的網絡速度,無法實現線速過濾與轉發。本文采用FPGA結合通用CPU模式,可以快速處理網絡數據,能夠避免NP的不足。網絡數據在建立連接跟蹤后,由FPGA實現的快速處理板直接轉發,實現了網絡數據的線速處理。通用CPU在操作系統支持下,完成網絡數據連接跟蹤的創建、維護以及對網絡規則表(端口黑名單、IP黑名單、端口白名單)的維護等工作。FPGA硬件板和CPU各司其職,實現快速轉發的目的。實踐證明,這是一種兼容性比較好的網絡安全架構。

二、系統整體設計方案

硬件防火墻分為兩個數據通道,FPGA硬件板承擔網絡數據的按規則高速收發與轉發,并按指定規則要求通過PCI-E將數據上傳至x86CPU;x86主控板承擔慢速通道工作。

防火墻軟件系統根據TCP、UDP、ICMP協議實現不同的連接跟蹤、跟蹤表項的匹配、跟蹤表的動態維護;x86上防火墻軟件系統通過硬件驅動程序和FPGA硬件板進行通訊。

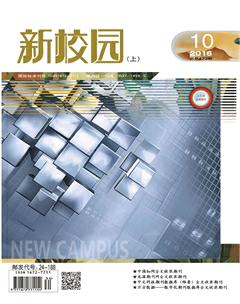

圖1中所示為FPGA系統設計過程中網絡抓包實驗中所形成的硬件架構圖。FPGA網絡抓包的數據可以通過串口發送至上位機,實驗可以清晰判斷當前網絡收發架構設計是否合理,能否準確地收發100Mbps的網絡數據。

在實現了基本的數據收發后,確定防火墻系統整體架構和功能模塊,如圖2所示。

可以看出在這里主要由網絡接口、網絡控制、MAC、外網處理模塊、PC處理模塊、PCI-E與DDR控制模塊幾大部分構成。

三、系統HDL設計方案

系統使用Verilog HDL語言完成設計。下面介紹一些主要模塊設計。

1.外網控制

本模塊的主要功能如圖3所示:

(1)存儲接收到的外網報文;

(2)對接收到的外網報文進行關鍵字提取和識別;

(3)對提取的結果根據用戶配置進行過濾;

(4)讀取存儲的本幀數據,根據本幀過濾的結果對其進行打包處理。

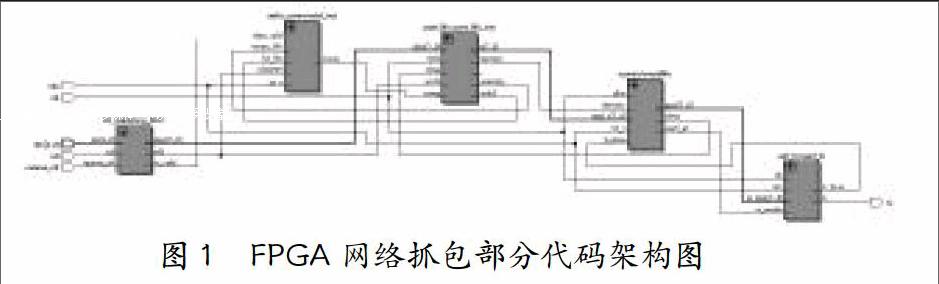

本模塊時序圖設計如圖4所示。

2.子模塊報文緩存功能設計

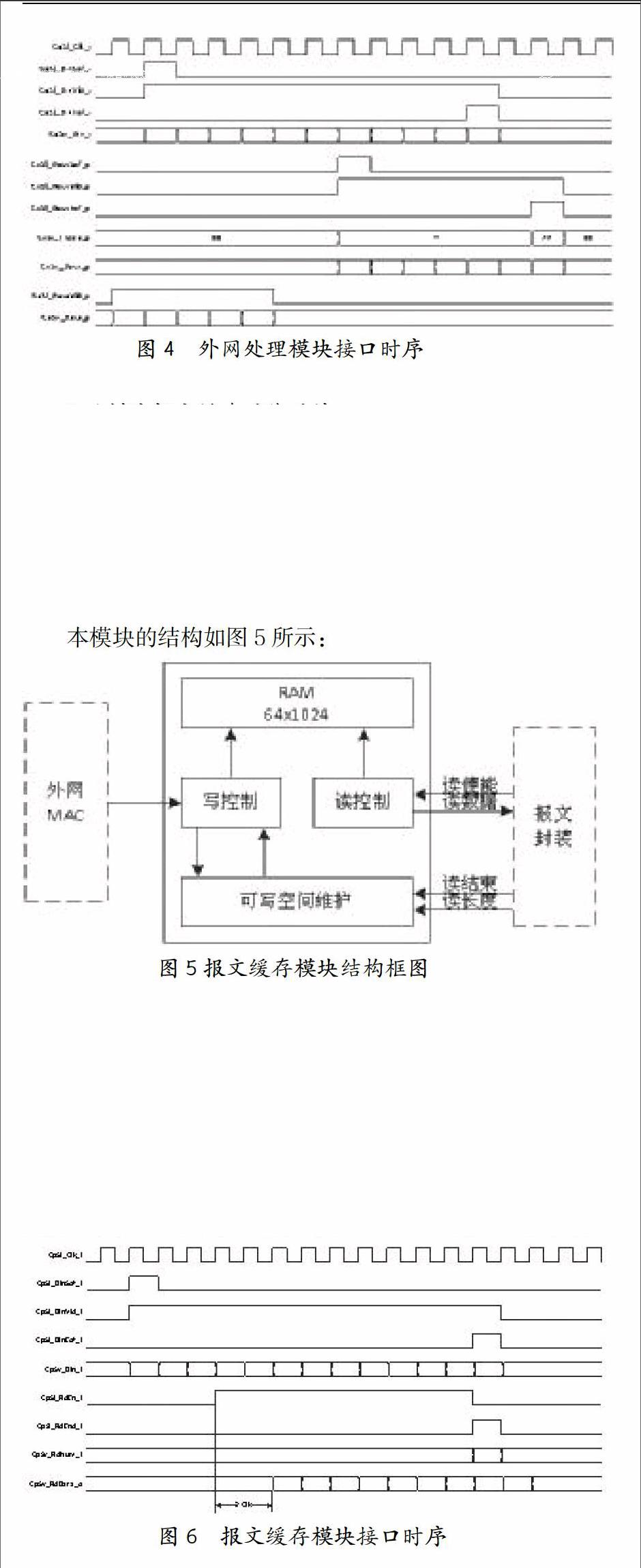

本模塊的功能是:用于緩存接收到的報文,等待本報文的過濾結果,由報文封裝模塊讀取此報文或者丟棄報文。本模塊實質上是一個循環的buffer,其位寬是64,深度是1024,可以存儲5個最大的1518Bytes報文。緩存模塊內部維護讀寫地址和可寫的空間,當可寫的空間小于1518Bytes時,不再接收數據。

本模塊的結構如圖5所示:

處理流程為:

(1)當報文到達時,首先檢查可寫空間是否大于1518Bytes,如果大于則向RAM中存入次報文,寫地址,循環累加,寫完后將本次寫入的數據量送給可寫空間維護,如果小于1518Bytes丟棄本報文,寫地址不變;

(2)寫空間維護,維護一個Counter,累加寫數據量,累減讀數據量,用RAM的總空間減去這個Counter就是可寫空間;

(3)當收到報文封裝模塊的讀使能時,讀地址累加,讀取RAM送出讀數據。

3.子模關鍵字提取功能設計

本模塊的任務是:在報文中提取過濾規則的關鍵字,關鍵字為標準IP協議數據包。

通過Type識別是否為IP報文,如果是,繼續提取Protocol、SIP、DIP;通過Protocol識別是否是TCP或者UDP報文,如果是,繼續提取SPort與DPort。報文結構如圖6所示,但是沒有option域。另外需要獲得本報文的長度(以Byte為單位)。

處理流程圖如圖7所示。

四、設計仿真測試

上述設計代碼在綜合后下載至硬件FPGA硬件板后,配合x86端測試軟件進行測試。限于實際條件,采用自循環數據測試數據收發,以及指定IP地址和端口地址的過濾測試,測試模式如圖8所示。經實際測試,系統能夠完成百兆數據的線速收發和指定規則的過濾。

五、結束語

本文基于FPGA的防火墻設計完成了基本的設計目標,能夠正常轉發和過濾指定規則的數據,能夠準確進行仿真和驗證,但仍屬于教學演示性設計,后續可以繼續進行優化,使系統更加完善。

(通訊作者:劉超)

參考文獻:

[1]夏宇聞.從算法設計到硬件邏輯的實現[M].北京:高等教育出版社,2001.

[2]王金明,楊吉斌. 數字系統設計與Verilog HDL[M]. 北京:電子工業出版社,2002.

[3]鄭堯.硬件防火墻中多模式匹配算法的設計與實現[D].哈爾濱:哈爾濱工業大學,2009.

[4]唐正軍,李建華.入侵檢測技術[M].北京:清華大學出版社,2004.

[5]Wes Noonan, Ido Dubrawsky(美).防火墻基礎[M].北京:人民郵電出版社,2007.

[6]胡道元.網絡安全[M].北京:清華大學出版社,2004.

[7]石晶林,程勝,孫江明.網絡處理器原理、設計與應用[M].北京:清華大學出版社,2003.

[8]肖晨陽.基于FPGA的硬件防火墻設計和實現[D].長沙:湖南師范大學,2009.

作者簡介:唐澤坤(1994- ),男,山西長治人,大學本科在讀,電子科學與技術專業;劉超(1981- ),男,遼寧凌源人,碩士,講師,研究方向:嵌入式系統。