基于IP核FIR濾波器的設計與FPGA實現

郭 勇, 楊 歡

(南京北方信息控制集團有限公司 產品研發中心,江蘇 南京 211153)

基于IP核FIR濾波器的設計與FPGA實現

郭 勇, 楊 歡

(南京北方信息控制集團有限公司 產品研發中心,江蘇 南京 211153)

介紹了一種基于Altera公司IP核進行FIR數字濾波器的參數設計及在FPGA中的快速實現方法。為了達到FIR濾波器的性能要求,介紹了Matlab和IP核中信道沖激響應的階數和時域系數的設計方法。編程實現了時域卷積運算,并給出了沖激響應和輸入數據比特量化的方法和結果。為驗證FIR濾波器設計的正確性,分別給出了Matlab和ModelSim中FIR低通濾波器的仿真輸入波形和濾波輸出波形。仿真結果表明,設計的濾波器通帶信號完整,阻帶濾波性能良好,該方法具有較好地適用性。

FIR;IP核;FPGA;時域卷積;波形驗證

0 引言

FIR濾波器具有嚴格的線性相位,且穩定性高,廣泛用于信號檢測和處理等領域。基于FPGA實現FIR濾波器的方法具有靈活、高效和動態可配置等特點。Altera公司的FIR濾波器的IP核功能強大,采用IP核的方法既可以保證性能,又能極大地縮短設計時間。目前的文獻中,完整地介紹濾波器參數設計[1]、IP核設計方法[2]及濾波性能測試的文獻不多[3],而且針對卷積運算的代碼實現也沒有提及[4]。本文著重介紹Matlab和IP核中FIR濾波器參數的設計方法和時域卷積運算的編程實現,并采用大容量仿真數據測試基于IP核FIR濾波器的濾波性能以及用Matlab設計濾波器的濾波性能。

1 FIR濾波器的數學原理及結構

FIR時域結構圖如圖1所示。

圖1 FIR時域結構

FIR濾波器是線性時不變系統,該系統的特征是輸出序列y(n)等于輸入序列x(n)與單位沖激響應h(n)的線性卷積。由圖1可知,y(n)等于當前時刻的輸入x(n)與N-1個時刻的x(n)與N個抽頭系數相乘再相加得到。FIR濾波器具有嚴格的線性相位特性,且h(n)滿足對稱性。

x(n)為輸入序列,h(n)為FIR濾波器的單位沖激響應,y(n)為輸出序列。x(n)與h(n)做卷積運算如下:

目前文獻中沒有提及對卷積運算的編程實現。本文給出上述公式的Matlab代碼實現如下:

%信號x經過FIR濾波器,N1=37,為FIR濾波器的階數,L為輸入序列的長度

z1=zeros(1,N1); %z1為1行37列的移位寄存器

y1=zeros(1,L); %y1為濾波后的信號

h1=h1’; %對信道沖激響應進行轉置

fori=1:L

z1(1) =x(i); %x為輸入序列

%加漢明窗進行濾波

% 2個矩陣做乘積運算,計算每個點的卷積值

y1(i) =z1*h1;

z2=z1(1:N1-1);

z1(2:N1)=z2;

z1(1)=0;

end

y1; %濾波后的信號

2 FIR濾波器的參數設計方法

設計的FIR低通濾波器通帶截止頻率為1.2 MHz,采樣頻率10 MHz,要求采用窗函數法設計。經過仿真驗證,選擇漢明窗,階數n=37,滿足要求[5-6]。在Matlab中輸入fdatool,啟動濾波器設計套件。在參數設置界面中輸入以下參數:方法采用窗函數法,選擇的窗口類型為“Hamming”,Fs=10 MHz,Fc=1.2 MHz。其中n=36,表示生成的階數n=37。生成的信道沖激響應h(n)為:

h(n)=[0.001 2,0.000 4,-0.001 0,-0.002 9,-0.003 9, -0.002 2,0.003 0,0.010 0,0.013 9,0.009 2,-0.0061, -0.026 8,-0.040 1,-0.031 3,0.008 9,0.076 7, 0.154 4,0.216 4,0.240 0,0.216 4,0.154 4,0.076 7, 0.008 9,-0.031 3,-0.040 1,-0.026 8,-0.006 1, 0.009 2,0.013 9,0.010 0,0.003 0,-0.002 2, -0.003 9,-0.002 9,-0.001 0,0.000 4,0.001 2] 。

為了驗證FIR低通濾波器設計的正確性,設計輸入信號為2個信號的疊加:一個是50kHz正弦波信號,一個是1.8MHz的正弦波信號,采樣個數L=10 000。經過FIR濾波器后,因為FIR濾波器的通帶截止頻率fc=1.2 MHz,所以只有50kHz正弦波信號輸出,而1.8MHz的正弦波信號被濾除,如圖2所示,輸出波形只有50kHz的正弦波信號,所以該FIR濾波器設計正確。

圖2 濾波器輸入輸出波形對比

設計另一種情況,輸入信號是50kHz的正弦波信號,疊加高斯白噪聲。因為高斯白噪聲在整個頻譜范圍內都存在,但通過FIR低通濾波器,可以濾除通帶內的白噪聲。波形如圖3所示。

圖3 疊加噪聲的正弦波信號輸入輸出波形

在FPGA中,參數為定點數,所以需要對濾波器參數h(n)和輸入數據進行比特量化,該文設計量化為10bit。h(n)的10bit量化在IP核設置中實現,輸入數據的比特量化在Matlab中編程實現,形成txt文件,便于ModelSimSE軟件讀取輸入數據文件生成仿真測試結果[7-8]。

因為輸入數據有負數,所以采用二進制補碼形式表示。n=10,歸一化輸入數據,最大值量化為2n-1-1=511。10bit量化結果如圖4所示。

圖4 源數據10 bit量化對比

3 基于IP核FIR濾波器的設計方法

如前所述,FIR低通濾波器通帶截止頻率為1.2MHz,采樣頻率Fs=10 MHz,采用窗函數法設計,全并行模式。濾波器階數為37階,選擇漢明窗。在IP核設置界面中,Filter Type欄選擇Low Pass,在Coefficients欄選擇37,在Window Type欄選擇Hamming,在Sample Rate欄輸入1.0E7,在Cutoff Freq.1欄輸入1.2E6,因為采樣頻率10 MHz,該文設計FIR濾波器的全局時鐘clk為10 MHz,所以時鐘周期T=100 ns。生成的信道沖激響應h(n)的時域浮點值和比特量化值如圖5所示[9-10]。在QuartusII生成的頂層文件如圖6所示。其中的ask_sink_error[1..0]設為00,表示輸入數據沒有錯誤。

圖5 IP核參數設置界面

圖6 生成的FIR頂層模塊

4 FIR濾波器的性能測試

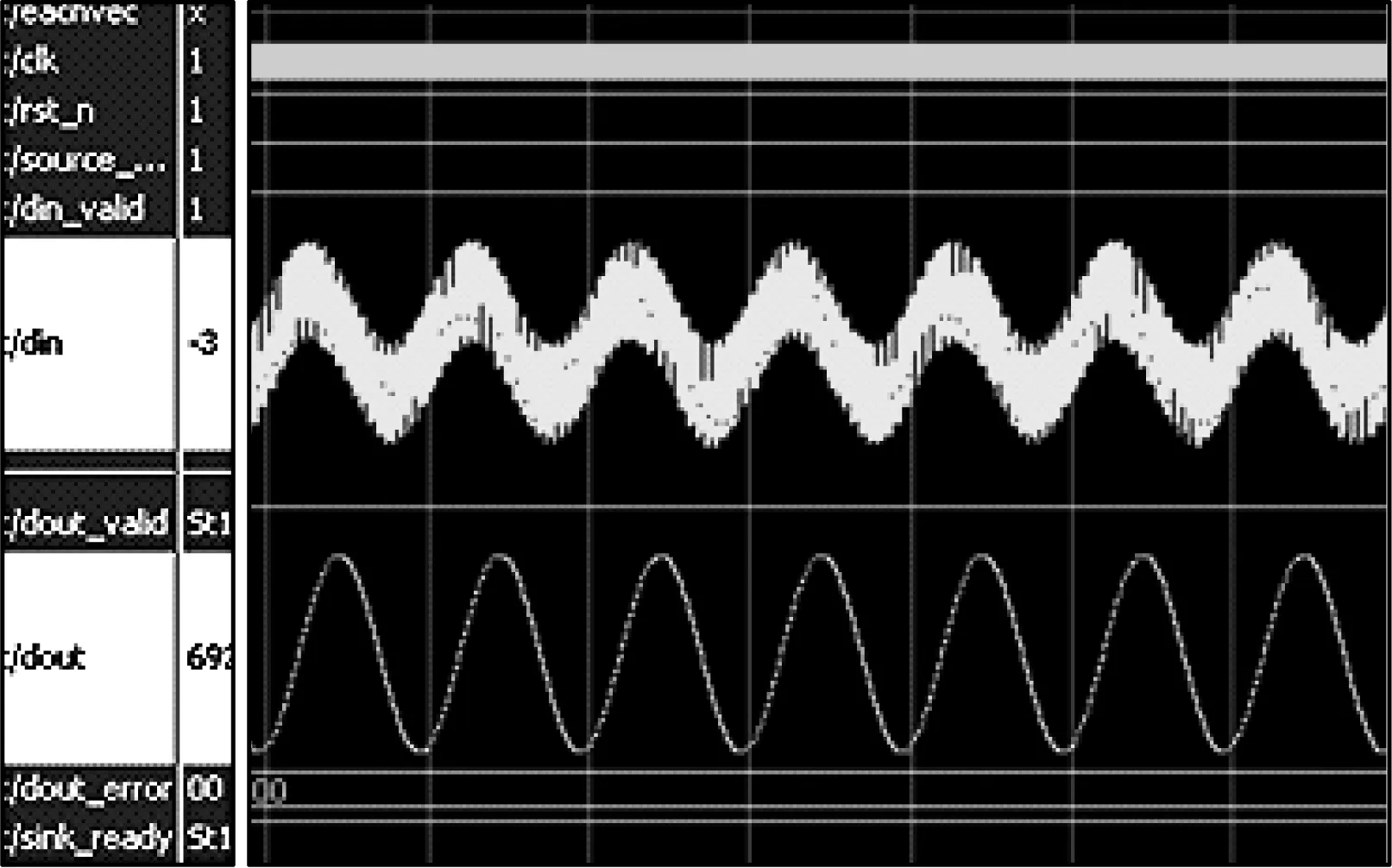

FIR濾波器的性能測試采用文獻[6]介紹的文件讀寫方法,采用Matlab和ModelSimSE聯合仿真,便于處理大容量數據。FIR濾波器輸入、輸出及參數為有符號數,輸出格式為二進制補碼形式[11-12]。為直觀顯示FIR濾波器的濾波效果,在ModelSimSE中采用模擬輸入和輸出的方式。仿真輸入、輸出波形如圖7所示。

輸入數據是50kHz和1.8MHz兩個正弦波信號的疊加信號,通過FIR低通濾波器,希望1.8MHz的信號被完全濾除,50kHz的正弦波信號完整地輸出,由圖7可知,50kHz的信號正確地輸出,設計的FIR濾波器正確。

同時對比圖2和圖7可知,采用Matlab設計的FIR濾波器和基于IP核設計的濾波器輸出的波形完全一致,也驗證了FIR濾波器設計的正確性。

圖7 基于IP核FIR濾波器的仿真輸入輸出波形

5 結束語

介紹了Matlab中使用FDATOOL工具設計濾波器的方法,給出了時域卷積運算的代碼實現,同時介紹了沖激響應和數據的比特量化方法,并給出了Matlab中FIR濾波器的濾波波形圖。本文完整地介紹了基于Altera公司FIRIP核的使用方法,并給出了完整地仿真輸入、輸出波形圖,設計的濾波器完全符合要求。采用該方法可以很好地設計和驗證項目要求的FIR濾波器。

[1] 劉東華.Altera系列FPGA芯片IP核詳解[M].北京:電子工業出版社,2014:187-193.

[2]Siruiks.無線通信的Matlab和FPGA實現[M].北京:人民郵電出版社,2009.

[3] 范紅旗,翟慶林.銳截止中頻采樣濾波器的設計與實現[J].電路與系統學報,2009,14(5):31-35.

[4] 曹振吉,何 敏.基于FPGA和Matlab的FIR數字濾波器[J].現代電子技術,2015,38(1):98-102.

[5] 喻慶華,司錫才,馮 策,等.基于IP核的FIR濾波器在新型FPGA的實現[J].彈箭與制導學報,2006,26(1):491-494.

[6] 郭 勇,陳艷玲.Viterbi-IP核糾錯性能的驗證[J].電訊技術,2012,52(10):1 640-1 643.

[7] 陳 鏡,曹芳菊.基于IP核的濾波器復用模塊的設計與實現[J].無線電工程,2010,40(4):26-30.

[8] 喻慶華,馮 策.基于IP核的FIR濾波器在數字正交變換中的應用[J].應用科技,2006,33(6):51-55.

[9] 范紅旗,翟慶林,王 勝,等.基于IP核的銳截止中頻采樣濾波器優化設計[J].電子測量與儀器學報,2008,22(1):99-103.

[10] 許金生,周春雪.基于IPCore的FIR數字濾波器的FPGA實現[J].安徽工業大學學報,2007,24(3):309-313.

[11] 郭 勇,楊 歡.RS(63,45)編譯碼器的設計與FPGA實現[J].無線電通信技術,2011,37(2):54-58.

[12] 郭 勇,何 軍.STM32單片機多串口通信仿真測試技術研究[J].無線電工程,2015,45(8):6-10.

郭 勇 男,(1978—),碩士,高級工程師。主要研究方向:調制解調、信道糾錯編解碼和無線通信中的信號處理等。

楊 歡 男,(1979—),碩士,高級工程師。主要研究方向:硬件電路設計和通信電路設計等。

Design and FPGA Implementation of FIR Filter Based on IP Core

GUO Yong,YANG Huan

(ResearchDepartmentofNorthInformationControlGroupCo.,Ltd.,NanjingJiangsu211153,China)

The paper introduces a method of how to design the parameter of the FIR filter and how to implement it in FPGA based on Altera’s IP Core.In order to achieve the capability of FIR filter demanded,the paper introduces a method of how to design the number of order ofh(n)andthetimevaluesofh(n)bothinMatlabandinIPCore,andimplementstheconvolutionoperationintimedomainbyprogramming.ThepaperalsointroducesthemethodandresultsofBitQuantificationofh(n)andinputdata.InordertovalidatethecorrectnessofFIRdesigned,thepapergivesthesimulatedinputwaveformandoutputwaveformfilteredbothinMatlabandinModelSim.ThesimulatedexperimentalresultindicatestheFIRfilterdesignedcanensuretheintegrityofsignalsinpassbandandthegoodfilteringeffectinstopband.Therefore,themethodintroducedhasthegoodapplicability.

FIR;IP Core;FPGA;time-domain convolution;waveform validation

10.3969/j.issn.1003-3106.2017.01.19

郭 勇,楊 歡.基于IP核FIR濾波器的設計與FPGA實現[J].無線電工程,2017,47(1):79-82.

2016-10-14

TN911.12

A

1003-3106(2017)01-0079-04