多核DSP的雷達數據處理平臺設計

張利平

(中國西南電子技術研究所,成都 610036)

?

多核DSP的雷達數據處理平臺設計

張利平

(中國西南電子技術研究所,成都 610036)

雷達數據處理平臺是雷達的重要組成部分,在現代雷達中通常用來分析和融合雷達信號處理回傳的目標信息,通過一系列復雜計算,將處理后的目標信息送給雷達綜顯進行顯示。給出了以TMS320C6678為核心構建硬件平臺的設計方案。通過實際測試,驗證了平臺的性能和工作的正確性。

雷達;數據處理平臺;嵌入式多核;TMS320C6678

0 引 言

現代雷達已經被賦予了新的作戰使命,不再單純地作為目標探測的工具。在雷達的衍生應用中,需要處理雷達二次信息,如速度、航跡、機型、敵我屬性、空情態勢及各種人機交互信息[1]。在某些特定的雷達應用中,可能還需要顯示數字地圖或雷達SAR圖像。要實現這些功能,就需要數據處理平臺對大量的回波信息進行復雜算法分析,并送出處理結果。TI公司推出的高性能多核DSP芯片TMS320C6678,可以構建現代雷達的數據處理平臺,其優異的性能滿足現代雷達的大型數據處理算法搭建要求。該平臺多核并行處理的優勢也可以擴展到如雷達組網、信號處理、大型數據鏈等多種應用,具有廣闊的市場前景。

1 TMS320C6678芯片介紹

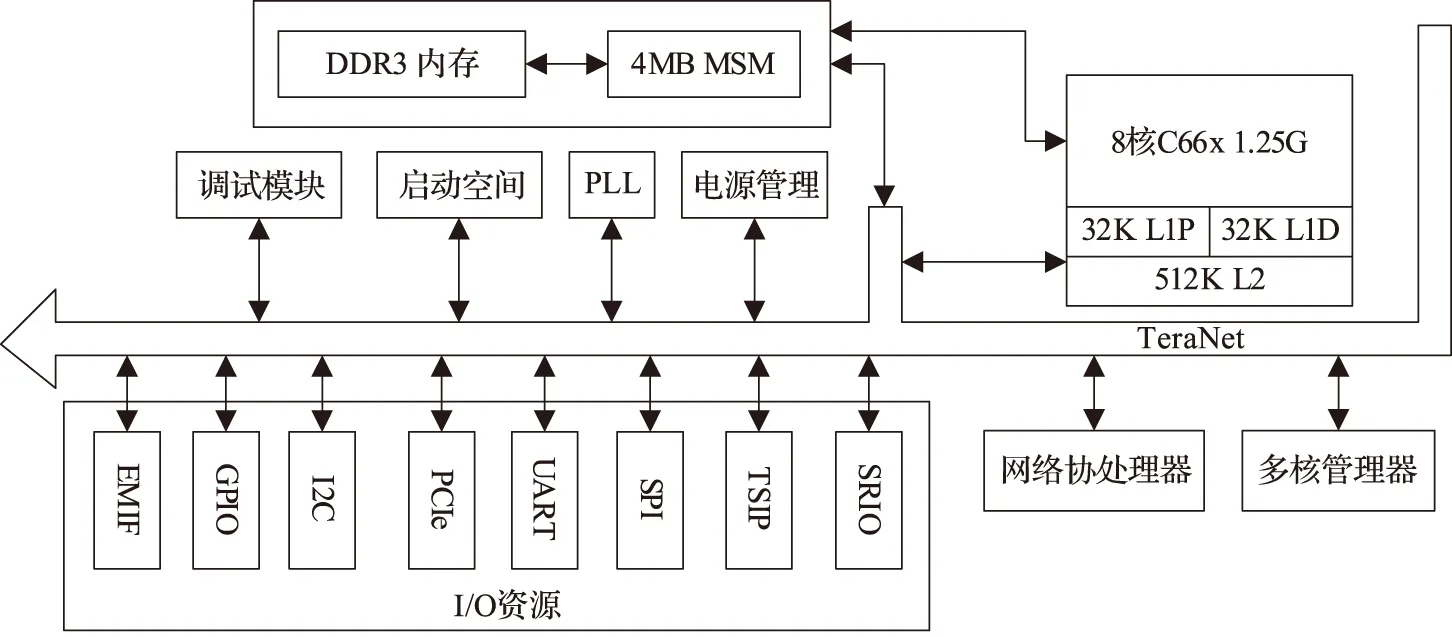

TMS320C6678是TI公司推出的高性能8核DSP芯片,采用了KeyStone架構,支持定點和浮點運算。其優勢是片內整合了豐富的協處理器、高性能I/O和大量的運算資源,內部結構框圖如圖1所示[2]。

由圖1可知,TMS320C6678是一個高度集成的多核DSP芯片,并且還具有以下特點[3-4]:

(1) 芯片集成8核DSP處理器,單核最高頻率達1.25 GHz;

(2) 采用KeyStone高性能架構體系,將協處理器和I/O均融合到DSP核中,增強了芯片的擴展性和適應性;

(3) 增強型C66x內核,融合定點和浮點處理能力;

圖1 TMS320C6678的內部結構

(4) 具備Semaphore硬件仲裁模塊和資源共享機制,有利于多核協調訪問共享資源,降低數據讀寫沖突的可能性;

(5) 豐富的外部接口功能,通過擴展后可以適應不同的接口需求。

2 平臺的硬件設計

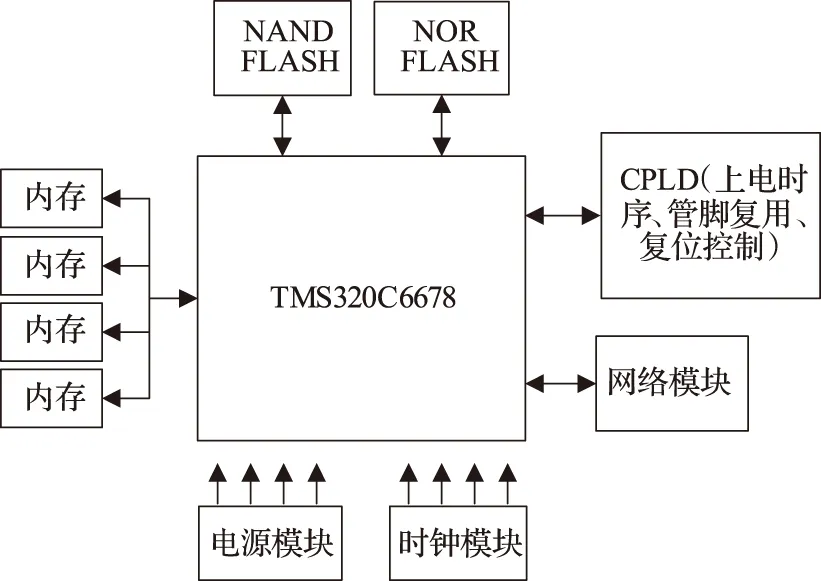

系統硬件總體框圖如圖2所示。

圖2 數據處理平臺系統搭建框圖

考慮到后續模塊的通用性和擴展性,將數據處理平臺設計為標準XMC結構,即通過最小系統的構建方式引出所有外部的接口,方便后續大系統的自由搭建。數據處理平臺的硬件設計部分主要包括電源模塊、內存模塊、網絡和存儲模塊、時序配置模塊等。

2.1 電源模塊

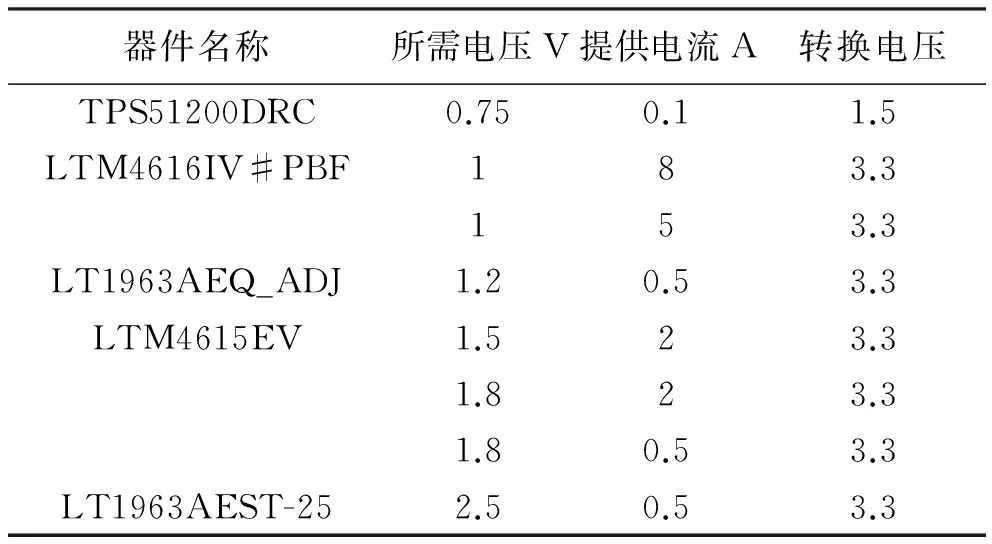

電源處理是決定硬件平臺是否穩定的重要因素之一。XMC標準架構可以給模塊提供+3.3V和+5V的電壓,因此數據處理平臺所需的其余電源均由電源轉換芯片提供。為實現相關硬件功能,數據處理平臺還需要+2.5V、+1.8V、+1.5V、+1V和+0.75V等5種電源。各電源分配如表1所示[6]。

表1 數據處理平臺電源分配表

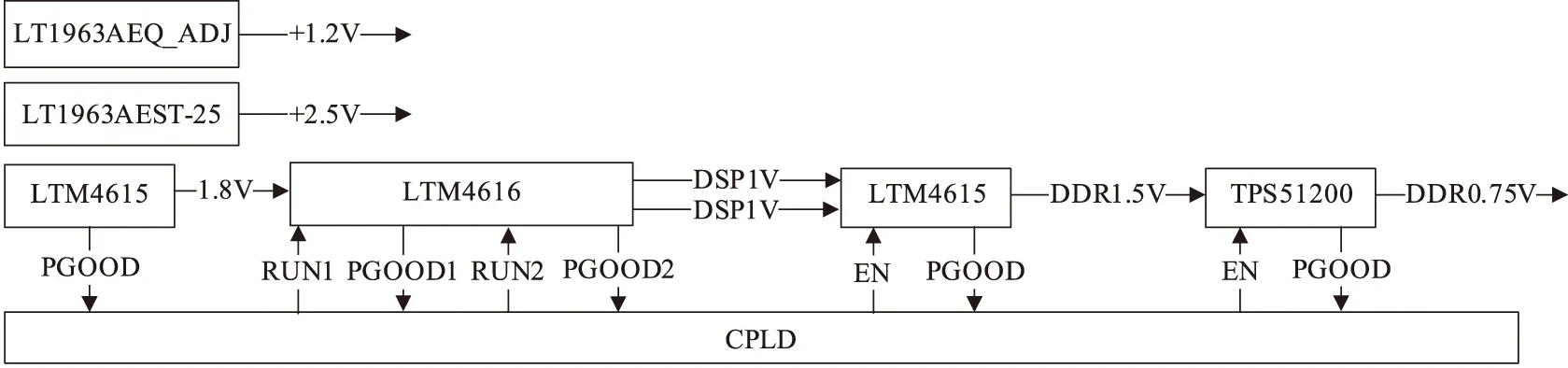

TMS320C6678啟動時對各電源的上電時序有嚴格要求。因此,將各電源的輸出穩定信號和輸入使能信號接入CPLD進行控制,保證上電后DSP能正常工作。上電時序如圖3所示。

2.2 內存模塊

DDR3即第3代雙倍數據率同步動態隨機存取存儲器,是電子設備工程聯合委員會開發的新一代內存技術標準,其I/O總線時鐘頻率范圍為800~2400 MHz。

圖3 上電時序示意圖

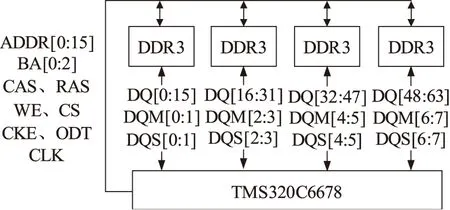

相較于DDR2標準,DDR3在功耗、工作頻率和穩定性等方面都有較大的提高。在本次設計中,采用四片美光公司的512M內存,通過級聯的方式,提供總共2G的系統存儲容量。內存模塊連接拓撲圖如圖4所示[5]。

圖4 內存模塊連接拓撲圖

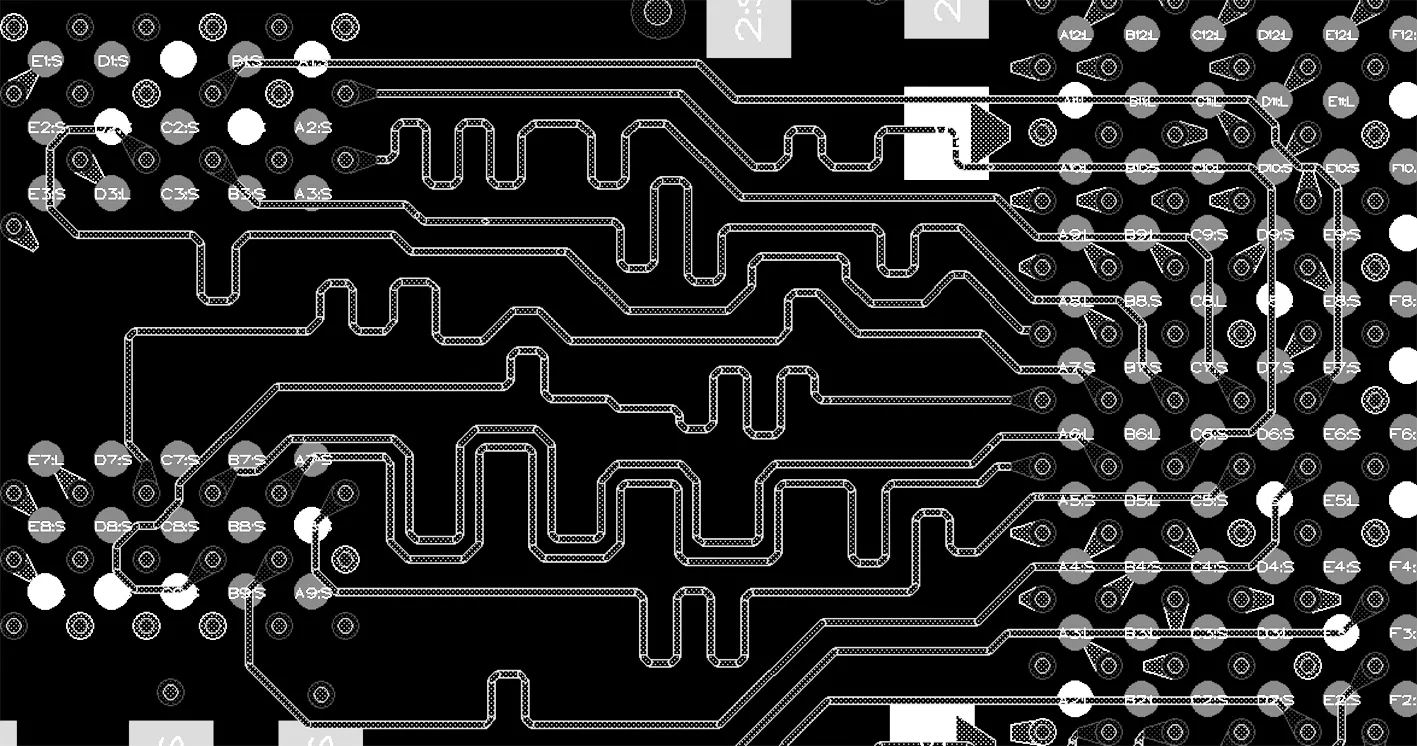

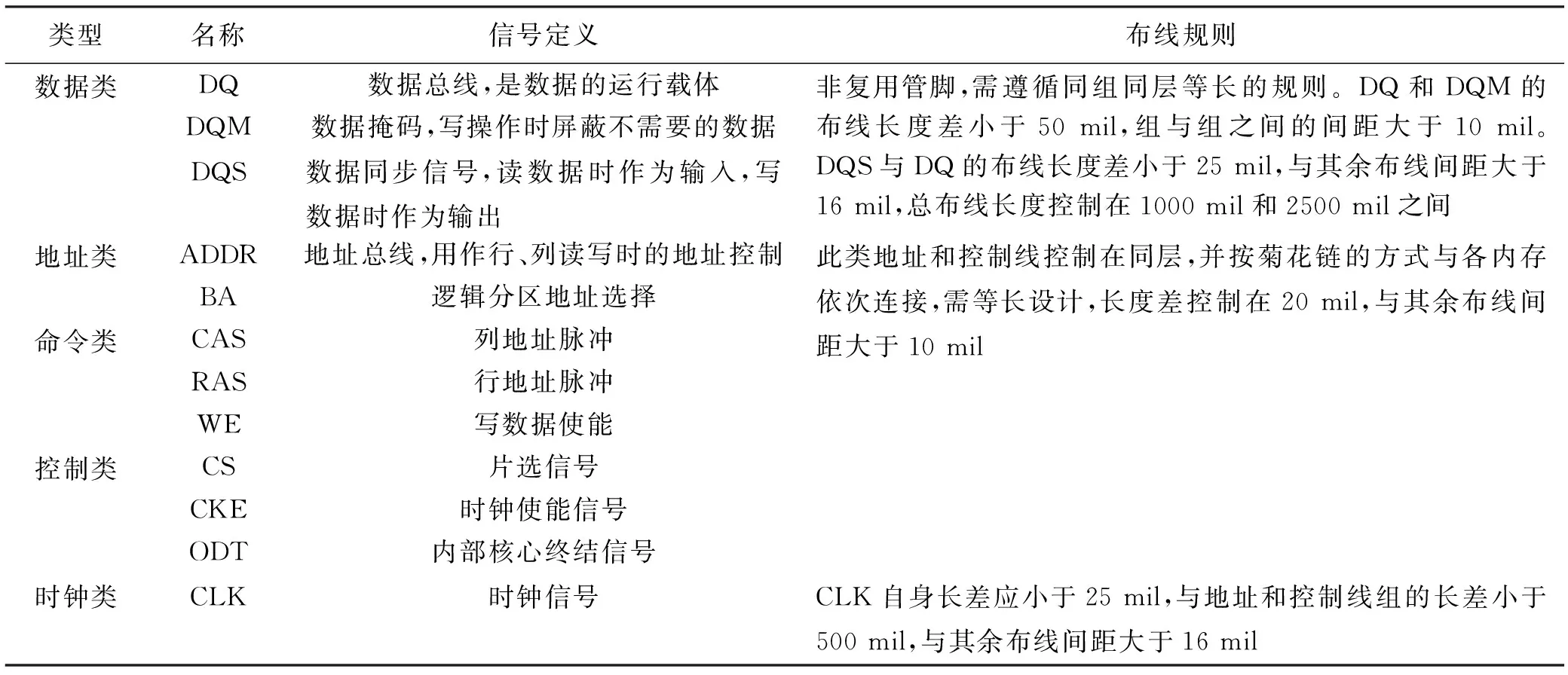

DDR3總線數據傳輸速率很高,傳輸電平低,易受到外界信號干擾,因此在設計時需嚴格遵循其布局、布線規則,保證信號傳輸質量。本次設計的布線規則如表2所示。數據組布線示意圖如圖5所示。

圖5 數據組布線示意圖

表2 DDR3總線布線規則

在DDR3應用中,需要將控制線上拉電阻到VTT,防止信號線終端產生反射。在本次設計中,考慮到印制板設計時可能產生的容差,將控制、命令和地址類信號進行RT端接(即上拉到VTT),確保信號完整性。

2.3 網絡和存儲模塊

TMS320C6678 DSP芯片自帶網絡協處理器,支持2個物理網口擴展,增強了使用的靈活性。結合MARVELL的外圍物理層控制芯片88E1111,可以搭建完整的網絡通信架構。

88E1111自帶SGMII接口,與DSP互聯時無需增加額外的驅動芯片。在本設計中,將88E1111的配置引腳接入CPLD進行控制,既節約了配置電阻的布板面積又方便了配置。88E1111需要提供一個20 MHz的時鐘輸入,因此在外部接入一個晶體。需要注意的是,與DSP互聯的數據收發差分對,需要在接收端端接一個100 nF的電容,隔離直流分量進行AC耦合。

考慮到數據處理平臺在不同雷達平臺中的功能擴展,在存儲模塊中同時使用了

NOR FLASH和NAND FLASH。NOR FLASH的容量較小,可以用來存儲系統啟動程序和部分小容量參數信息。NAND FLASH容量較大,可以存儲大量的系統參數信息并實時記錄試驗數據[7]。

2.4 時序配置模塊

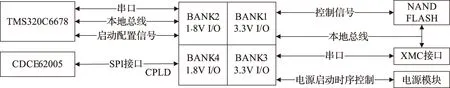

在數據處理平臺中,采用XILINX公司COOLRUNNER系列的CPLD:XC2C256-7FT256I,來做系統啟動的配置和各I/O接口的轉換,實現各種時序配置功能。該款CPLD包含4個BANK,每個BANK均可以獨立配置I/O電壓。由于TMS320C6678的I/O端口電壓為1.8 V,其余芯片I/O端口電壓為3.3 V,將BANK1和BANK3設定為3.3 V輸出,BANK2和BANK4為1.8 V輸出,這樣就省掉了由于電壓不一致而必須添加的驅動芯片,節約了布板面積,提高了系統的穩定性。CPLD模塊的連接框圖如6所示。

圖6 CPLD模塊連接框圖

3 軟件設計

TMS320C6678的8個內核相互獨立。因此,當在進行軟件開發時,為了最大限度地發揮其多核的效能,需要運用到核間同步的機制。核間同步的方式主要有以下4種[8]:

(1) 變量監聽模式:在軟件中通過監測volatile類型的變量變化情況,實現多核同步;

(2) 中斷模式:多核之間通過中斷的方式,實現同步;

(3) 事件通知模式:基于SYS/BIOS的多核同步通信模式;

(4) 消息傳遞模式:通過消息隊列的方式,在傳遞同步信息的同時,可以傳遞少量參數信息。

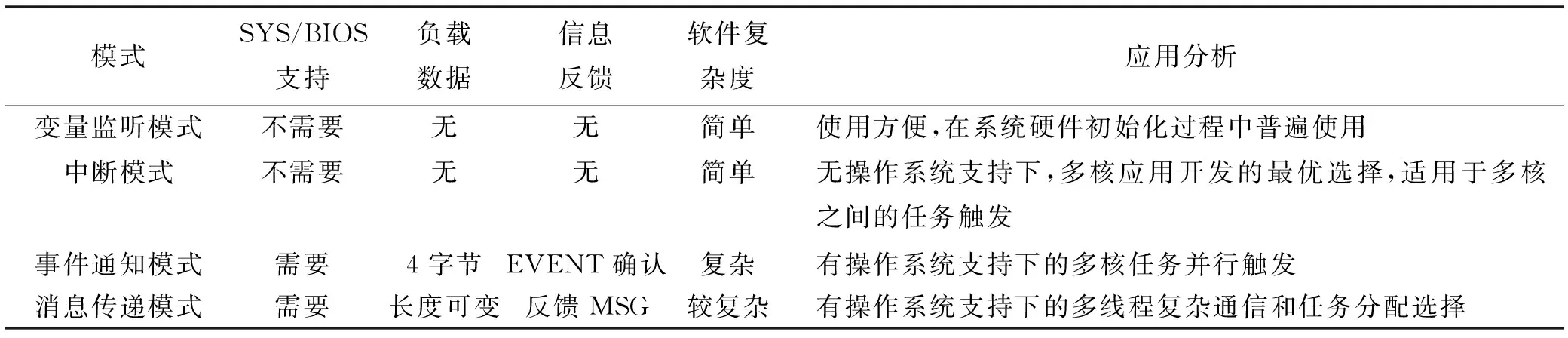

4種同步方式各有優劣,表3從幾個方面進行了比較。

表3 核間同步模式分析表模式SYS/BIOS

3.2 多核DSP軟件開發框架搭建

許諾向丁小慧坦白,自己是在結婚之后,才明白婚姻的真正價值,不是花好月圓時的錦上添花,而是他走在人生的陰暗面時,有她的扶持,當他寂寞的時候,有她愿意陪著他無所事事。是她對他的好,讓他想變得更好,也讓他愛上了她。

在多核DSP軟件開發過程中,最重要的是均衡各核之間的任務量,即通過合理的軟件框架劃分,最大限度地發揮8核的并行處理效能,以便用最短時間完成數據處理工作。雷達的設計思路不一樣,相同的數據處理算法需遵循的開發架構也不一致,并沒有固定的映射關系。以下主要通過分析兩種常用的軟件框架介紹搭建軟件框架的思路。

3.2.1 數據流框架

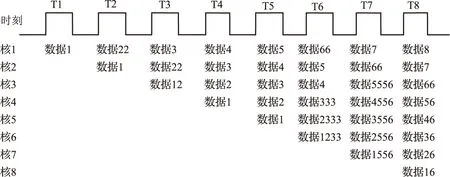

數據流框架即是流水線模式,是通過對算法處理流程的劃分讓每個核依次執行固定任務,最后一個核輸出處理結果的形式。使用這種框架,內核之間對數據的處理是有先后順序的,必須等前一個核處理完數據下一個核才能開始工作。使用數據流框架的關鍵在于算法處理時間的均勻劃分。不合適的劃分會導致某一個核數據處理時間過長,最終影響雷達系統的性能。當數據充滿流水線順序執行時,總體任務執行性能會得到較大提升。數據流框架處理流程如圖7所示。

圖7 數據流框架處理流程圖

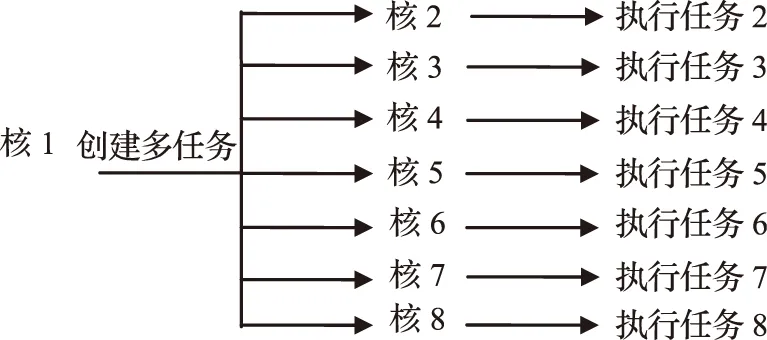

3.2.2 主從框架

主從框架即是使用其中一個核進行集中控制,創建多線程,將任務分流給其余核執行的過程。使用主從框架,必須有操作系統支持。這種方式對簡單任務是適用的。當執行復雜任務時,難點在于如何均衡各從核之間的任務執行效率。只有能保證負載均衡和共享資源能夠及時使用,才能實現整個軟件的并行工作。

主從框架處理流程如圖8所示。

圖8 主從框架處理流程圖

4 結果與分析

4.1 數據吞吐速率測試

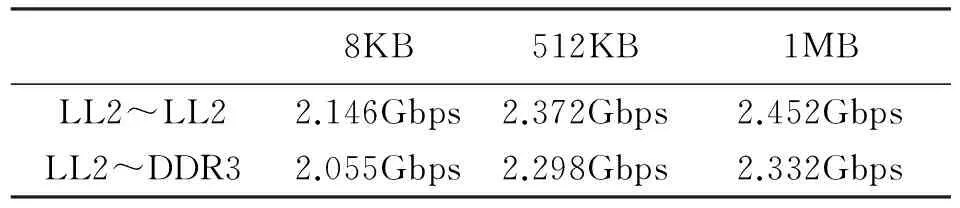

在雷達的SAR圖像處理過程中,需要在DSP和存儲器之間進行大數據的交互。數據吞吐的時間損耗即是一個關鍵指標。因此,著重對平臺大數據搬移時間進行了測試,使用SRIO高速傳輸接口。測試結果如表4所示。

表4 數據傳輸速率測試表

在測試過程中發現,負載數據越小,傳輸的速率越慢。多核之間的LL2數據傳輸速率明顯高于與外部DDR3的數據交互。因此,在實際軟件設計過程中,頻繁使用的數據應盡量在LL2之間進行交互,并盡量減少小塊數據的傳輸,提高雷達系統數據實時處理能力。

4.2 功耗測試

在8核滿負荷工作時,數據處理平臺平均功耗約為15 W。通過外接散熱片方式,傳導散熱,即可正常工作。

5 結束語

隨著現代雷達技術的飛速發展,多核DSP的雷達數據處理平臺也將成為發展趨勢。本文介紹的即是其中一種應用于雷達設備中的多核DSP數據處理平臺的設計方法。該平臺以TI公司的多核DSP處理器TMS320C6678為核心,具有高性能、可擴展和低功耗等優點。此數據處理平臺已經成功應用于某型號雷達設備中。本系統的研制成功也為開發下一代的雷達多核數據處理平臺的研究提供了借鑒。

[1] 西北電訊工程學院《雷達系統》編寫組.雷達系統[M].北京:國防工業出版社,1980:64.

[2] Texas Instruments.TMS320C6678 Multicore Fixed and Floating-Point Digital Signal Processor[M].Texas,U.S.A,2012:11-63,92-208.

[3] Texas Instruments.C66x CPU and Instruction Set Reference Guide[M].Texas,U.S.A,2012:14-20.

[4] David Bell,Greg Wood.Multicore Programing Guide[M].Texas,U.S.A,2012:11-43.

[5] Micron Technology.1GB_DDR3_X4X8X16_D1[M].DDR3 SDRAM,2010:1-10.

[6] Texas Instruments.TMS320C6000 Optimizing Compiler v7.4 Users Guide[M].Texas,U.S.A,2012:11-27.

[7] Texas Instruments.KeyStone Architecture Gigabit Ethernet(GbE) Switch Subsystem User Guide[M].Texas,U.S.A,2013:20-34.

[8] 蘇保禹.基于TI-C6678的多核DSP圖像處理系統研究[D].中國科學院研究生院(光電技術研究所)碩士學位論文,2014:41-53.

Design of radar data processing platform with multicore DSP

ZHANG Li-ping

(China Southwest Research Institute of Electronics Technology, Chengdu 610036)

The radar data processing platform, as an important part of the radar, is generally used to analyze and fuse the target information sent back from the radar signal processor in modern radars. The target information processed is sent to the terminal display console for display after a series of complicated calculation. The design scheme of building the hardware platform is given with the TMS320C6678 as the core. The performance of the platform and the correctness of the work are verified through the actual test.

radar; data processing platform; embedded multicore; TMS320C6678

2016-09-10;

2016-10-03

張利平(1982-),男,工程師,研究方向:各種嵌入式平臺的開發和顯示系統的研究。

TN957.52

A

1009-0401(2016)04-0032-05