DSP指令Cache的設計與實現

湘潭大學物理與光電工程學院 呂華智 黃嵩人

DSP指令Cache的設計與實現

湘潭大學物理與光電工程學院 呂華智 黃嵩人

為提高DSP處理器的執行效率,專門針對CPU指令處理速度與存儲器指令存取速度不匹配問題,本文通過在CPU與主存儲器之間設計了一款指令Cache,從而有效解決了上述問題。根據DSP四級流水線的特性,所設計的指令Cache采用直接映像機制;通過verilog實現指令Cache的編程,并使用ModelSim仿真軟件對指令Cache進行了仿真驗證,仿真結果表明指令Cache的效果符合預期。

DSP;指令Cache;Cache控制器

近年來,在國家的大力扶持下,集成電路產業發展異常迅速, CPU的處理速度越來越快,集成度也越來越高,然而相對于微處理器而言,存儲器讀寫速度的提高卻相對比較緩慢,兩者之間的速度差距越來越大,以至于導致瓶頸問題的產生,從而制約著系統整體性能的提高。在現代計算機體系結構中,通常在CPU和主存儲器之間插入一個容量小而速度快的存儲器來滿足性能要求,這一存儲器被稱為高速緩存(Cache)。

1 指令Cache的設計與實現

1.1 Cache的工作原理

在Cache的存儲系統中,Cache和主存儲器之間一般是用塊來進行信息交互的。因此,Cache和主存都會被分割成一些大小相同的塊,且塊的大小通常為2的冪次方字節。

當CPU需要讀Cache里面的內容時,CPU會發出一個物理地址,這個物理地址被放到主存地址寄存器中。緊接著地址變換部件會將主存地址中的塊號B轉換成Cache的塊號b,并存儲到Cache地址寄存器中。與此同時將主存地址中的塊內地址W直接作為Cache的塊內地址w裝入到Cache地址寄存器中。如果轉換成功(稱為Hit),就用此Cache地址去尋址Cache_SRAM,并且將訪問到的數據傳給CPU。反之,則稱為Cache Miss,CPU就直接訪問主存儲器,將主存儲器的內容傳給CPU,且同時將其復制到Cache_SRAM中。在拷貝的過程中如果發現Cache已經滿了,那么就需要采取某種替換策略將一些不常用到的塊替換出來,以此來裝入新調入的塊。由于程序具有局部性的特點,當發現Cache失效時,我們就將失效內容對應的整個塊都裝入Cache中,從而減少Cache的失誤率。

1.2 指令Cache的基本結構設計

Cache容量的大小與映射的方式存在著一定的關系,被稱為2:1 Cache的經驗規律,即容量為N的直接映射Cache與容量為N/2的二路組相聯Cache有著幾乎相同的缺失率[2]。其中強制性失效率并不會受Cache容量的影響,然而容量失效率則與Cache的容量成反比關系;同時強制失效和容量失效有一個共同點,就是他們都不受相聯度的影響。如果Cache容量過大,就會導致Cache的命中時間過長,進而會影響到CPU的執行效率;沖突失效率是隨著Cache相聯度的增加而下降。但是并不是說Cache的容量越大越好,當達到一定容量的時候,如果再繼續增加Cache的塊大小,反而會導致Cache的命中率降低。

在綜合考慮了性能、功耗、面積等方面的因素,最終把指令Cache的容量大小設計為8KB,塊大小為16個字節,采用直接映射。指令Cache主要由以下幾個模塊構成:ICache_CTR控制模塊、I Cache_SRAM模塊、TAG_SRAM模塊,其中TAG_SRAM、ICache_ SRAM可以稱為數據部分,ICache可以稱為控制部分,在數據部分進行查找操作,將查找結果(hit或miss)送到控制部分,由控制部分依據查找結果進行下一步的操作。

由于直接映像是一種最簡單,也是最直接的方法,所以在本款32位的DSP內核中,指令Cache采用直接地址映像的方式。其直接映像就是指主存中的一個塊在Cache中具有唯一的位置。當CPU訪問該主存塊時,利用塊索引查找對應的目錄表項,如果其中保存的標識與主存塊Tag相同,且"Valid"位為1,則說明該位置上的Cache塊即是所要找的塊。假設主存的塊號為I。Cache的塊號為J,則可按照一種循環分配的原則確定I、J之間的對應關系:

J=I mode M

其中,M為Cache的塊數。

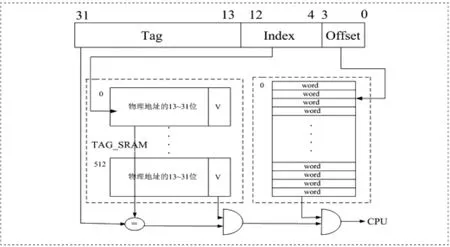

在本系統中,Tag表示存儲器的區號,index表示塊索引,offset表示塊內偏移,通過每塊中的offset就可以找到塊中的每一個word。

TAG_SRAM總共有512個目錄表項,每個表項包含Tag位和Valid位,其中取物理地址的高19位作為Tag位。ICache_SRAM存儲的是指令Cache中的內容,ICache_SRAM中的4個表項(每個表項是一個word,其中一個word包含4個Byte)與TAG_SRAM中的一個表項組成ICache目錄表中的一個line,比如:TAG_SRAM的第1個表項與ICache_ SRAM中位于4~7的word組成ICache目錄表的line1.當要取指時需查找TAG_SRAM,利用要讀取指令地址的4~12位的值作為索引查找TAG_ SRAM,得到TAG_SRAM對應的表項,將該表項返回給ICache模塊,后者據此判斷ICache是否命中。指令Cache的基本結構圖如圖1所示。

圖1 指令Cache的基本結構圖

1.3 指令Cache的實現

將指令Cache結構和Cache控制器進行整合后,采用verilog編程來實現指令Cache。ICache控制器的主體是一個狀態機,有三個狀態:IDLE、IC_FETCH和IC_MISS。處理器復位的時候處于IDLE狀態,當需要取指時會進入IC_FETCH狀態,在此狀態下又分以下三種情況:①當Cache命中時,則直接從Cache取得指令返回給處理器②如果Cache未命中,則從內存中讀取指令,且將指令讀入Cache中③如果指令所在的內存塊被禁止,則同樣從相應的內存塊中讀取指令,并回到IDLE狀態。

而ICache的存儲體TAG_SRAM和ICache_SRAM直接用Memory Compiler生成。

2 指令Cache的仿真與驗證

指令Cache的仿真在ModelSim中進行,例化程序的機器碼由CCS運行產生,再將機器碼導入存儲器中。在系統上電復位的時候,指令Cache未被使能,ICache_SRAM中還沒有數據,所以在初始化Cache之前,CPU取指是需要從內存中獲取,該指令在流水線執行階段用了多個時鐘周期,仿真結果如圖2.當Cache初始化完成之后,并且指令Cache被使能,此時CPU取指則可從Cache中直接獲取,此時在流水線執行階段只占用一個時鐘周期。仿真結果如圖3所示。