用于超聲導波測溫技術的數據采集系統設計

中北大學電子測試技術國防重點實驗室,儀器科學與動態測試教育部重點實驗室,山西太原 030051

一、引言

超聲測溫是聲學測溫的一部分,它是一種利用接觸測溫方法來進行溫度測量的新技術[1],這種技術可以用于被測物體處于溫度變化快,而且溫度較高的如先進火箭、導彈等的惡劣環境中[2-3]。美國于上世紀九十年代已經將超聲測溫技術應用于核反應堆堆芯溫度測試當中[4],國內在此方面尚屬開始階段,華北電力大學安連鎖等人成功將12kHz氣體超聲溫度計安裝于200MW機組鍋爐上進行調試[5-6]。

目前國內距離用聲學法實現溫度場實時在線監測尚有很大差距,所以對于更高頻率的細線超聲測溫時的信號實時采集與傳輸的研究顯得尤為重要。本文提出了一個高速、低成本的細線超聲測溫數據采集系統,以較低的成本實現了較高的采集速度,并將采集數據實時傳送至計算機,彌補了傳統采集方案的受限于器件性能的不足。

二、超聲測溫原理

本文所設計的數據采集系統主要應用于細線超聲測溫技術[7]。由于聲波在固體中傳播時,聲速的溫度靈敏度隨溫度升高而增大,因此這種溫度計更適于測量高溫[8]。而聲波在細線傳播時的速度與材料的楊氏彈性模量,材料的密度有關。但由于缺少彈性模量與溫度間的精確的函數關系,因此聲速與溫度間的關系主要靠后期實驗標定系統來標定[9]。由于細線的長度已知,所以超聲聲速與溫度間的關系就可以演化為超聲在細線中的傳播時間與溫度的關系。

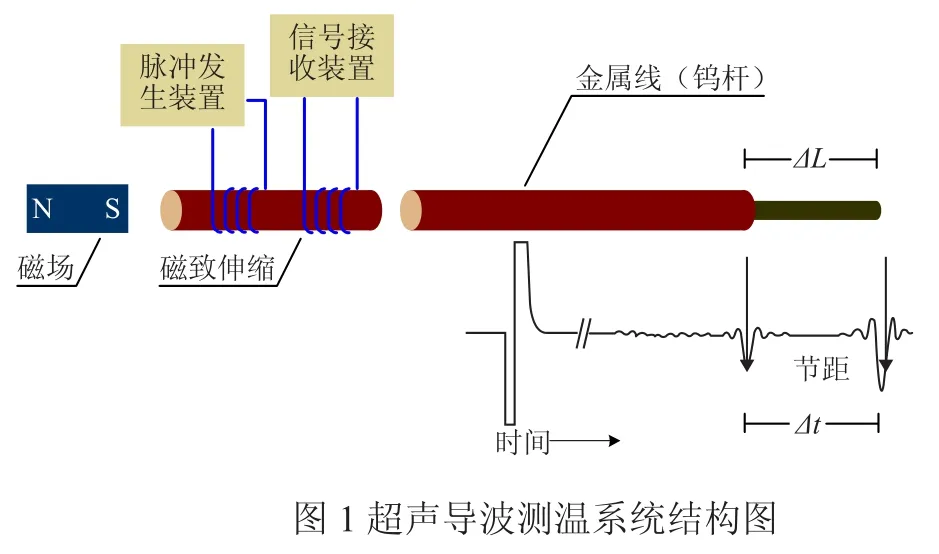

三、高速采樣硬件方案

高速采樣硬件方案如圖1所示,超聲導波測溫系統主要包括脈沖發生裝置,耐高溫金屬線(鎢桿),超聲接收裝置(限幅、放大、模數轉換電路、系統控制電路、USB接口電路以及上位機等構成)。超聲接收裝置核心是由FPGA構成。本文主要討論超聲導波測溫技術中高速采集的關鍵技術與實現方法,設計A/D轉換單元和FPGA邏輯控制單元。

從理論上講,該方案是根據超聲回波信號的波包寬度、頻率特征來設計的,系統采用兩塊高速A/D轉換器對同一個超聲換能器的信號進行采集,兩塊A/D采樣時鐘信號相位相差90°。而采集速率取決于超聲信號的頻率。當超聲信號的頻率越高、單個超聲回波波包的長度越短時,就能夠在鎢桿前端制作更短的節距,為更快響應速度的超聲測溫帶來可能。

四、FPGA 時序邏輯設計

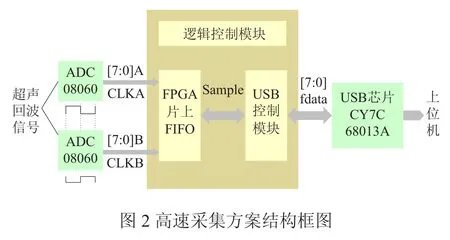

根據超聲導波信號具有重復性和高頻的特性,設計中采用了與相位合成技術相似的高速采集方案[10]。方案的結構框圖如圖2所示。

該高速數據采集方案包括兩塊高速A/D轉換器、FPGA邏輯控制單元,USB接口電路。其工作原理是,將同一個傳感器同時接入兩塊高速A/D轉換器。當采樣觸發同步脈沖到來時,采樣邏輯控制器即FPGA邏輯控制單元產生A/D轉換器時鐘信號CLKA、CLKB。兩塊A/D轉換器在時鐘信號的驅動下進行邏輯轉換。轉換結果由FPGA的邏輯控制下寫入FPGA片上FIFO模塊,并將FIFO模塊中緩存的數據逐步通過USB接口電路傳送至上位機。采樣過程中,CLKA與CLKB的邏輯相反,即在一個周期內,兩片高速A/D分別采集一次信號,相差半個周期。

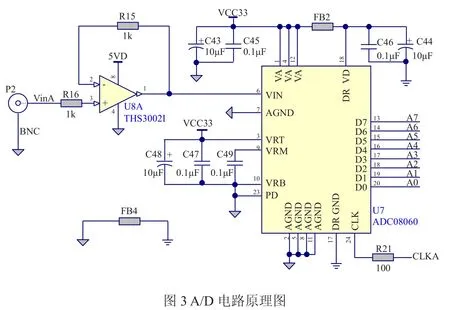

1、A/D采樣控制

A/D轉換芯片采用8位的ADC08060高速A/D芯片,其最大采樣速率為60Msps。由于更高的采樣頻率對電路整體設計要求十分苛刻,設計缺陷帶來的采集信號毛刺等問題會對采集到的超聲信號帶來影響,所以設計中A/D采樣系統中使用20MHz采樣時鐘。A/D芯片的采樣時鐘信號由FPGA給出。兩塊芯片的輸入信號連接在一起,在信號輸入ADC08060之前,由高速與門芯片THS3002I構成電壓跟隨,使得超聲換能器與A/D轉換芯片阻抗匹配。當開始采集超聲回波信號時,邏輯控制模塊發出的ADC時鐘信號CLKA、CLKB信號進入,兩時鐘信號相位差為90°。其中單片A/D電路原理圖如圖3所示。

2、采樣結果高速緩存

本模塊是由FPGA自帶的資源通過IP核生成。由A/D轉換芯片采集的超聲信號數據直接送入FIFO中。生成的兩個FIFO模塊,對兩片A/D轉換芯片采集的數據分別進行存儲。兩塊FIFO的時鐘信號與A/D轉換芯片的時鐘信號同步,做到高速緩存,位寬為8 bits,緩存深度為1024 words。由于兩片FIFO分別存儲兩片A/D信號,而傳輸到USB端的信號需要合并為同一信號。這里在FPGA上讀信號實現了乒乓操作,從兩片FIFO上交叉逐一讀出信號,即為原始信號。

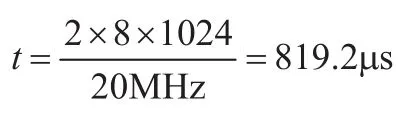

在單片20MHz采樣速率下,兩塊存儲器可存儲的時域信號的時間長度為:

若超聲波在磁致伸縮材料中的傳播速度為4900m/s,在鎢中的傳播速度為5700m/s,按最低速度計算,并以超聲換能器所激發出的縱波在磁致伸縮材料中傳輸并反射為例,該容量的存儲器可使用的最大材料長度為:

由于目前所使用的細線超聲傳感器長度遠小于該長度值,因此設計的緩存器容量能夠滿足要求。

3、USB與FPGA通信接口

USB控制模塊采用Cypress公司的EZ-USB FX2LP系列的低功耗單片機CY7C68013A。它的外圍接一個I2C芯片AT24LC64,用來存放固件程序。FPGA與CY7C68013A通過異步FIFO方式連接,接口時鐘USB_IFCLK也由FPGA給出,時鐘頻率與FPGA相同。當FIFO讀信號發出時,過半個周期讀數據,將數據傳送至上位機。

五、軟件設計

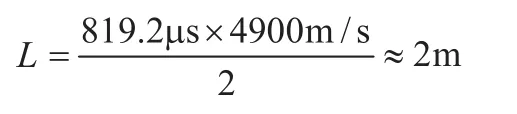

本系統的上位機編程采用Visual Studio開發平臺,主要包括系統初始化、USB數據讀取、采樣深度等數值傳輸模塊。具有繪圖、坐標偏移、設備檢測、設備刷新、通道選擇、采樣深度設置、門前延時、觸發間隔等功能。設置了單點觸發和循環觸發兩種觸發方式,同時也可以保存輸入到上位機的數據,保存波形圖片等功能。上位機界面如圖4所示。上位機通過USB接口與單片機進行通訊,將采樣深度,門前延時,通道選擇,觸發間隔等控制字傳輸至FPGA,來控制FPGA的采集模式。FPGA將采集到的數據傳輸至軟件,軟件將采樣到的數據點繪圖,形成超聲信號波形。

六、實驗過程及結果分析

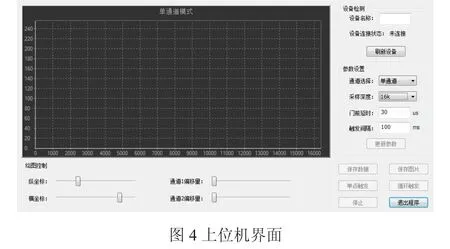

實驗使用直徑為3mm,長度為604mm的磁致伸縮材料作為超聲波導,在磁致伸縮材料上加工一個深度為1mm,軸向長度為1mm的凹槽,節距長度為300mm。給系統上電后,通過上位機設置采樣深度、門前延時以及觸發方式。將超聲機理裝置激發出的超聲調節為400kHz,開始采集超聲回波信號。實驗共采集常溫以及100℃~600℃溫度范圍內每個溫度點三組數據,溫度間隔為100℃。

圖5所示為單次200℃時高速數據采集系統所采集到的超聲縱波信號。第一個波包為起始聲波,第二個小的信號為凹槽回波,第三個波包為端面回波。

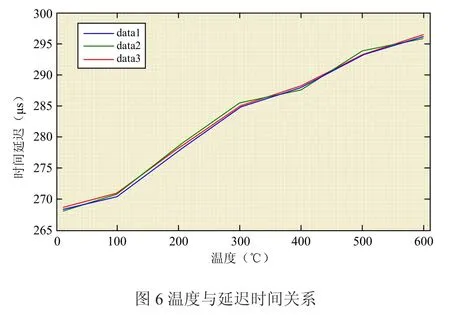

為便于分析,對所得到的三組數據使用MATLab 進行描點分析,得到如圖6所示為三組溫度與延遲時間關系圖。可以看出超聲回波信號延遲時間隨溫度的升高而相應的增加,在12℃~600℃的區間內,超聲回波時間與溫度有較好的線性關系。但由于高溫爐在100℃~1200℃之間時,不確定度為2℃,且控制精度為1℃,假設爐內溫度不確定度在2℃時,超聲波傳播的標準傳播時間可取三組數據的平均值。實際實驗中高溫爐的溫度漂移以及沒有通過精確算法對回波信號進行計時所帶來的人為因素不可避免。

七、結論

文中提出了一種用于超聲導波測溫技術超聲回波信號采集系統的設計方法,該超聲回波信號采集系統能夠以40Msps采樣速率采集超聲回波信號,滿足實際檢測時信號采集的要求,且采樣深度、門前延時和觸發方式可調,能夠在超聲導波測溫技術中用于更高頻率的超聲回波信號的數據采集,可用于更高精度的超聲導波測溫技術當中,而上位機的數據保存與波形圖保存功能使得后期的數據處理過程大大簡化,提高檢測效率。