基于FPGA的LCD顯示控制系統的設計

徐暢

渤海大學工學院

?

基于FPGA的LCD顯示控制系統的設計

徐暢

渤海大學工學院

本文主要介紹了關于LCD的視頻控制芯片設計方案,介紹了系統功能的實現,以及FPGA的實現原理,LCD驅動原理,解決了DSP,LCD和FPGA,之間的協同合作的難題。

LCD FPGA LCD驅動

隨著電子工程的不斷發展,嵌入式系統的應用不斷擴展,實現人機信息相互交互的界面已經是社會的趨勢。通過研究發現以往的發光二極管已經無法滿足市場的需要。發光二極管的顯示控制部分比較簡單,功能太少,無法對復雜的信息進行顯示,而且控制起來也不方便。相于是LCD液晶顯示器應運而生,代替了傳統意義上的發光二極管,并且LCD在智能儀器的應用極為寬廣。

很多的LCD是靜態顯示的,LCD的控制器大部分是以單片機為主,并且只能進行顯示而不能實現實時交互。程序在執行的過程中只能一步一步進行,不能進行多任務并發進行。本論文是基于FPGA的LCD顯示控制,硬件描述語言選擇的是Verilog,SPARTAN系列選擇的是XC2S50。通過Verilog進行語言文字的顯示和控制。

1 LCD的概述

液晶顯示的LCD做為一種目前比較流行的平板顯示器件,它的形成是在電場存在的情況下從而導致液晶材料的位置進行了改變,最后透光性能進行了遮蔽。

根據商品的形式不同可以將LCD分為以下幾種:

1.1液晶顯示模塊

該顯示模塊簡稱為LCM,該模塊由三部分組成,分別是IC驅動,組裝線路板和其它之類的商品。

1.2液晶顯示屏

顯示屏通常又可以稱為LCD屏,該屏中的設備驅動程序是由使用者自己設計的。

根據LCD顯示的形式不同,可以分為以下幾種:

(1)單色顯示。

顧名思義指的就是只有白色和黑色兩種顏色,要么背景是黑色的,文字是白色的,要么背景是白色的,文字是黑色的。兩種顏色相互間隔。

(2)彩色顯示。

其中的彩色顯示又可以分為兩種,單彩色以及多彩色,并且這個多彩色中還分為真彩色以及偽彩色,他們的區分是根據顯示的顏色總數進行的,8到32色的稱為偽彩色,而256種顏色的稱為真彩色。

LCD的器件分為TN,STN和TFT三種型號,這三種型號的性能是不斷提高的,同時相對著相關的成本也就會增多。單色LCD制作中通常選擇的型號是STN和TN兩種,真彩色的LCD通常選擇TFT。

LCD的顯示離不開由LCD控制組成的驅動電路,這是LCD實現顯示功能的首要前提,該基本的驅動電路是由背光電路,震蕩電路以及供電電路等組成的。LCD的LCD的驅動程序中往往采用的是匯編或者C語言進行編程,這些驅動程序通常涉及到的有初始化,管理和數據處理程序。

2 FPGA的概述

隨著信息時代的到來,工程領域的不斷發展,可編程邏輯技術在電子工程領域的應用越來越廣,一些新型的嵌入式產品的不斷誕生,表明現代的工程技術將會不斷的走向系統化,集成化以及電子化的發展道路。

FPGA是Field Programable Gate Array的縮寫,從英文名稱介紹可以知道指的是現場可編程的門陣列的意思,FPGA是以GAL,PAL和EPLD為發展基礎的,在系統設計中得到了廣泛的應用,其特點是系統的功耗比較低,邏輯容量的密度比較大。目前生產研發FPGA知名度比較高的公司主要有Lattis公司,Altera公司和Ximlinx公司等等。同時FPGA的前進目標是軟件開發,工具開發和工藝器件方向這兩個方向。FPGA在20世紀90年代進入了發展的黃金時代,2000年可控端口的數量相比于1990年增加了將近200倍。FPGA的硬件語言大體分為VHDL和Verilog HDL這兩種。FPGA在發展的初步階段使用的就是VHDL,而Verilog語言的前身是從C語言來的,因此大部分的編程者更傾向于用VHDL語言進行編程,VHDL的發展歷程悠久,所以語法規范性,結構性都比較強,功能比較強大,Verilog語言的發展時間還不是很長,所以語法掌握起來比較容易,比較適合入學者。

FPGA模塊部分擁有很多的功能,如下所示:

(1)產生驅動時序。因為不同類型的LCD,其顯示面板上的刷新頻率也不同,所以相應著他的分辨率參數也不相同。參數不同也就會導致產生不同的時序。所以FPGA電路模塊的核心功能是如何使得時序的驅動程序是正確的。

(2)FPGA芯片中還包括了調節亮度,調節對比度等等。FPGA選擇主要是以器件的功耗,性能,速度等因素進行選擇。

3 LCD的驅動

3.1驅動分類

(1)靜態驅動

靜態驅動的基本原理是在相對應的一對電極間連續外加電場或者是連續不加電場。其中驅動的波形指的是當同相時液晶上沒有電場,當反向是時液晶的上面就會添加一個矩形的波形。當這個添加的矩形波形的電壓比液晶所設置的閥值還要高的時候,此時LCD就可以認為是選通的狀態了。

(2)多路驅動

當電極是沿著X和Y的方向形成矩陣的時候,根據順序依次把選通的波形給X電極,Y電極上施加的選通波形或者是非選通的波形和X電極上是同步的。

從多路驅動的原理中分析可以知道,電壓會施加給選通相素也會施加給非選通的相素,為了實現選通的相素受選通電壓的控制,非選通的相素受非選通的電壓控制,LCD在光電性能方面的閥值必須要越大越好。

根據系統的要求,本論文中選擇LCD液晶顯示的器件是MTG-F32240X,該器件的像素是320*240,LCD的器件型號是FSTN,顯示的方式是圖形。

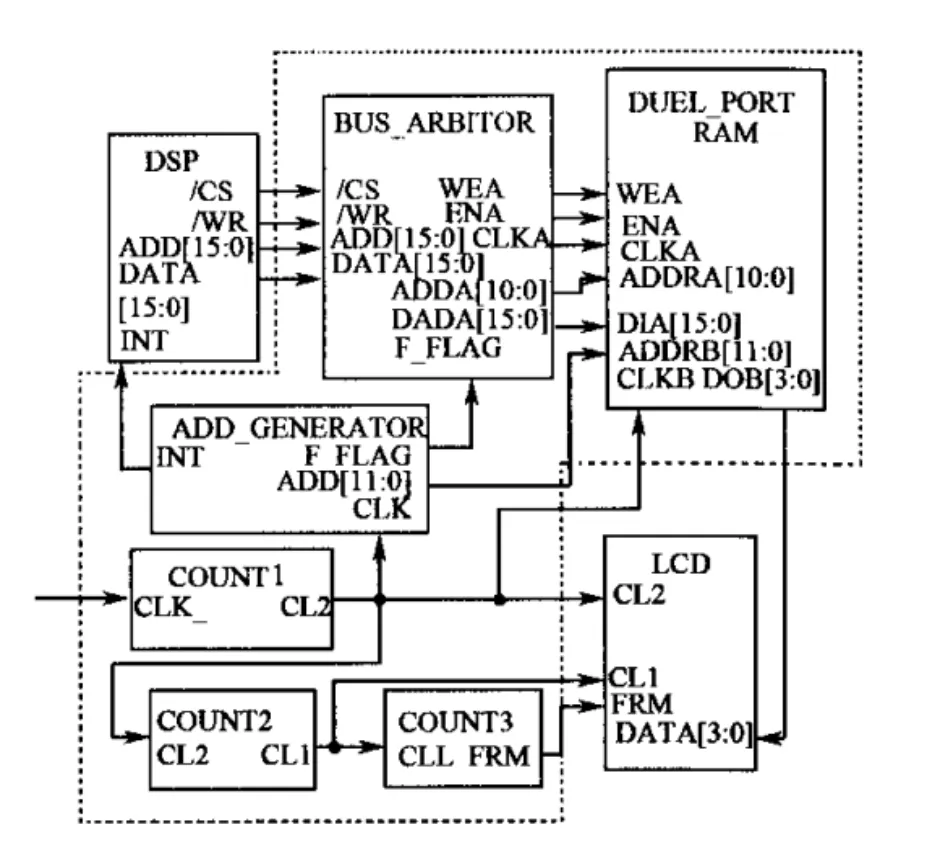

圖1 LCD接口時序

3.2LCD顯示驅動原理

該類型的液晶顯示器的接口時序中所用到的驅動信號為CL1,CL2和FRM,目前該信號的工作頻率可以參考如下:CL2=1.28MHz,CL1=16KHz,FRM=66Hz。LCD的驅動過程主要是首先移位脈沖CL2發出80個后,緊接著發出行頻脈沖CL1,當CL1發出累計到240個后FRM信號就會跟著發出,當FRM信號發出結束后,這個過程是不斷的進行循環,循環結束后液晶的顯示控制過程也就結束了。接口時序圖如圖1所示。

4 選擇顯示緩存區的存儲介質

顯示數據以及處理數據的相關性不能太高,必須盡可能降低,可以通過把數據緩存的設備加入到系統設計中,從而讓主處理器擺脫了操作上的單一性。目前數據緩存區的介質主要有兩類,分別是FPGA內部雙口和SRAM。本文采用的是FPGA內部雙口RAM作為緩存區的存儲介質。因為如果采用SRAM,可編程資源損耗過多,而且系統的穩定性受控制單元的直接影響。

該系統選擇了前者作為存儲介質的考慮因素,主要體現在:1、數據顯示的連續性得到了實現;2、完成了16bitsDSP與LCD 4bits的數據格式的相互轉化。本系統的顯示數據緩存是2Kbytes的存儲單元。

5 基于FPGA的LCD驅動器實現

LCD的驅動實現離不開驅動信號CL1,CL2以及FRM。緩存區端口地址是驅動信號決定的,當顯示數據之前需要把中斷數據的請求提交給DSP,然后DSP收到請求后就就繼續進行下一幀數據的傳送。

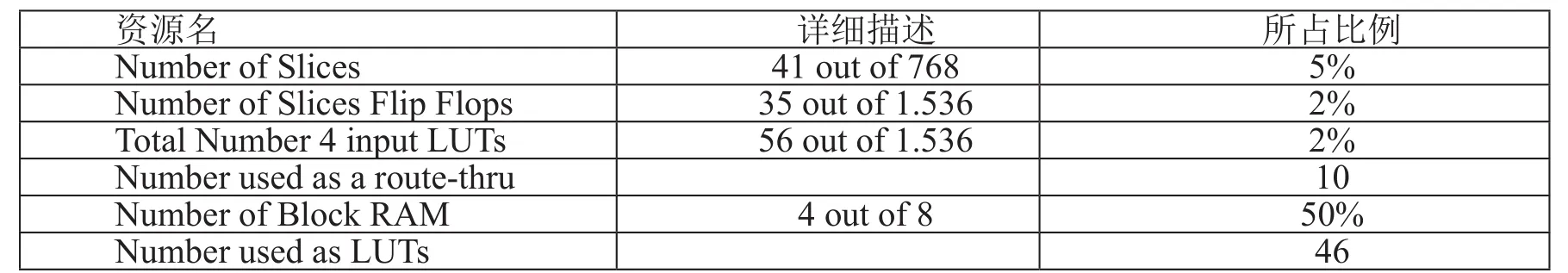

圖2 LCD驅動結構圖

從圖中可以看出,當地址是在E00H之后時幀的數目就會發生改變,BUS-ARBITOR單元專門是記錄幀的數目,接收到幀數目后中斷傳送的通知就會停止。緩存BUS-ARBITOR單元的顯示是通過DSP進行刷新實現的。

由于定時中斷的原因,所以DSP數據處理部分需要進行打斷,通過資源占有率來指明部分功能對其他流程的影響情況。資源占有率用POC表示,是中斷一次響應的時間ti與中斷兩次的時間tii之間的比值,如公式(1-1)所示:

這個模塊采用了VHDL描述語言,硬件資源占用情況如表1所示。

6 結語

本論文實現了基于FPGA的LCD顯示控制器,介紹了LCD的相關理論知識,LCD的驅動原理以及FPGA的實現原理。本文論述了通過結合DSP。FPGA以及LCD的相互結合可以增強主要器件的工作性能,為工作的順利完成提供了保證,也為軟件硬件的設計提供了方案。

[1]周鵬,李圓圓. 基于FPGA的LCD液晶動態顯示驅動程序的設計[J].電子質量,2014(11): 34-42.

[2]廖超平.基于FPGA的信號發生器按鍵LCD模塊設計[J].科技資訊,2013 (26): 1-2.

表1