一種IRIG-B碼解碼器的設計與實現

陳 偉,王 宇,余飛俠,范曉東

(安徽四創電子股份有限公司,安徽 合肥 230031)

?

一種IRIG-B碼解碼器的設計與實現

陳偉,王宇,余飛俠,范曉東

(安徽四創電子股份有限公司,安徽合肥230031)

針對現有靶場儀器組串行時間碼解碼器解碼精度低、工作穩定性差等問題,將微處理器與現場可編程門陣列相結合,提出一種新的解碼器實現方案:采用最新的片上系統控制器,在其內部配置了微處理器系統及可編程邏輯單元;串行時間碼碼元識別由相應的硬件邏輯單元控制,保證已識別的秒脈沖邊沿精準;微處理器系統控制已識別的時間碼流的解碼及輸出,由此節省了硬件資源、提高了解碼效率;最后通過現場運行及儀器監測證明該方案串行時間碼解碼精度和穩定性優于現有解碼技術,其授時精度能夠滿足時間同步的要求。

片上系統控制器;現場可編程門陣列;微處理器;靶場儀器組串行時間碼

0 引言

美國靶場間儀器組(inter-range instrumentation group,IRIG)提出了靶場儀器組串行時間碼(B type format of IRIG,IRIG-B)[1],廣泛應用于時間信息傳輸系統中。IRIG-B碼具有世界通用、接口標準化、適用于遠距離傳輸等特點。在我國,工業控制、通信、氣象、航天、電力系統測量與保護等領域的測試設備均采用IRIG-B國際時間標準作為時統設備的時間同步標準[2-3],并制定了相應的國軍標。目前國內的IRIG-B解碼采用的核心控制器大都為現場可編程門陣列(field-programmable gate array,FPGA),資源消耗量大、解碼精度低、工作效率和穩定性差;因此需要有由更高效的控制器、有效的解碼算法實現即插即用、授時精度高及運行穩定的新型解碼器。SmartFusion2系列芯片是Microsemi公司的最新65 nm工藝的片上系統產品,,是基于Flash架構FPGA發展而來,內部集成166 MHz的Cortex-M3硬核處理器,不占用FPGA的邏輯資源,能夠為用戶提供高安全性、高可靠性及超低功耗等性能[4-5]。本文方案采用SmartFusion2作為解碼器核心控制器,將FPGA和微處理器Cortex-M3優勢相結合,實現高精度授時和高可靠性的時統設備IRIG-B碼解碼器。

1 IRIG-B碼簡介

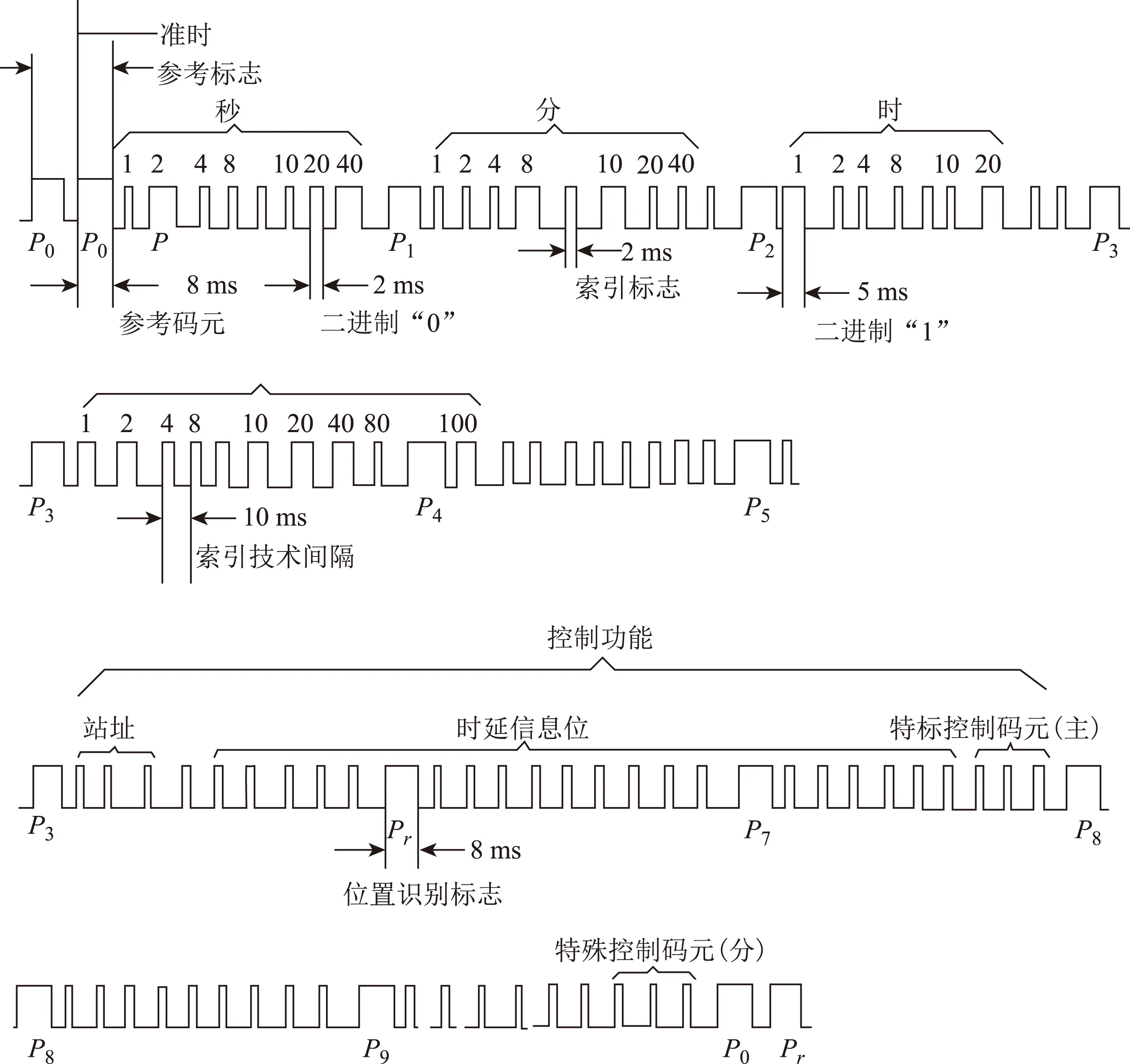

IRIG-B碼是一種串行的時間格式碼[6-10],DC碼為IRIG-B碼的直流碼,DC碼的幀周期為1 s,由100個碼元組成,每個碼元10 ms,碼元寬度有8 ms、5 ms和2 ms 3種,分別代表碼元P(位置識別標志或基準碼元)、二進制的1以及二進制的0,如圖1所示。為了便于傳輸和提取B碼中的信息,每10個碼元中有1個位置識別標識,分別稱為P1、P2、…、P9、P0。幀參考標志是由位置識別標志P0和相鄰的基準碼元Pr組成的,Pr的前沿即是每幀的準秒時刻,也就是從該準秒時刻起,按秒、分、時、天等時間信息進行編碼,最終形成DC碼,如圖2所示。

圖1 DC碼碼元圖

圖2 IRIG-B(DC)碼信號波形

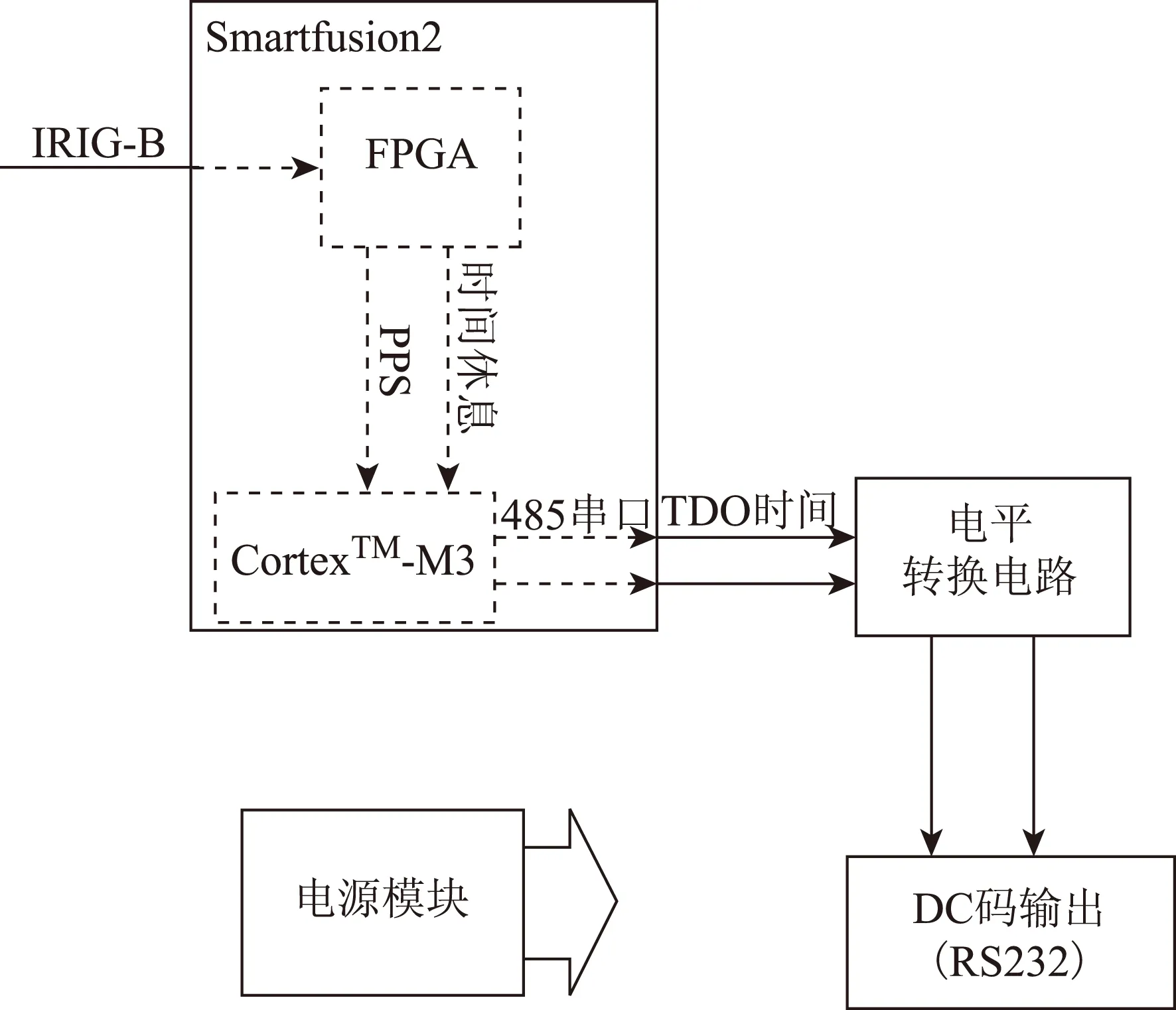

2 硬件電路設計

IRIG-B碼信號解碼器的整體硬件電路設計框架如圖3所示,這里的SmartFusion2在其內部配置了FPGA和Cortex-M3硬核處理器。

圖3 硬件電路設計框架

首先將標準的IRIG-B碼信號作為SmartFusion2的輸入信號,這里SmartFusion2采用Microsemi公司的M2S010芯片;接著在SmartFusion2中,先通過FPGA接收輸入信號IRIG-B碼,識別出秒脈沖(pulse per second,PPS)和對應的二進制碼元,將1個PPS送入Cortex-M3微處理器,將對應的二進制碼元送入雙端口的隨機存取存儲器(random access memory,RAM),Cortex-M3微處理器根據輸入的1個PPS同步讀出FPGA中RAM里二進制碼元,并進行解碼;根據IRIG-B碼協議提取出對應的時間信息,然后將其轉換成字符格式的實時時間常數(time of data,TOD)信息;同時TOD信息被送到Cortex-M3微處理器的串口輸出腳,進入電平轉換電路,從而將TOD信息直觀顯示到電腦串口調試助手上。這里采用芯片MAX3232SOP對TOD信息進行驅動并轉換成匹配的電平信號。

此外,整個硬件電路設計中,還需要電源模塊,以滿足各芯片對供電電壓的需求,分別需要電壓為+5 V、+3.3 V;這里采用電源轉換芯片LT1963ES8以完成+6.5 V到+5 V的轉換,集成電路LT1963EST-3.3以完成+5 V到+3.3 V的轉換。

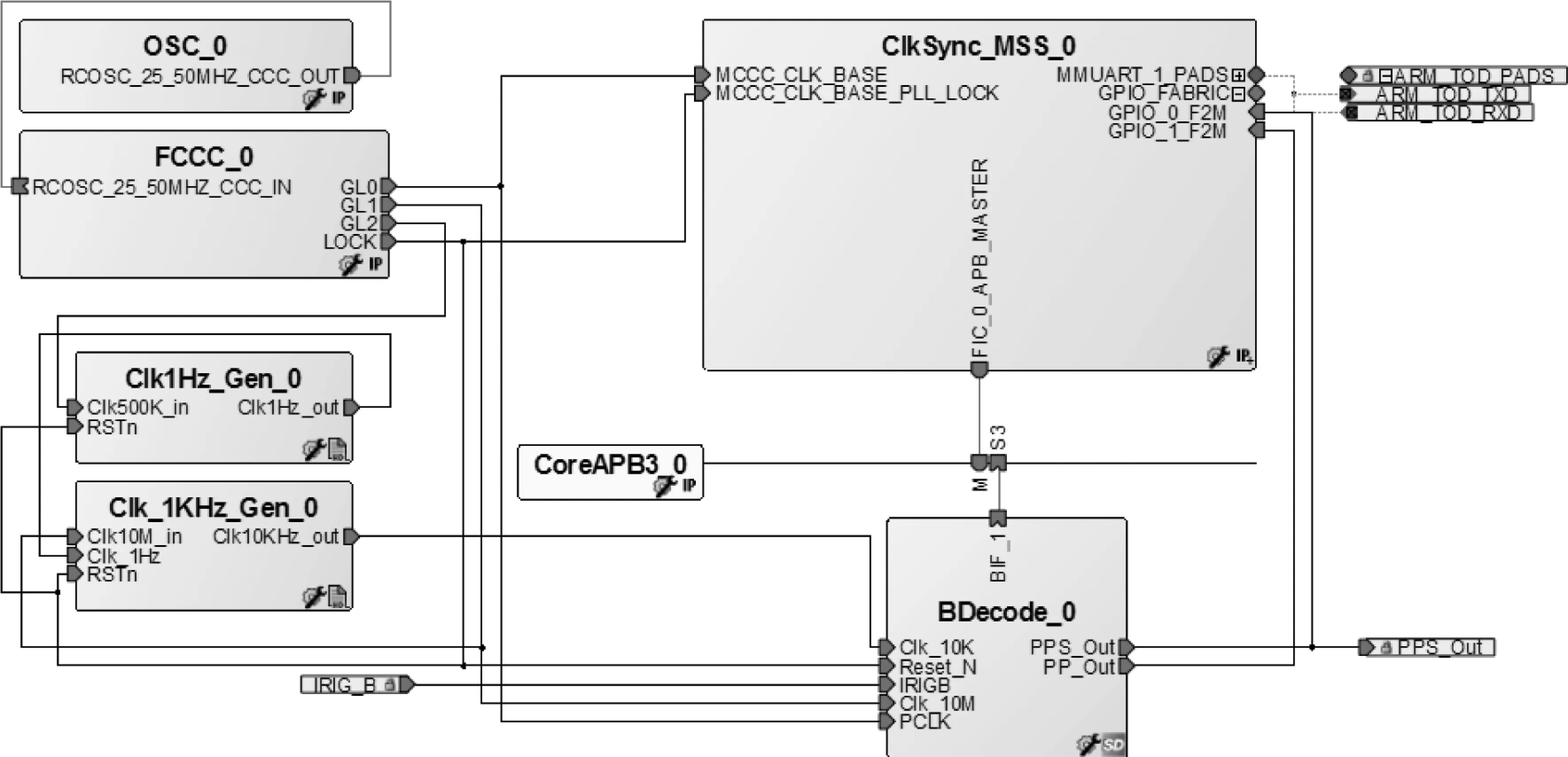

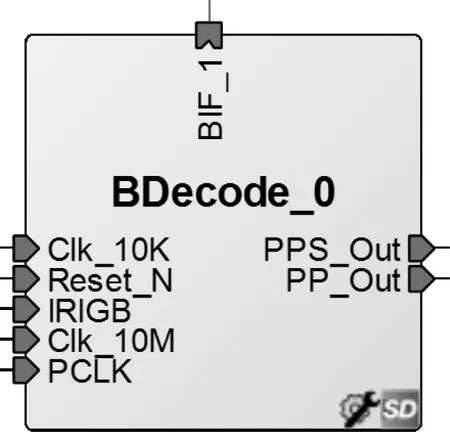

3 軟件程序設計

IRIG-B碼信號解碼器的軟件設計主要是基于FPGA及Cortex-M3微處理器系統(microcontroller subsystem in SmartFusion2,MSS)而完成,如圖4所示,其中FPGA主要負責MSS的構建、IRIG-B碼中1個PPS和對應碼元識別及碼元存儲的程序設計,MSS主要負責讀取存儲器中對應碼元并解碼輸出的程序設計等。

圖4 總體軟件設計程序

3.1IRIG-B碼解碼方法簡述

根據IRIG-B碼波形,在本設計中每1 ms視為1 bit,有脈寬為高電平1,否則為低電平0,則IRIG-B碼中3種碼元“P”“1”和“0”分別用二進制表示為1111111100、1111100000和1100000000,即十六進制0x3fc、0x3e0和0x300。則一幀IRIG-B碼為100碼元即為1 000 bit二進制碼流。

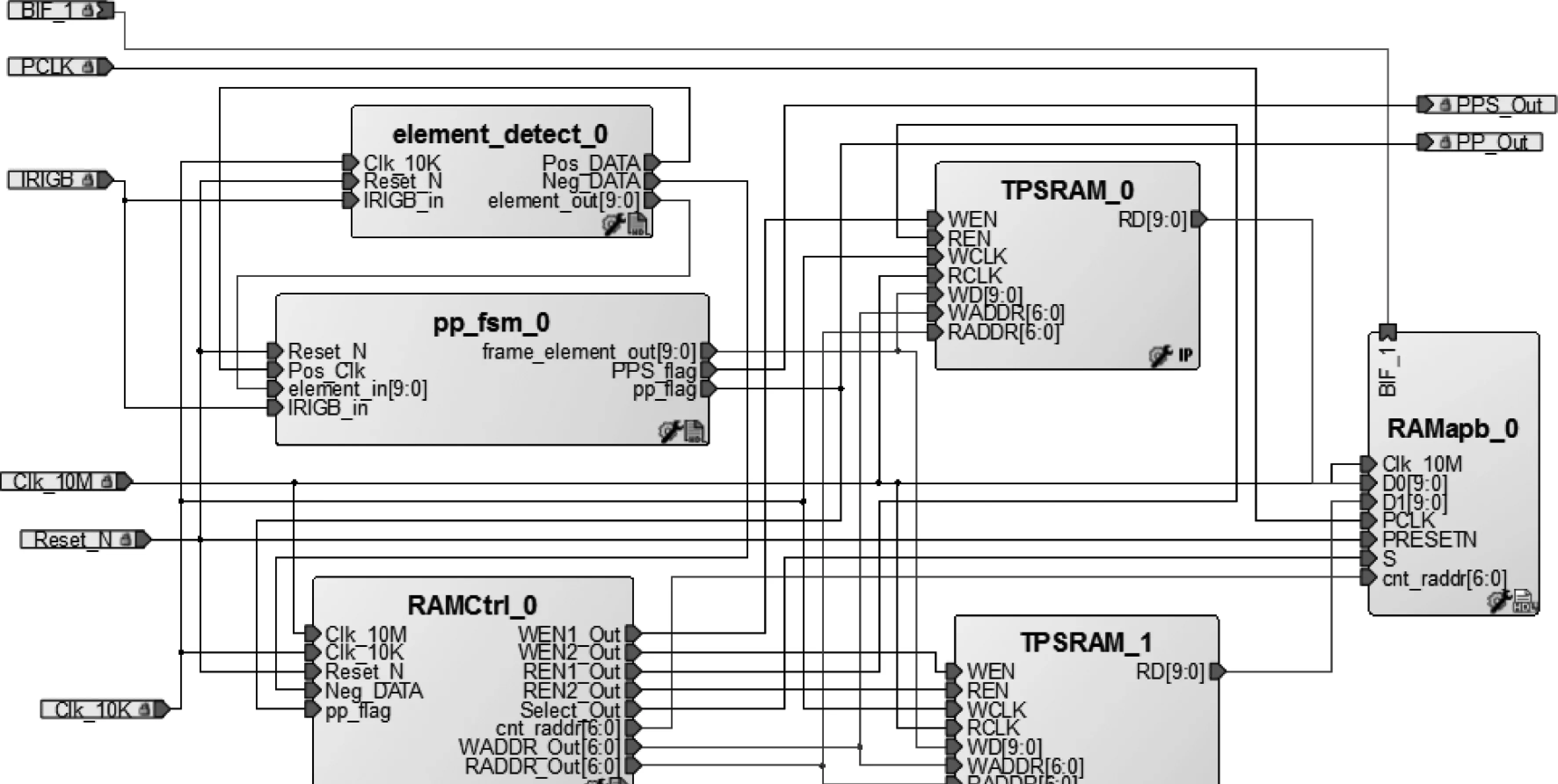

首先通過FPGA識別以上3種碼元,并得出幀參考標志PP_Out;其次根據PP_Out和IRIG-B碼上升沿開始計數,計滿99,則其后相鄰的IRIG-B碼上升沿為準秒時刻PPS_Out,即為同步的1個PPS;同時,根據PP_Out開始提取此幀的100碼元并轉換成1 000 bit碼流,并存入雙端口RAM中,FPGA程序如圖5、6所示;MSS根據準秒時刻標志PPS_Out產生中斷,讀出FPGA中RAM中1 000 bit碼流,并進行解碼,根據IRIG-B碼協議,提取出對應的時間信息并轉換成字符格式的TOD信息,并將此TOD信息通過串口發送出去。

圖5 IRIG-B碼解調核的FPGA程序

圖6 IRIG-B碼解調核的FPGA內部程序

3.2FPGA程序設計簡述

在FPGA里完成的程序設計主要有以下幾個方面:

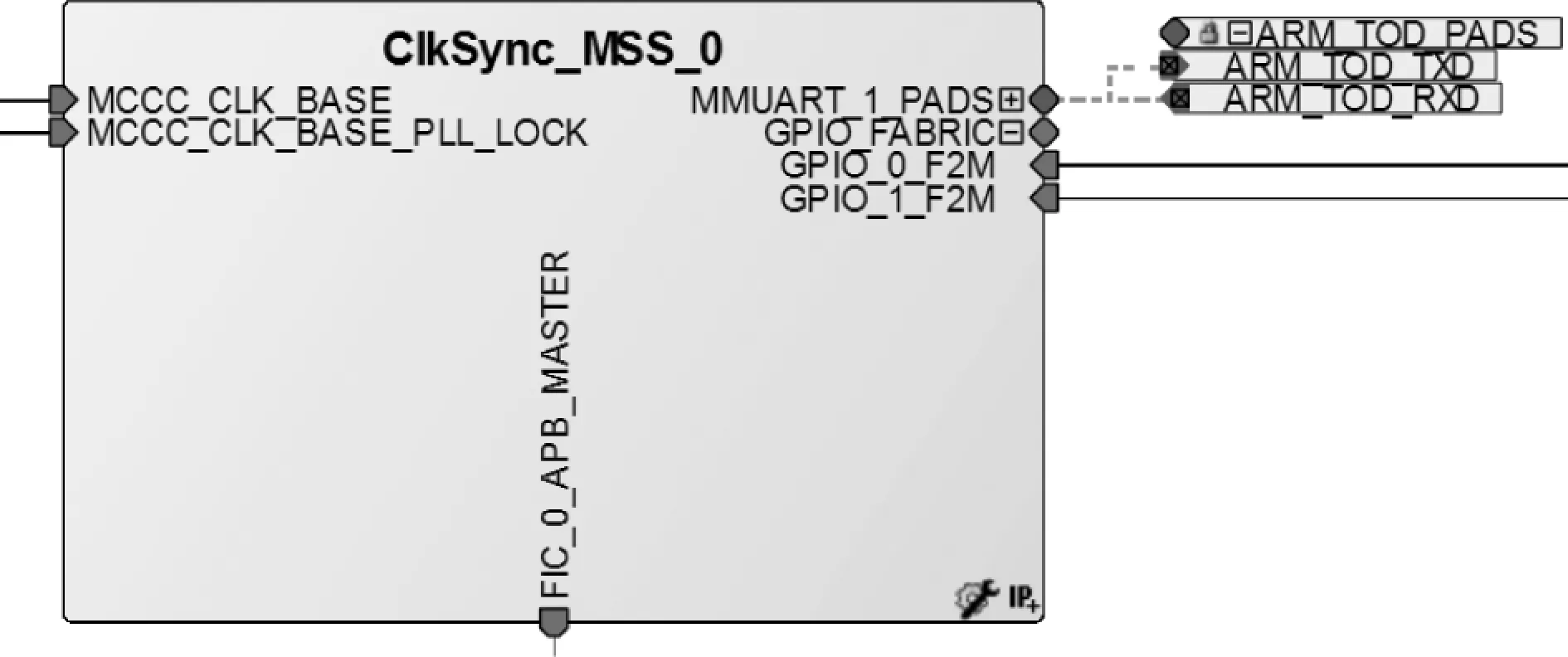

1)設計鎖相環、復位電路。從而給FPGA程序里各個設計模塊和微處理器系統MSS提供參考時鐘與復位。2)構建MSS。包括中央處理器、通用輸入輸出(general purpose input output,GPIO)模塊、串口通信模塊、外圍總線(advanced peripheral bus,APB)等,如圖7所示。

圖7 Cortex-M3微處理器系統MSS的FPGA程序

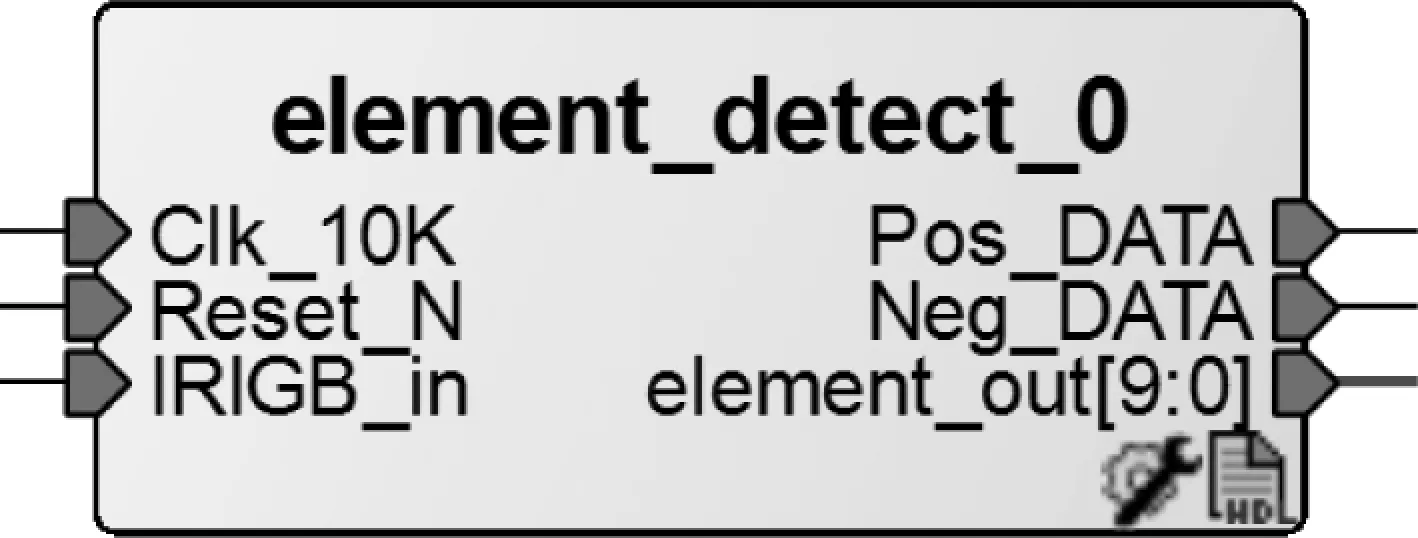

3)定制碼元識別模塊。主動識別IRIG-B碼中3種碼元“P”“1”和“0”,并分別用二進制表示為111111100、1111100000和1100000000,即十六進制0x3fc、0x3e0和0x300;同時主動識別IRIG-B碼的上升沿和下降沿。

圖8 IRIG-B碼元識別模塊的FPGA程序

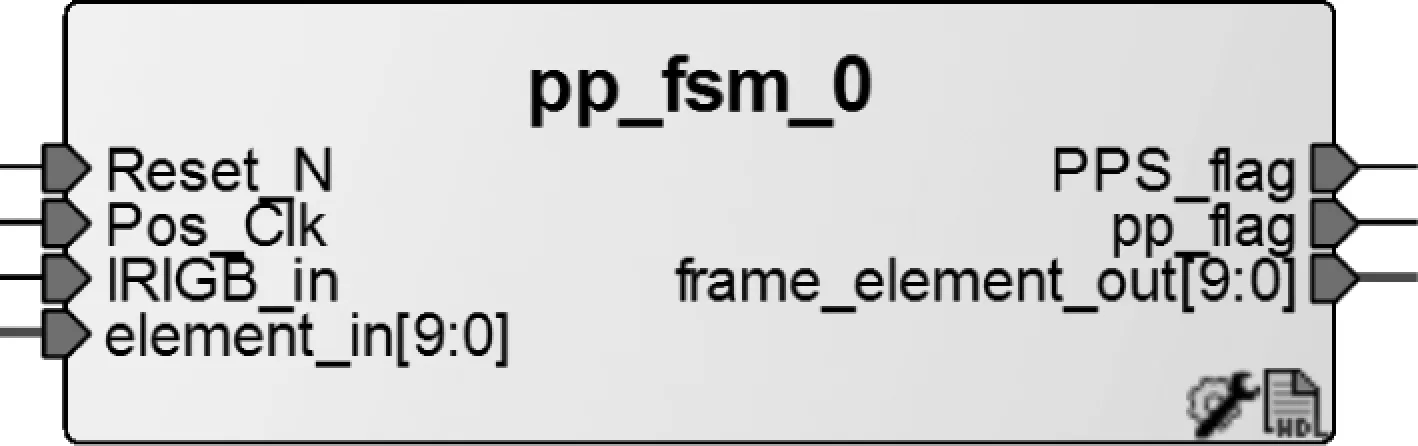

4)定制IRIG-B碼解碼模塊。根據輸入IRIG-B碼的上升沿Pos_Clk和二進制碼元element_in,可主動識別IRIG-B碼的幀參考標志PPFlag;當識別出PPFlag的同時,自上升沿Pos_Clk來,輸出二進制碼元,以得到完整的一幀IRIG-B碼的二進制格式;當識別出PPFlag的同時,根據輸入的IRIGB_in上升沿開始計數,當計滿99,下一相鄰的IRIGB_in上升沿即為準秒時刻標志PPSFlag,即為同步的1個PPS。

圖9 IRIG-B碼解碼模塊的FPGA程序

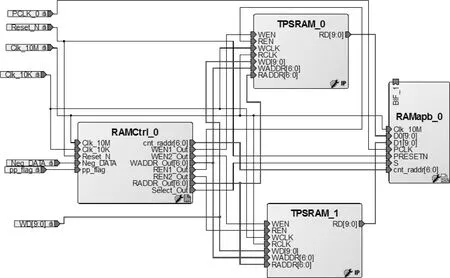

5)定制雙端口RAM模塊。從FPGA解碼模塊輸出的二進制碼流被寫進RAM模塊里,MSS通過APB總線從RAM模塊中讀出對應的二進制碼流。在這里,FPGA程序采用了乒乓操作,即寫RAM_0操作的同時進行讀RAM_1操作,而寫RAM_1操作的同時,進行讀RAM_0操作,如此循環操作,如圖10所示。RAM寫時鐘為10 kHz,寫字長為10 bit,而RAM讀時鐘為10 MHz,讀字長為10 bit;其中,RAM控制程序通過幀參考標志PPFlag來控制RAM_0、RAM_1的讀寫切換,通過10 kHz控制RAM寫地址,通過10 MHz控制RAM讀地址。

圖10 雙口RAM讀寫模塊的FPGA程序

3.3MSS程序設計簡述

在微處理器系統MSS里完成的程序設計,主要有以下幾個方面:1)對MSS進行初始化。配置一個GPIO端口作為中斷引腳,映射來自FPGA中識別出的1個PPS中斷;再配置一個GPIO端口作為中斷引腳,映射來自FPGA中識別出的幀參考標志PPFlag中斷;配置一個APB總線主模塊,讀取FPGA中解出的IRIG-B碼流;配置一個串口通信模塊,發送已解出的TOD信息。2)當幀參考標志PPFlag中斷到來時,通過APB總線開始讀取FPGA中RAM里的IRIG-B碼元并進行解碼,得到秒、分、時、日、月、年等時間信息并保存在內部的一個結構體類型變量中。3)當秒脈沖中斷到來時,開始向串口發送已解出的時間信息,格式為:

$TOD,時分秒,日,月,年*checksum/r/n

4 實驗與結果分析

基于SmartFusion2芯片方案設計中FPGA部分采用Libero SoC v11.0設計軟件,用硬件描述語言(verilog hardware description language,Verilog HDL)實現設計,Cortex-M3微處理器系統MSS部分采用Microsemi SoftConsole IDE v3.4編程軟件設計,IRIG-B碼信號由上海申貝公司的時間同步裝置輸出。根據本設計方案,接入IRIG-B碼信號,系統上電,測試結果如圖11所示。

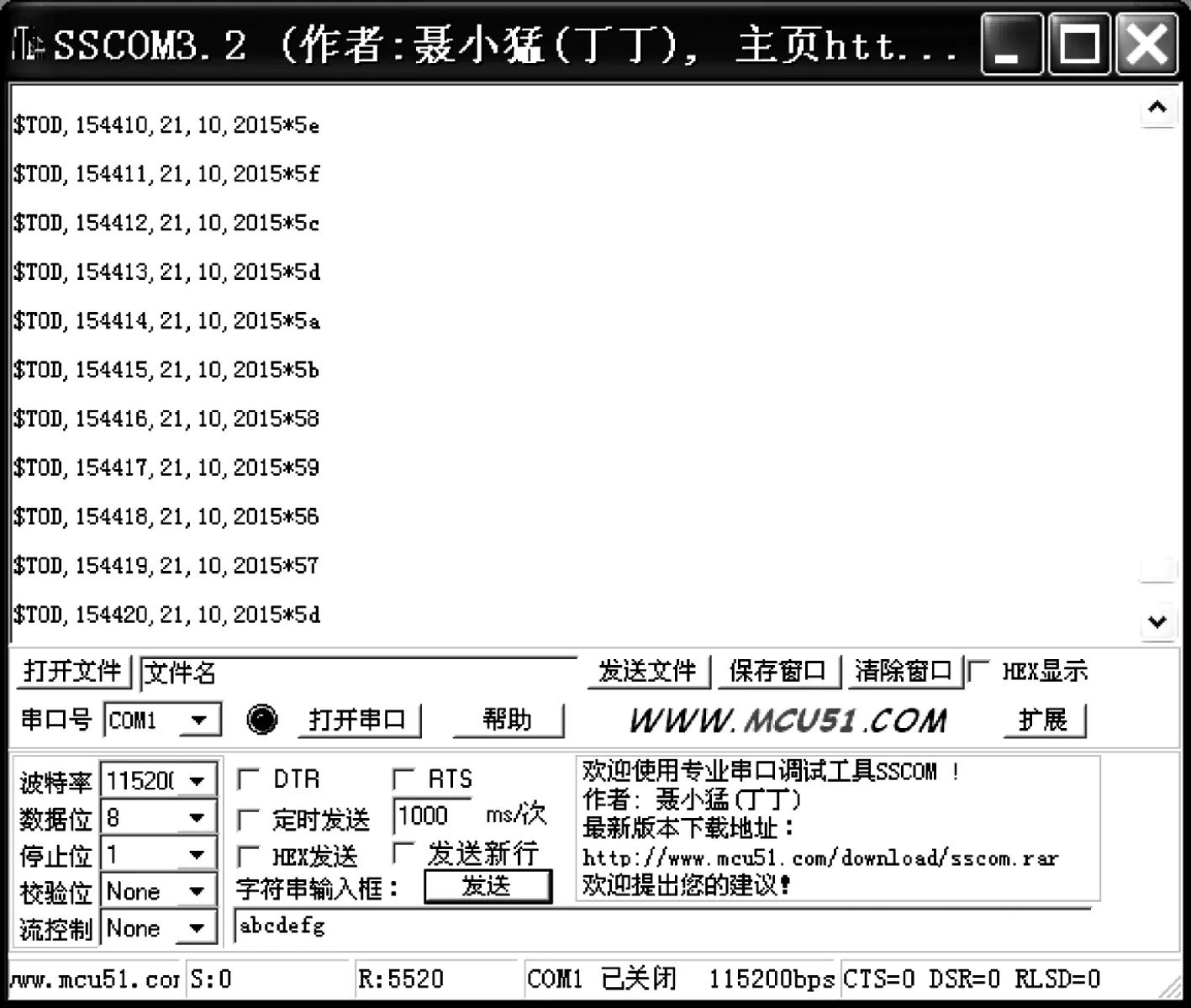

圖11 實驗測試結果

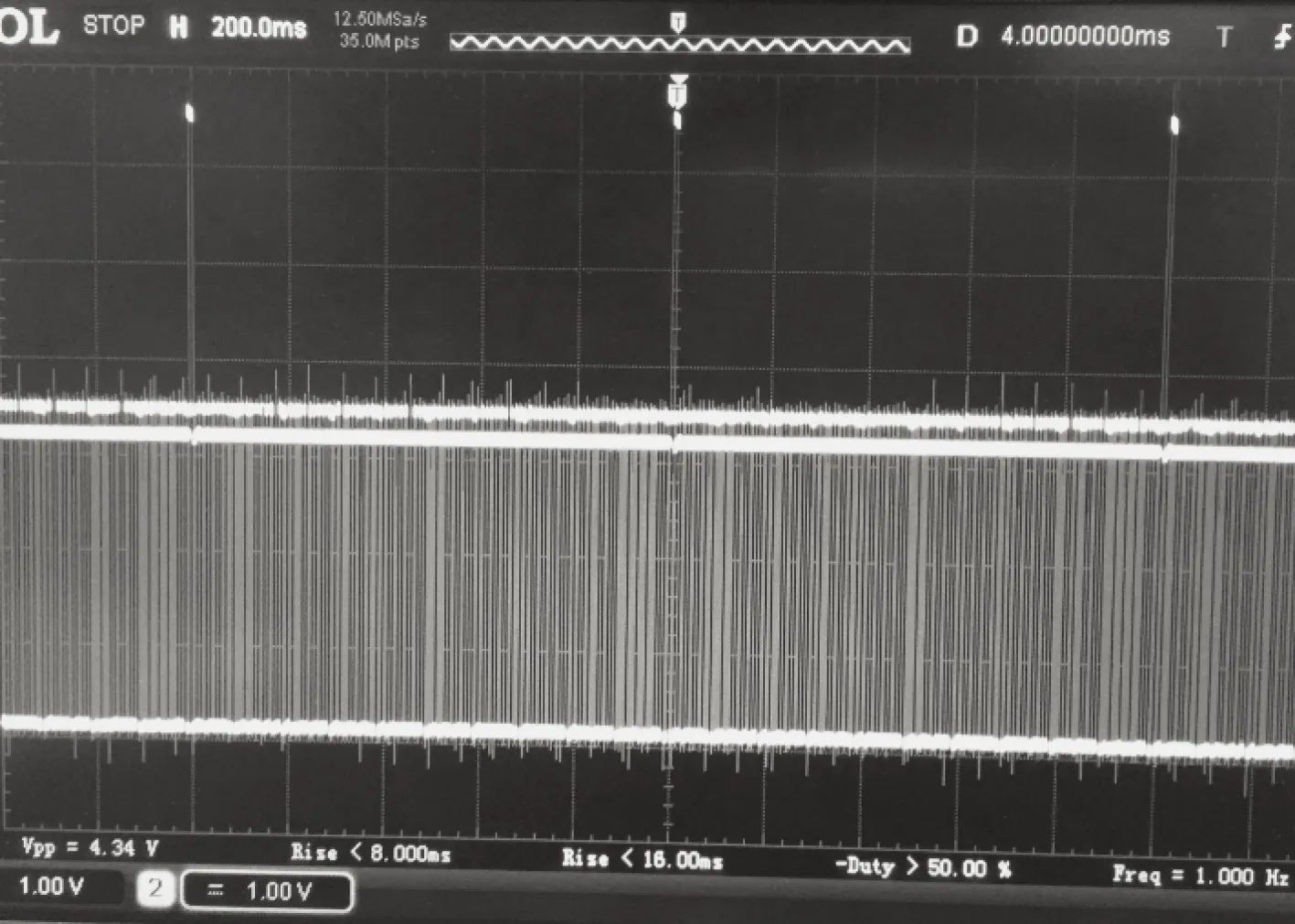

將串口輸出接入電腦串口調試助手中,從圖中可以看出,時間在1 s的跳變,時間跳變準確。用示波器監測秒脈沖輸出端和串口輸出端口,實驗測試結果見圖12。

圖12 實驗測試結果

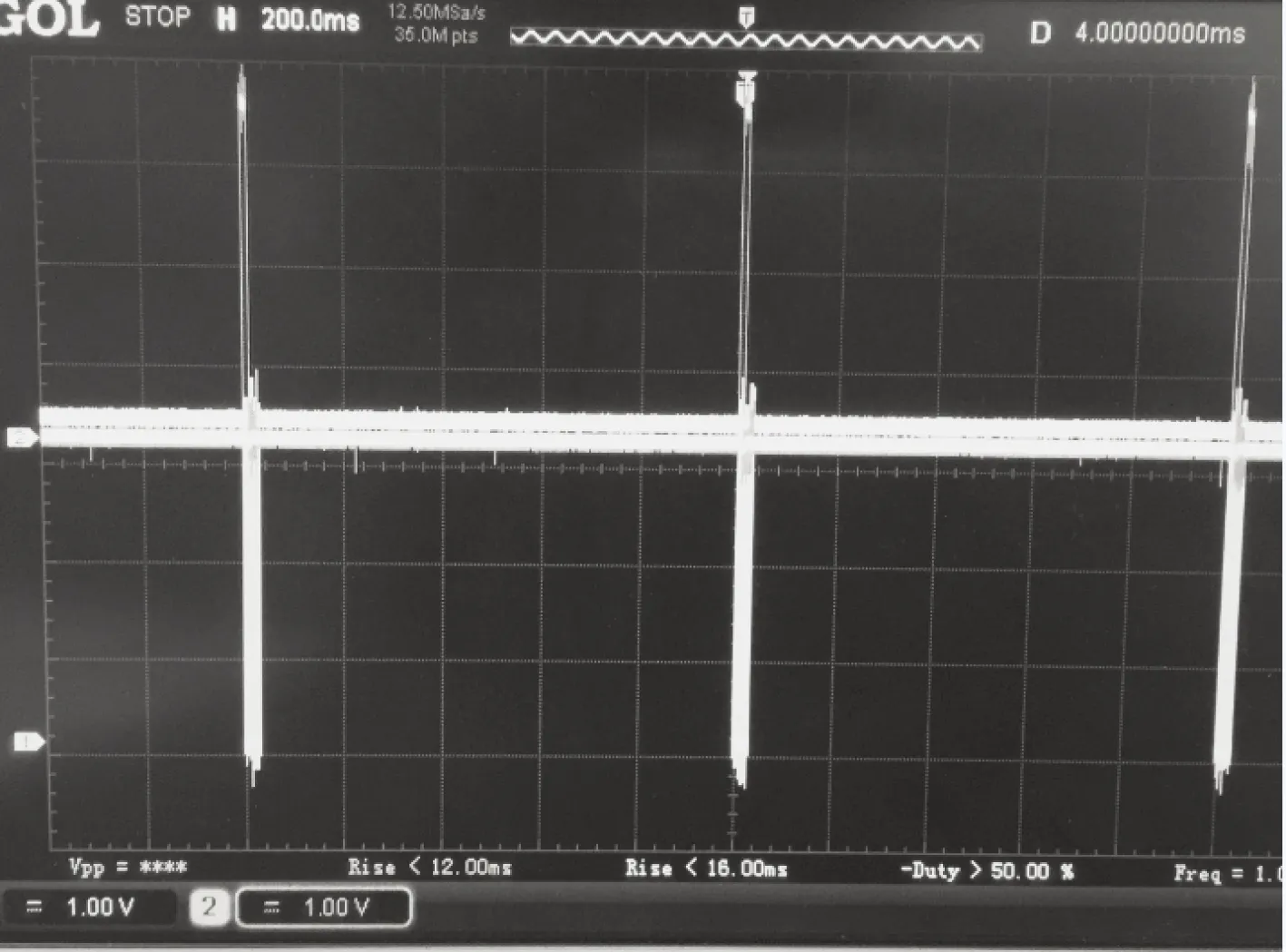

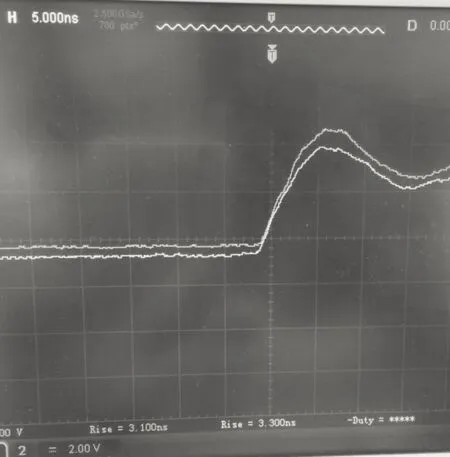

從圖中可以看出,解調1個PPS之后相鄰1幀解調的時間信息,解調的1個PPS和時間信息是IRIGB碼同幀數據。用示波器監測IRIG-B碼信號的輸入端口和解出的秒脈沖1個PPS輸出端口,測試結果見圖13。從圖中可以看出,每一解出的1個PPS對應1幀IRIG-B碼輸入信號。用示波器上升沿觸發方式捕捉1個PPS上升沿,可獲得如圖14所示的波形。

圖13 實驗測試結果

圖14 實驗測試結果

由圖14中可以看出,解出的1個PPS上升沿與IRIG-B碼輸入信號的準秒時刻對齊,且2者間的誤差優于5 ns,則本設計的解碼誤差優于5 ns;因此該IRIG-B碼信號解碼器的設計完全符合設計要求。

5 結束語

本文分析了目前IRIG-B碼解碼技術實現的現狀及存在的問題,介紹了IRIG-B碼解碼的基本原理,提出基于FPGA和Cortex-M3設計實現的IRIG-B碼解碼器,并結合某型時間同步裝置進行了監測。監測結果表明,該IRIG-B碼解碼器能夠滿足時統設備授時的需求,提高IRIG-B碼的授時精度、提升IRIG-B碼解碼效率、加強系統運行的可靠性。隨著IRIG-B碼在加速組網和授時系統中日益成熟,在今后工作中將進一步對IRIG-B碼解碼性能深入研究。

[1]The Timing Committee Telecommunications and Timing Group Range Commanders Council.IRIG standard 200-98 IRIG serial time code formats(Format B)[EB/OL].(2005-01-27)[2015-11-11].http://irigb.com/pdf/wp-irig-200-98.pdf.

[2]譚述森,李琳.北斗系統導航定位報告體制與工程技術[J].導航定位學報,2013,1(3):1-9.

[3]楊安洪,卜鮑強,姜忠武.雙模授時技術在航天測控設備中的應用[J].導航定位學報,2015,3(1):88-91.

[4]Microsemi Corportion.Smartfusion2 Microcontroller Subsystem UG0331 User Guide,m2s_ug0331_microcontroller_subsystem_v10.pdf[EB/OL].(2015-06-01)[2015-11-11].http://www.microsemi.com/index.php?option=com_docman&task=doc_download&gid=130918.

[5]Microsemi Corportion.Smartfusion2 SoC FPGA Evaluation Kit UG0541 User Guide,m2s_ug0541_evaluation_kit_ug_v4.pdf [EB/OL].(2015-06-01)[2015-11-11].http://www.microsemi.com/index.php?option=com_docman&task=doc_download&gid=133574.

[6]王茂凌.基于FPGA的IRIG-B(DC)碼解碼[J].現代有線傳輸,2005(4):86-88.

[7]賈磊,崔永俊,楊兵,等,基于FPGA的IRIG-B(DC)碼解碼卡的設計[J].計算機測量與控制,2015,23(6):2143-2145.

[8]吳衛,陳建軍,宋虎.基于FPGA的IRIG-B碼解碼器的實現[J].雷達與對抗,2009(3):37-40.

[9]顧陽陽,付道文.基于FPGA的IRIG-B碼解碼器設計[J].電子科技,2015,3(1):88-91.

[10]張建春,任記達.基于FPGA的IRIG-B碼調制解調實現[J].現代導航,2012,8(4):305-308.

Design and implementation of a IRIG-B signal decoder

CHEN Wei,WANG Yu,YU Feixia,FAN Xiaodong

(Anhui Suncreate Electronics Co.,Ltd.,Hefei,Anhui 230031,China)

Aiming at the problem that the existing IRIG-B signal decorder is liable to low decoding precision and lack of running stability,the paper proposed a IRIG-B signal decoding scheme by integrating MPU(Cortex-M3) and FPGA:the latest SOC was selected that configures microcontroller subsystem in Smartfusion2 and logical unit of FPGA;the IRIG-B signal code recognizing procedure was controlled by the hard logic of FPGA for ensuring the accuracy of the rising edge of the recognized PPS;the decoding procedure of the recognized time stream and the time output was designed in MSS in order to save FPGA resources and improve decode efficiency.Finally,by the field operation with instrument monitoring,result indicated that the IRIG-B decoder could offer better accuracy and stability than exiting decode technology,and the timing accuracy could satisfy the requirement of time synchronization.

Smartfusion2;FPGA;Cortex-M3;IRIG-B

2015-11-11

國家電子信息產業發展基金項目(工信部財[2013]472號)。

陳偉(1987—),女,安徽合肥人,碩士研究生,研究方向為通信與信息系統。

10.16547/j.cnki.10-1096.20160319.

P127

A

2095-4999(2016)03-0094-06

引文格式:陳偉,王宇,余飛俠,等.一種IRIG-B碼解碼器的設計與實現[J].導航定位學報,2016,4(3):94-99.(CHEN Wei,WANG Yu,YU Feixia,et al.Design and implementation of a IRIG-B signal decoder[J].Journal of Navigation and Positioning,2016,4(3):94-99.)