基于FPGA的模塊化聯網實驗箱系統的設計與實現*

許逸波++郝慧杰++周潤++肖建

文章編號:2095-6835(2016)13-0008-03

摘 要:由于傳統電工電子實驗箱平臺存在陳舊落后、結構固定的情況,已經脫離了物聯網革命的潮流,實驗教學信息化改革迫在眉睫。在分析物聯網原理的基礎上,使用模塊化設計,通過網口模塊進行網絡通信,采用單片機與FPGA協同處理控制,通過IIC總線驅動單元電路組合,完成了實驗箱硬件結構和基于ARM和FPGA的IIC驅動程序、網絡通信程序和系統控制程序,實現實驗箱系統與控制終端遠程互聯,完成了13個基本實驗,并可以通過更新實驗模塊拓展實驗箱功能。實踐證明,實驗箱系統系統性價比高,可以突破時間與空間的限制,提高學生的實驗效率,增強教學質量。

關鍵詞:物聯網;實驗箱;模塊化;單片機

中圖分類號:TP368.1 文獻標識碼:A DOI:10.15913/j.cnki.kjycx.2016.13.008

隨著各大高校對學生實踐能力的重視,實驗教學逐漸被提升到一個較高的地位。而目前,許多高校的實驗平臺都是從教儀企業采購的。該類平臺的結構往往固定,而且采用的導線連接直插式電子元器件方式,存在分立元件過多導致電路結構雜亂無章、錯誤頻現的弊端,造成實驗內容更新慢、實際利用率低,難以滿足學生日益增長的創新性實驗需求。這在很大程度上制約著學生專業能力的鞏固和提高。

此外,隨著近年來物聯網的興起,實驗室物聯信息化已成為實驗教學改革的必然趨勢。從提高實驗教學效率、實現信息化改革的角度出發,本文設計實現了一種具備物聯特性的基于FPGA的模塊化聯網實驗箱系統。它依托可編程器件和IIC總線通信技術,采用模塊化設計,兼容多種實驗電路單元,與互聯網結合形成一個巨大的網絡,提供功能可變、遠程可控、虛實結合的實驗平臺,提升設備的通用性和更新速度,提高學生的實驗效率,提高教學質量。

1 實驗箱系統的總體設計

在實驗教學物聯化改革的趨勢中,基于FPGA的模塊化聯網實驗箱系統首先要解決的問題是設備通信。對于實驗箱系統與測量儀器及客戶端之間的通信,采用網口通信的方式更加合適,以ARM單片機為通信核心,通過串口轉網口模塊,實現實驗箱系統的網絡接入,便于用戶對實驗箱的操作以及波形數據測量;對于實驗箱系統內部的通信,在眾多的通信方式中,IIC總線作為一種出色的通信方式,資源成本極低,而且信息傳輸速率相對較高,具備多從機掛載能力。因此,采用IIC總線進行系統內部通信,便于FPGA對于實驗電路模塊的管理和控制。

另外一個需要解決的問題是實驗內容的更新。基于FPGA的模塊化聯網實驗箱系統采用模塊化設計,依托IIC總線連接多個可插拔的電路模塊,在無需改動控制單元的情況下,靈活動態地搭建實驗電路。此外,可以根據學生在不同階段不同層次的學習需求,采用更換電路模塊的方式進行實驗內容的更新,充分滿足創新性實驗需要。

當然,實驗箱系統還需要包括處理模塊、電源模塊、編程下載口模塊和信號輸入/輸出模塊,加上之前的通信模塊、總線控制模塊和電路模塊三個模塊,共七個部分。系統采用星形拓撲結構,通過電源模塊提供功能保障,以單片機和FPGA協同的處理模塊為核心,向周邊輻射展開各功能模塊,實現實驗箱系統的物聯與重構功能。實驗箱系統結構如圖1所示。

2 單元模塊設計

根據系統總體設計,基于FPGA的模塊化聯網實驗箱系統集成多種功能,采用雙層結構,下層為實驗箱底板,上層為各功能模塊,包括處理模塊、電源模塊、通信模塊、總線控制模塊、編程下載口模塊、信號輸入/輸出模塊和電路模塊。圖2為實驗箱示意圖。

2.1 處理模塊設計

實驗箱系統借鑒片上系統(System on Chip,SOC)的思想,采用單片機與FPGA協同工作的方式,充分發揮FPGA的資源優勢以及ARM微處理器的低成本、低功耗和高性能,用 ARM單片機實現實驗箱系統與網絡的信息通信,用FPGA完整控制內部系統,兩者之間采用一組I/O口進行并行數據通信。其中,FPGA處理單元采用Xilinx的Spartan XC3S50,作為5萬門級

的可編程芯片,加上144個I/O口,其性價比高、處理速度快,完全可以滿足電工電子實驗教學的基本需求以及學生的創新性實驗需求;單片機處理單元采用的是STM32F103VE,其采用的ARM CORTEX-M3的內核和32位精簡指令集,成本低,性能優異,在72M的工作頻率下,具備較高的處理速度和較強的處理能力,可以進行較高速的數據通信和處理。

2.2 電源模塊設計

實驗箱系統主要用到的是+1.2 V、+3.3 V和±5 V,其中,+1.2 V和+3.3 V分別為FPGA芯片的內核與I/O口供電,使用±5 V給各模塊器件供電。1.2 V電源電路如圖3所示。

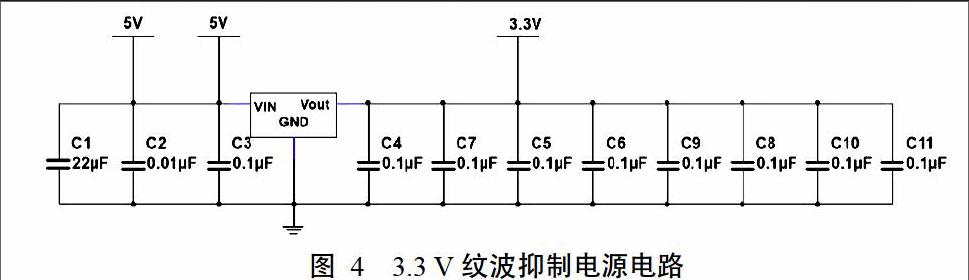

具體做法如下:①采用XL2576S降壓型開關穩壓器,將由外部輸入的12~40 V電壓信號進行降壓并穩定輸出5 V;②將5 V電壓作為輸入信號,通過AMS1117-3.3電源芯片降壓至所需的3.3 V;③以3.3 V電壓作為輸入信號,通過AMS1117-1.2電源芯片來獲取1.2 V的目標電壓。此外,考慮到電源正負極反接的可能,在信號輸入端采用最大反相電壓為45 V的1N5817二極管——超過了學生直流電源的最大輸出電壓,充分保護電源模塊及實驗箱系統。3.3 V紋波抑制電源電路如圖4所示。

由于系統中的各功能模塊對電壓值具有較高的要求,因此,如圖4所示,可以在輸出端外接成排接地電容,有效地濾除紋波,提高電源質量,給整個物聯化實驗箱系統提供紋波較小的工作電壓。

2.3 通信模塊設計

通信作為必不可少的一部分,其主要由兩部分組成,分別為RS232串口單元和網口轉串口單元。通信模塊與處理模塊連接,其中主要是采用ARM處理核心來進行數據的傳輸和處理的。RS232串口單元用于終端客戶機與實驗箱進行有線數據傳輸,在9 600波特率的速率下進行信息交互。網口單元主要由串口轉以太網模塊構成,模塊集成 10/100M 自適應以太網接口,最高波特率256 Kbps。將終端客戶配置為TCP Client工作模式,實驗箱配置為TCP Server,采用用戶/服務器的工作方式,實現實驗箱與客戶終端之間的數據傳輸,同時以串口數據的形式將數據發送至處理模塊。由于串口工作電平不同,在串口和控制電路之間還需要RS-232線路驅動器/接收器——ADM3202RN,通過升壓轉換器加上電壓電平轉化發射/接收器,實現通信單元與單片機的隔離,保護電路,防止發生高電壓損壞電路的情況。

2.4 總線控制模塊設計

基于FPGA的模塊化聯網實驗箱系統的核心內容是實驗電路的構成,總線控制模塊是建立在IIC總線和網絡通信技術基礎上的,由單片機通過網口來接收客戶端數據,同時把信息返回給通信模塊,實現信息的交互;然后單片機和FPGA協同處理控制命令,并主要通過FPGA來確定電路的重構方式,采用IIC總線主從應答的方式,選擇所需的電路模塊,通過控制命令,實現FPGA對單元電路的組合控制,確定各單元電路的動態組合,實現實驗電路重構。IIC結構如圖5所示。

該模塊是基于FPGA的模塊化聯網實驗箱系統的特點,由于賦予各電路模塊唯一的IP地址,使得這些模塊可以通過同一組IIC總線來實現數據通信,降低了產品的整體成本。此外,采用的環形布局和布設的多組接插口,不僅提高了系統的集成度,減少了導線長度,還可以降低信號衰減,提高系統的穩定性。

2.5 電路模塊設計

電路模塊是基于FPGA的模塊化聯網實驗箱系統的硬件實現部分,由模擬電路模塊和數字電路模塊組成,負責提供構成電路的多種元器件和小規模電路模塊。其中,數字電路相對簡單,可以由FPGA來直接控制和生成所需電路,當然也可以采用獨立的電路模塊來實現;而模擬電路要復雜得多,信號不再局限于“0”和“1”。因此,只能采用模塊來構成電路,通過FPGA進行模塊的組合拼接,搭建實驗電路。此外,實驗板上保留了多個用于激勵信號輸入、采集和控制的管腳,進一步增加了系統的靈活性。

2.6 信號輸入/輸出模塊

基于FPGA的模塊化聯網實驗箱系統采用的FPGA具有144個I/O口資源,在此預留了5個輸入信號端與5個信號輸出端,采用標準的4 mm香蕉插頭,降低信號衰減幅度,提高系統可靠性。

2.7 編程下載口模塊

基于FPGA的模塊化聯網實驗箱系統中采用的是可編程器件與單片機作為處理單元,因此需要分別設計下載模塊。

(a) (b)

圖 6 編程下載接口

對于單片機而言,從節約系統資源和提高下載效率的角度出發,采用SWD燒錄模式,僅需GND、VCC、SWDIO和SWDCLK 4個端口就可以實現仿真器與STM32的連接。在高速模式下,它比JTAG更加可靠,燒錄成功率更高,如圖6(a)所示;對于FPGA而言,采用JLINK仿真下載的方式,則至少需要VCC、GND、TDO、TMS、TCK和TDI6個接口,所有接口采用標準間距2.54 mm,如圖6(b)所示。

3 實驗箱應用

基于FPGA的模塊化聯網實驗箱系統的基本功能如表1所示。

與傳統的基于8051的電工電子實驗箱相比,該實驗箱的批量生產成本約700元。尤其在實驗箱網絡接入之后,用戶只需支付網絡平臺費用,成本極低,而且還能夠通過網絡進行真實的實驗學習。表1所列舉的實驗內容只是最基礎的一部分,可以根據學生實驗需求,通過更換電路模塊的方法來更新的實驗內容.因此,該實驗箱系統的功能更加全面,可滿足學生的創新性學習。

考慮到大學生創新訓練的需要,實驗箱上預留了編程下載口模塊和多個I/O口,提供實驗箱的二次開發空間,使得該實驗箱可以作為學生參加大學生電子設計競賽、挑戰杯競賽的賽前訓練之用,以學促賽,以賽促學。

4 結束語

基于FPGA的模塊化聯網實驗箱系統包括處理模塊、電源模塊、通信模塊、總線控制模塊、編程下載口模塊、信號輸入/輸出模塊和電路模塊,集成多種常用電子元器件,采用IIC總線控制的方式,根據任務要求進行單元模塊的動態組合,實現不同的電路功能。以網絡服務器為支撐的實驗箱系統,采用客戶終端控制的方式,進行網絡接入、數據交互、遠程控制和電路重構,擺脫了電工電子實驗中時間和空間上的限制,提高了學生實驗的效率,增強了實驗內容的豐富性和靈活性,為實驗教學提供了一個功能可變、遠程可控、虛實結合的硬件平臺。此外,作為教育改革中的一部分,本設備的成功研制,對實驗教學的信息化改革和建設具有一定參考意義。

參考文獻

[1]惠煌,賴曉晨,遲宗正,等.高校單片機教學實驗設備自制模式探索[J].實驗技術與管理,2012,29(5).

[2]周冠玲,馮占英,李戰.“單片機原理及應用”課程教學改革的探討[J].中國電化教育,2012,33(6).

[3]黃衛華,賈歷程.“基于FPGA的EDA實驗系統改革與實踐”[J].實驗室研究與探索,2012,31(4).

[4]部德才,張永平.基于LabVIEW的虛擬數字存儲示波器的設計[J].科技與創新,2014(20).

[5]于娟,唐瑞.基于89C52單片機的LED顯示器設計[J].科技與創新,2016(01).

[6]王漢森.一種智能功能集成的設計方法及實例[J].科技與創新,2016(01).

[7]賈萍,丁向榮,胡美蘭.“教、學、做”一體化單片機教學實驗平臺的設計與應用[J].實驗技術與管理,2012,29(6).

[8]胡文華,胡仁喜.Altium Designer 13電路設計[M].北京:化學工業出版社,2013.

〔編輯:胡雪飛〕