基于CPLD可編程邏輯控制器件FIFO的設計

周慶芳

【摘 要】隨著電子技術的不斷發展與進步,電子系統的設計方法發生了很大的變化,那些只提供特定的邏輯功能,不能夠由用戶根據具體設計的需要修改的成品邏輯器件已經慢慢被可編程邏輯控制器件所替代。本文介紹PLD可編程邏輯器件的設計開發及相關軟件的使用。并通過PLD的應用設計FIFO。在傳統設計的基礎上提出一種新穎的電路結構并對其進行綜合仿真和實現。首先介紹異步FIFO的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法;詳細介紹了每一個過程的設計思想和處理過程。使用Max+plusII和ALTERA公司的實驗箱對FIFO進行設計。

【關鍵詞】CPLD;Max+plusII;異步FIFO

一、引言

當前電子系統的設計正朝著速度快、容量大、體積小、質量輕、用電少的方向發展。推動該潮流迅猛發展的決定性的因素就是使用了現代化的EDA設計工具,使電子系統的電路設計變得更簡單,設計周期大大縮短。設計人員在不必更改硬件電路設計的前提下,只須要修改可編程邏輯電路的功能和用戶軟件,就可以完成面向不同應用需求的系統設計了。PLD(Programmable Logic Devices)是可以由用戶進行編程實現所需邏輯功能的數字集成電路。利用PLD內部的邏輯結構可以實現任何布爾表達式或寄存器函數。它能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用PLD來實現。FIFO (First In First Out)是一種在電子系統得到廣泛應用的器件,通常用于數據的緩存和用于容納異步信號的頻率或相位的差異。

二、PLD和Max+plusII簡介以及FIFO的設計原理

PLD是一種由用戶根據自己要求來構造邏輯功能的數字集成電路,一般可利用計算機輔助設計,即用原理圖\狀態機\布爾方程\硬件描述語言(HDL)等方法來表示設計思想,經一系列編譯或轉換程序,生成相應的目標文件,再由編程器或下載電纜將設計文件配置到目標文件中,這時可編程器件就可作為滿足用戶要求的專用集成電路使用了。Max+plusII是Altera公司推出的第三代PLD開發系統,主要用于設計新器件和大規模CPLD/FPGA。使用MAX+PLUSII的設計者不需精通器件內部的復雜結構,因而被公認為是最易使用,人機界面最友好的PLD開發軟件。

FIFO的基本單元是寄存器,作為存儲器件,FIFO的存儲能力是由其內部定義的存儲寄存器的數量決定。現在的FIFO存儲器采用SRAM單元來實現。它是基于帶兩個指針的環行FIFO結構的。要寫入的數據的存儲地址放在寫指針中,而FIFO結構中要讀出的第一個數據的地址放在讀指針中。從硬件上來實現循環存儲器,可以用雙端口的SRAM來存取數據。

三、異步FIFO的設計

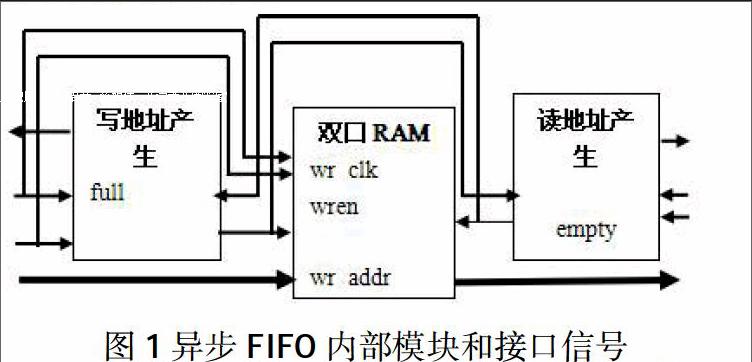

FIFO(先進先出隊列)是一種在電子系統得到廣泛應用的器件,通常用于數據的緩存和用于容納異步信號的頻率或相位的差異。FIFO的實現通常是利用雙口ram和讀寫地址產生模塊來實現的。FIFO的接口信號包括異步的寫時鐘(wr_clk)和讀時鐘(rd_clk)、與寫時鐘同步的寫有效(wren)和寫數據(wr_data)、與讀時鐘同步的讀有效(rden)和讀數據(rd_data)。為了實現正確的讀寫和避免FIFO的上溢或下溢,通常還應該給出與讀時鐘和寫時鐘同步的FIFO的空標志(empty)和滿標志(full)以禁止讀寫操作。寫地址產生模塊根據寫時鐘和寫有效信號產生遞增的寫地址,讀地址產生模塊根據讀時鐘和讀有效信號產生遞增的讀地址。FIFO的操作如下:在寫時鐘wr_clk的升沿,當wren有效時,將wr_data寫入雙口RAM中寫地址對應的位置中;始終將讀地址對應的雙口RAM中的數據輸出到讀數據總線上。圖1給出了FIFO的接口信號和內部模塊圖。

四、系統仿真與測試

本文中的設計方案經過仿真與測試,證明了系統實現了FIFO的基本要求。通過實踐,我們發現編譯的結果與仿真測試的結果一致,同時驗證了基于CPLD設計的FIFO系統具有非常高效率以及正確率,得到了比較滿意的結果。

五、總結與展望

通過軟件仿真,我們可以事先驗證設計的正確性。在PCB完成以后,還可以利用PLD的在線修改能力,隨時修改設計而不必改動硬件電路。使用PLD來開發數字電路,可以大大縮短設計時間,減少PCB面積,提高系統的可靠性。PLD的這些優點使得PLD技術在90年代以后得到飛速的發展,同時也大大推動了EDA軟件和硬件描述語言(HDL)的進步。

【參考文獻】

[1]王彩鳳,胡波,李衛兵,杜玉杰.EDA技術在數字電子技術實驗中的應用[J].實驗科學與技術,2011.01:4-6+110

[2]幸云輝,楊旭東.計算機組成原理實用教程.清華大學出版社,2004.1

[3]王金明.數字系統設計與Verilog HDL等編著.電子工業出版社出版,2004.3

[4]潘松等.現代DSP技術.西安電子科技大學出版社,2005.7