面向安全啟動的SPI Flash控制器

吳雪濤,戴紫彬,張立朝

(信息工程大學 密碼工程學院,河南 鄭州450001)

0 引 言

串行接口NOR Flash簡稱SPI Flash,它具有讀取速度快、穩定性高、易用性強等優點,已成為最常見的非易失性存儲介質之一[1]。

在以SPI Flash為主要存儲載體的SoC設備中需要加入專用的控制器來完成對SPI Flash的多種操作[2]。目前,常見的SPI Flash控制器主要有全硬件和軟硬件結合兩種實現方式[3,4],文獻 [3]采用軟硬件結合的實現方式,可操作性強、適用性廣泛但是無法支持系統啟動;文獻 [4]采用全硬件的實現方式,讀取速度快、能夠支持系統啟動,但是在讀取過程中無法進行數據加解密操作,因此其中重要數據尤其是啟動代碼的安全性無法保障。

針對上述情況,為提高系統啟動過程和片外存儲功能的安全性,本文基于AHB總線協議設計了一款ESSB (encryption storage and security boot)型SPI Flash控制器,在保證其使用效率的同時可支持系統安全啟動和加密存儲。本文設計的控制器采用緩存結構提高讀寫速度,提出了一種二次解析方法對SPI Flash的繁雜功能和操作進行優化,提高了可操作性。

1 SPI Flash差異性分析

不同廠商生產的SPI Flash芯片各有特點,為設計具有廣泛適用性的控制器,需要研究多種芯片的差異性,找到它們的共同點,并針對適用性較廣的結構進行設計,以提高兼容性。

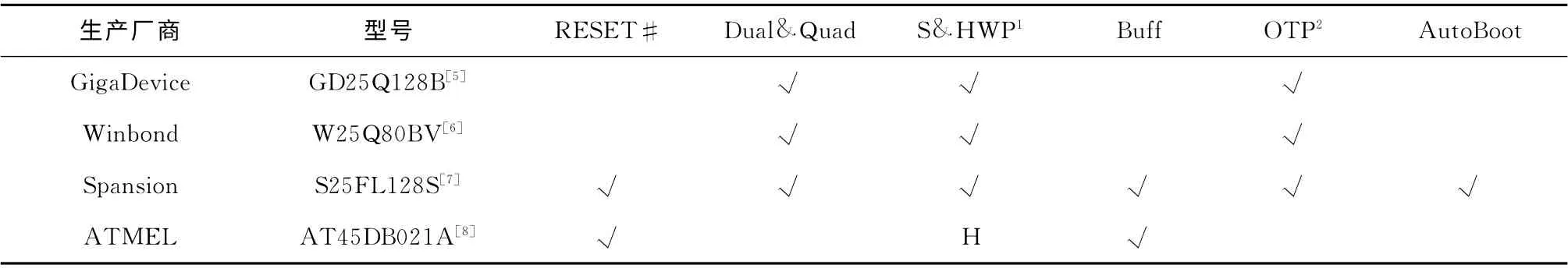

表1 通過對GigaDevice(兆易半導體)、Winbond (華邦電子)、Spansion (飛索半導體)、ATMEL (愛特梅爾半導體)等幾大主要SPI Flash廠商生產產品的對比發現了幾點不同:①管腳信號數目方面在是否支持Reset#上各有不同;②功能方面在是否支持雙端 (dual)和四端 (quad)模式、是否設置了緩存上略有差異,如ATMEL 的雙SRAM Buffer結構;③部分芯片還有其特殊功能,如飛索半導體的AutoBoot。但是在主要功能和結構上是具有很多相同點的:操作碼 (OP code)基本一致,操作時序基本一致,必要功能均得到很好支持等。除ATMEL 的AT45系列外其余幾個廠商所生產的芯片在主要操作上完全相同,如操作代碼和操作時序,且他們在功能上除一些附加功能外是通用的,因此就上述通用操作代碼集和基本功能設計的控制器是具有廣泛適用性的。

表1 主流SPI Flash廠商產品功能對比

據以上分析,本文設計的控制器能夠支持讀寫、快速讀寫、擦除、安全區域讀寫等主要功能,兼容兩種訪問接口,即能夠支持RESET#信號的硬件復位功能,其余信號為CS#、SO、WP#、SI、HOLD#、SCLK。對Flash芯片的控制都是通過SI、SO、WP、HOLD這4個控制信號來控制完成的。

2 SPI Flash控制器設計

SPI Flash在SoC設備中主要作為程序存儲器,用來存儲啟動程序、操作系統等代碼量不大的固件程序,也可用來存儲少量重要數據。針對許多應用場景對系統啟動過程的高效性和高安全性要求,本文所設計的SPI Flash控制器加入了Boot Supporter結構,實現了高效的系統啟動,同時集成了獨立的數據保護電路,保證了啟動代碼及重要數據的完整性和安全性。

2.1 控制器總體結構

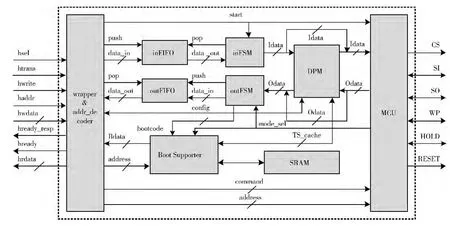

為保證各功能模塊的獨立性和靈活性,采用模塊化設計方法,該控制器整體結構如圖1所示。本文設計的ESSB型SPI Flash控制器由以下幾個模塊組成:接口和地址譯碼模塊 (wrapper &addr_decorder)、輸入控制模塊 (inFSM)、輸出控制模塊 (outFSM)、微控制器模塊 (MCU)、啟動支持模塊 (boot supporter)、SRAM、數據保護模塊(DPM)和輸入輸出FIFO 等。

控制器的信號傳遞過程為:接口和地址譯碼模塊接收AHB總線信號,直接向微控制模塊發出操作指令,由輸入(輸出)FIFO 和控制模塊完成數據的傳輸,傳輸完成后由控制模塊完成串并轉換,根據需要對數據進行加解密,生成指令序列,最后由微控制器匹配成SPI Flash芯片所能接受的時序完成相應操作。

圖1 SPI Flash控制器結構

2.2 接口和地址譯碼模塊

為了使控制器更好地與總線配合,設計了接口和地址譯碼模塊 (wrapper &addr_decorder)以解析總線時序并處理跨時鐘域問題。由于SPI Flash的功能較為繁雜可操作性差,在進行某些操作前還需要幾個先行配置操作,為用戶的使用帶來了極大不便。本文提出了一種二次解析的方法將其優化。wrapper &addr_decorder模塊對總線的請求進行先后兩次解析才轉換為Flash芯片可接受的命令,第一次解析是通過總線信號解析出用戶所執行的操作,并自動完成配置操作形成操作流;第二次解析是將此完整的操作流解析為相應指令序列傳輸給Flash芯片。采用這種方法,用戶既無需了解SPI Flash芯片各功能的OP Code也無需了解某項操作所需的配置操作而只需簡單地了解一套連續的數值各代表哪種操作即可,提高了使用性。

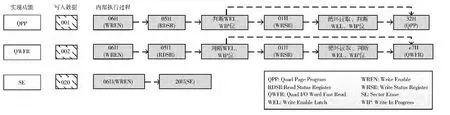

本文設計的控制器在wrapper &addr_decorder模塊中設置了一組可直接訪問的命令寄存器,總線對命令寄存器寫入不同數據將被解析出不同的操作,而后在內部填充好配置操作產生出完整的功能代碼傳送給Flash芯片,完成相應操作,例如:寫入0x001即實現QPP (四端頁寫)功能,內部將自動依次向SPI Flash芯片輸入06H (寫使能)、01H (寫狀態寄存器)指令代碼,然后由MCU 自動循環讀取狀態寄存器的數值直到寫入完成,最后輸入32H (四端頁寫)指令代碼。本文所使用的OP Code集為上一節分析得出的具有較強普遍性的代碼集,為防止出錯常用操作的寫入數據采用熱編碼機制。其中QPP、QWFR (四端快速讀)、SE (扇區擦除)的OP Code與命令寄存器中輸入數據的對應以及它們在Wrapper模塊內部的執行過程如圖2所示。

圖2 命令寄存器功能映射及執行過程

2.3 啟動支持模塊

由于SPI Flash的讀寫速度較SRAM 等易失性存儲介質慢得多,所以多用于程序的存儲而執行一般在SRAM 上完成。為支持系統啟動代碼的加載和執行過程,本文設計的控制器中加入了Boot Supporter模塊,包括Boot Supporter和SRAM。該模塊既能很好地支持啟動程序的執行過程又能提高啟動速度,在非啟動應用下作為DPM 模塊臨時數據的緩存,能夠減小硬件開銷,提高使用效率。

Boot Supporter與SRAM 共同實現系統的啟動功能。由于SPI Flash的一個扇區為4 K 字節,而且一般情況下SoC設備的啟動代碼不會超過4K 字節,所以將SRAM 的容量設置為4K 字節。Boot Supporter作為啟動過程的控制器,既能夠模擬SRAM 的時序,完成對SRAM 的讀寫操作,又能夠接受來自MCU 和DPM 的信號實現更復雜的功能。在其內部設置有狀態寄存器,為方便讀寫,設置為32 bit。在系統啟動階段MCU 通過mode_sel信號修改相應的標識位使Boot Supporter模塊進入啟動模式。在啟動模式下,為了完成啟動代碼的讀寫,Boot Supporter模塊支持AHB總線經wrapper模塊對SRAM 中的啟動代碼進行直接讀寫;啟動過程完成后,model_sel信號使其退出啟動模式,為保護SRAM 中緩存的數據不再支持直接讀寫。在非啟動模式下,DPM 模塊工作的過程中需要緩存大量的數據,為此特別擴展了其緩存功能,DPM 模塊可以直接將需緩存數據經Boot Supporter傳輸至SRAM 中,此時Boot Supporter的功能簡化為SRAM 控制器,在整個SPI Flash控制器內形成一個閉合的獨立存儲空間,保證了DPM 運行過程中數據的安全性。

2.4 數據保護模塊

在安全性需求較高的應用場景下,為保證系統的安全啟動,啟動代碼需要加密存儲,因此僅能夠完成代碼的加載和執行是不夠的,還需要通過加密來保證其安全性。

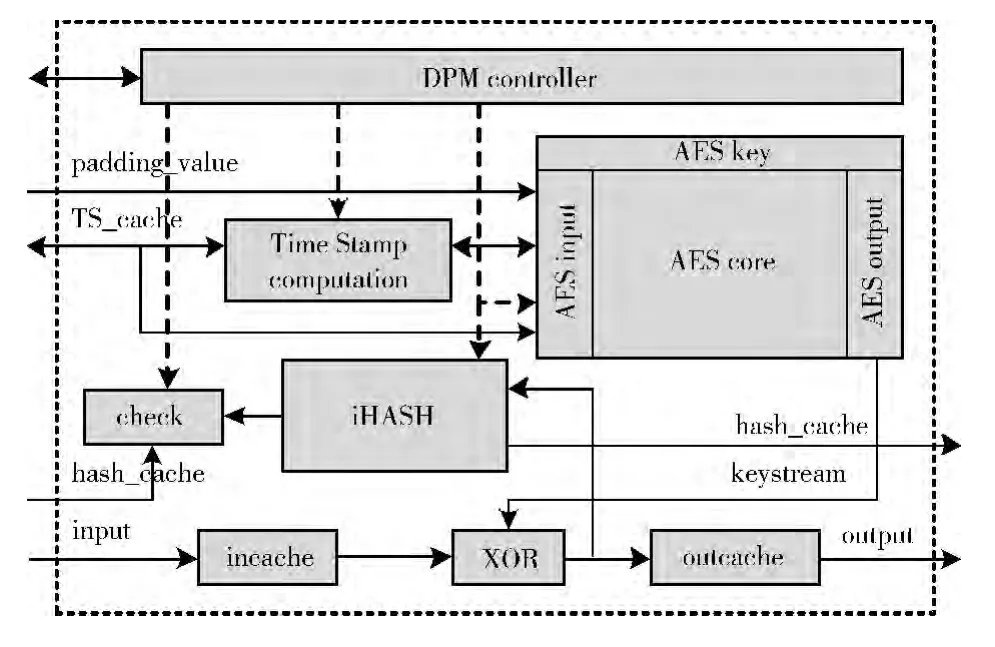

為了對Flash芯片中的數據進行加密存儲,本文采用了AES-TAC/iHASH 片外存儲安全防護技術[9]作為獨立的數據保護模塊DPM (data protection module),并針對本文特點加以改進。文獻 [9]的設計中為安全合理地保存iHASH 模塊產生的標簽以及AES-OTP模塊所產生的時間標簽TS (time stamp)在其結構中加入了標簽緩存,這樣一來硬件開銷會明顯增大,本文的設計中由于Boot Supporter模塊 (見2.3)的存在很好地解決了這個問題,減小了硬件開銷的同時也保證了標簽的安全性;在文獻 [9]的工作流程中,明文經過iHASH 模塊產生的標簽也被加密存儲在緩存中,在本文的應用中無需將其標簽再次加密存儲,提高了運行效率。圖3為DPM 模塊內部的結構。為抵抗竊聽攻擊且增強靈活性,AES core所需密鑰采用外部注入的方式,本文設計的數據保護模塊,可抵抗篡改攻擊、拷貝攻擊、竊取攻擊、監聽攻擊等攻擊模型有力地保證了數據的完整性和安全性。

圖3 DPM 模塊結構

在DPM 模塊中設置有配置寄存器和標識寄存器。配置寄存器用來指示當前輸入的數據是否需要加密存儲功能。配置寄存器的配置由wrapper模塊解析特定的命令完成,在數據進入前配置完成,當檢測到數據輸入完成信號后根據配置寄存器的值完成相應的操作。標志寄存器可被隨時讀取以了解當前運行狀態,設有工作狀態、工作模式、iHASH 值生成、完整性檢測、密鑰注入完成、keystream生成、數據加密、數據解密等標志位以表示響應工作狀態。

需要加以說明:在相當多的情況下我們存儲的數據并不需要進行加密或是添加雜湊值。為了增強電路的靈活性,使得控制器容易識別出此段代碼是否經過了加密處理。本文人為地將整個Flash芯片存儲區域劃分為兩部分,其中一部分用來存儲需加密存儲的數據,另一部分存儲未加密數據。寫入時,當寫入區域與加密設置不符合時提示錯誤,讀取時根據所讀取的區域進行是否進行解密運算。

3 控制器操作流程

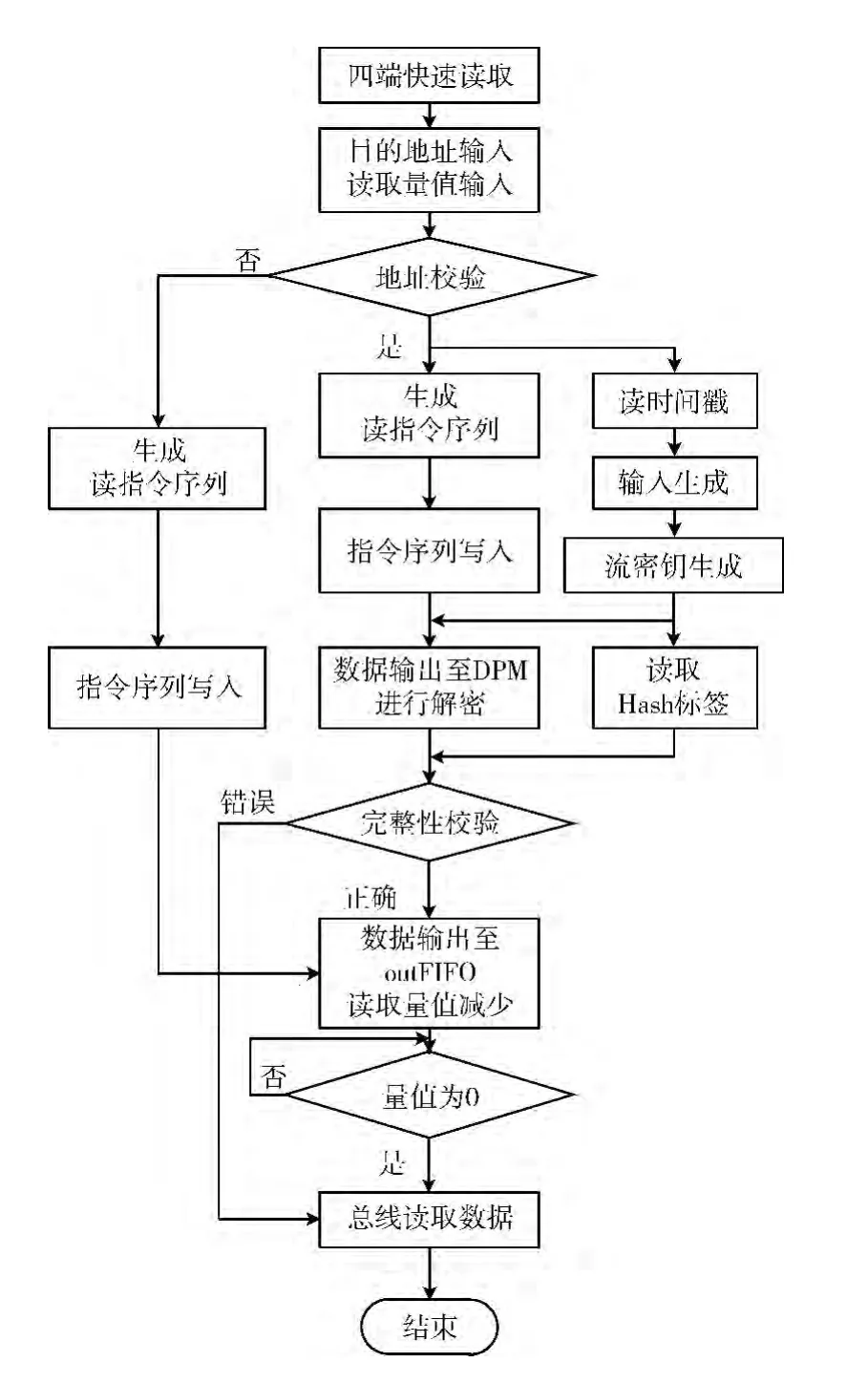

SPI Flash的操作時序較為復雜,本文設計的控制器通過優化使其復雜度大大降低,下面給出其操作流程。圖4以四端快速讀取操作為例給出了的一般的工作流程。

經優化后的操作流程有較高的一致性,依次可分為4個階段:輸入階段、校驗階段、序列階段、接收階段,不同的操作可能只有其中的幾個甚至只有一個階段。輸入階段需要使用者向命令寄存器輸入與操作對應的命令代碼、向地址寄存器輸入操作執行的地址、向數據端口輸入即將操作的數據,不同的操作需輸入的內容會有所不同。對于各不同寄存器的輸入沒有次序要求。校驗階段將對輸入的內容進行檢查,如果出現錯誤將向使用者報告并要求重新輸入,如果無誤將會繼續下一步操作。序列階段將生成能夠直接輸入至Flash芯片接口的指令序列,如果當前操作涉及數據寫入則直到數據準備好即發出start啟動信號時,才能生成由命令代碼、操作地址、操作數組成的指令序列,如果不涉及數據則可由指令代碼和操作地址甚至只有指令代碼組成指令序列。接收階段將由Flash芯片根據請求輸出相應的響應,例如讀狀態寄存器操作的寄存器數值,讀操作的讀出數據等。

圖4 控制器工作流程

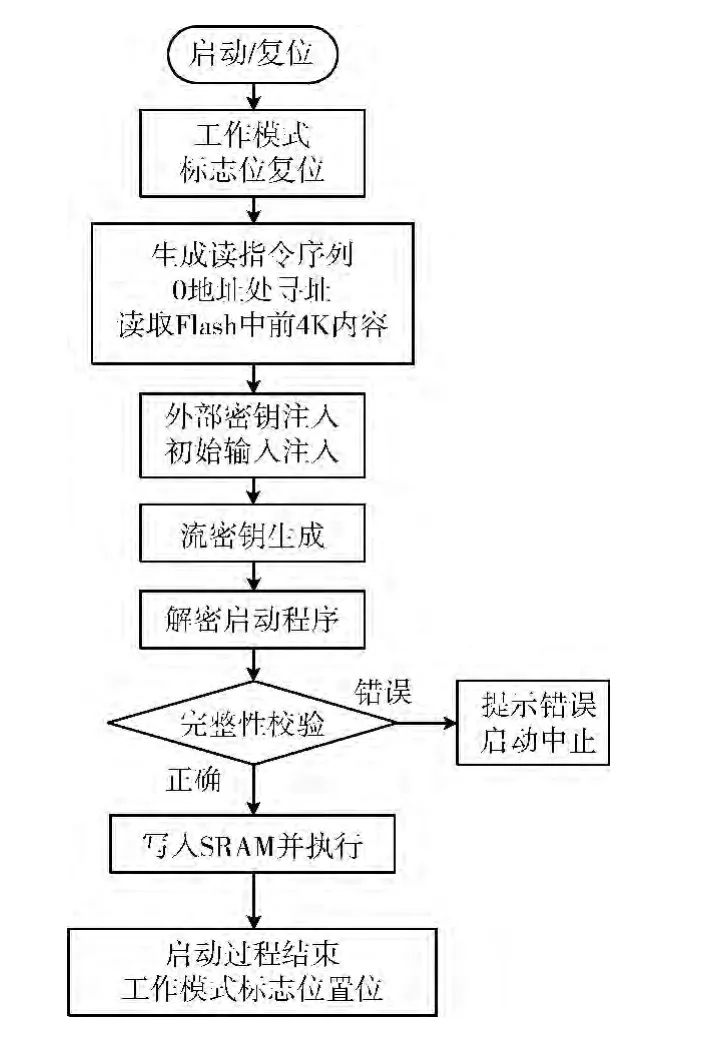

由于啟動階段的操作流程比較特殊,所以在圖5單獨給出,下面對啟動階段的工作流程做詳細介紹。系統上電啟動或復位后,MCU 檢測到復位信號,自動將操作地址設置為SPI Flash 中的起始地址,生成讀指令序列輸入至Flash芯片,讀出前4K 內容,讀取完成后等待外部密鑰注入,以此密鑰運行數據保護模塊進行解密,解密完成后運行完整性校驗,期間任何過程未通過則輸出提示信息后關閉系統,反之,則運行啟動代碼。

4 性能參數

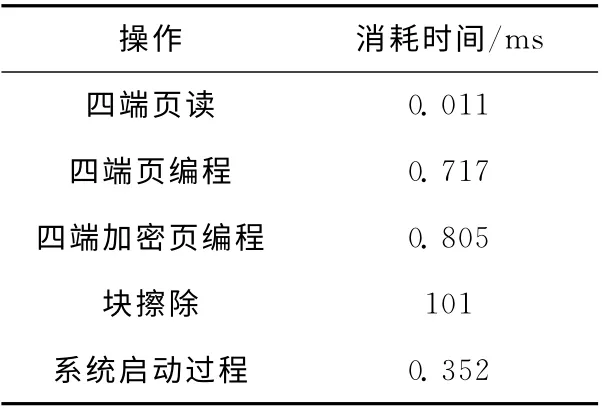

為驗證設計的正確性,采用Verilog HDL 語言對本文設計的SPI Flash 控制器編程實現,SPI Flash 芯片選用Giga Device的GD25Q128B,利用Synopsys公司的VCS軟件進行功能驗證,包括數據加解密和系統啟動在內的所有功能均正確無誤,在50 MHz時鐘下,各主要操作消耗時間情況見表2,與相關設計相比具有較高性能[10]。并利用Design Compiler軟件在SMIC 0.18μm 工藝庫下進行綜合,整個IP核的等效門數為9.78萬門。

圖5 系統啟動工作流程

表2 主要操作時間消耗

在功能驗證的基礎上搭建了硬件測試平臺,采用Altera公司的Stratix Ⅲ系列FPGA 芯片EP3SL150F1152C2N進行了硬件驗證,并利用Tektronix公司的TLA5202系列邏輯分析儀得到了Flash芯片接口處實際的信號波形圖,確認了其功能的正確性。實驗結果表明,本文所設計的結構可以實現安全高效存儲,可以較為容易地移植到其它系統中去,可以支持多種SPI Flash芯片,具有普遍適用性。

5 結束語

本文以SPI Flash控制器為研究對象,面向密碼SoC的應用場景,采用二次解析的方法對其操作方式進行優化,嵌入Boot Supporter結構和獨立的SHA-256和AES算法模塊同時保證了數據安全性和完整性,設計了一款可支持啟動加載和安全存儲的SPI Flash控制器,解決了其寫入速度慢、操作繁雜、安全性不足等問題。通過VCS功能仿真和FPGA 板級測試驗證了本文設計的可用性,在未增加資源消耗的情況下提高了安全性和高效性,實現了SPI Flash的啟動支持和安全存儲。本文所設計的控制器為數據的安全存儲提供了有力支持,其設計思想、整體結構和操作流程具有一定普遍適用性和參考價值。

[1]Chu CC,Lin YM,Yang CH,et al.A fully parallel BCH codec with double error correcting capability for NOR flash applications [C]//IEEE International Conference on Acoustics,Speech and Signal Processing,2012:1605-1608.

[2]Talole PT,Sawale ST.Performance enhancement by the design of flash controller for x8NAND flash memory devices[J].International Journal of Computer Applications,2010,1 (9):24-29.

[3]CHEN Chaowen,PENG Guojie,WANG Yiwen,et al.Design of NOR flash controller based on PLB general bus [J].Microelectronics &Computer,2014,31 (5):83-86 (in Chinese). [陳超文,彭國杰,王憶文,等.基于PLB 總線的NOR FLASH 控制器設計 [J].微電子學與計算機,2014,31(5):83-86.]

[4]LUO Li,XIA Jun,DENG Yu.Design and verification of general SPI flash controller [J].Computer Engineering,2011,37 (8):22-24 (in Chinese). [羅莉,夏軍,鄧宇.通用SPI Flash控制器的設計與驗證 [J].計算機工程,2011,37 (8):22-24.]

[5]Technical Datasheet.GD25Q128B [S].

[6]Technical Datasheet.W25Q80BV [S].

[7]Technical Datasheet.S25FL128S [S].

[8]Technical Datasheet.AT45DB021A [S].

[9]CAI Luting,XU Jinfu,ZHANG Lichao.Security management of off-chip memory based on AES-TAC/iHASH [J].Computer Engineering and Design,2014,35 (3):841-845(in Chinese). [蔡路亭,徐金甫,張立朝.基于AES-TAC/iHASH 的片外存儲器安全防護 [J].計算機工程與設計,2014,35 (3):841-845.]

[10]TIAN Peng,NIE Zedong,ZHANG Zhengping,et al.Design of a nor flash controller IP compatible AHB bus[J].Microelectronics & Computer,2013,30 (6):88-91 (in Chinese).[田鵬,聶澤東,張正平,等.一種兼容AHB總線的Nor Flash控制器IP 設計 [J].微電子學與計算機,2013,30 (6):88-91.]