基于6Gbps速率光纖傳輸系統設計

唐 寬 王皓奎

(廣西瀚特信息產業股份有限公司,廣西 桂林 541004)

基于6Gbps速率光纖傳輸系統設計

唐 寬 王皓奎

(廣西瀚特信息產業股份有限公司,廣西 桂林 541004)

隨著 3G技術的發展以及多模系統的應用,傳輸帶寬要求越來越寬,載波數要求越來越多,這就要求在傳輸鏈路上有更高的速率,因此6Gbps速率光纖傳輸技術要求越來越緊迫,為了實現6G光纖傳輸技術應用于產品,對6Gbps速率光纖傳輸技術涉及的并行數據到串行數據轉換,數據同步,串行數據收發,時鐘恢復等做了測試,設計了FPGA程序并下載到FPGA芯片中進行了驗證。實現了高數據速率下光纖的數據互聯。

FPGA;串行收發器;光纖傳輸;誤碼率

隨著3G技術的發展以及多模系統的應用,傳輸帶寬要求越來越寬,載波數要求越來越多,這就要求在傳輸鏈路上有更高的速率,因此6Gbps光纖傳輸技術要求越來越緊迫,為了降低6Gbps光纖傳輸技術直接在產品中應用所帶來的研發風險,迫切需要提前對6Gbps光纖傳輸技術進行技術研究。據此,本文設計6Gbps光纖傳輸系統,滿足了市面上射頻拉遠單元在多模系統中的應用,并且可配置性強,便于靈活組網使用。

1 系統總體設計框圖

該系統設計了TD-SCDMA多模系統中的GSM近端數字模塊和GSM+TD-SCDMA的遠端數字模塊。近端和遠端的FPGA芯片采用支持6Gbps數據傳輸的單FPGA芯片,這樣硬件相對簡單,同時也滿足了系統要求。

系統總體設計框圖如下圖1所示:

圖1 系統總體設計框圖

預計設計系統的工作方式如圖 1所示,近端為GSM_ADD,其中,D、E、F為業務光口,功能對等。Y用于近端機之間內部交互光口,用于傳遞TD、 GSM及WLAN數據。Z為WLAN端口,用于與WLAN專用模塊相連。遠端機C為WLAN端口。測試只用上圖1-1中GSM通道,從近端機輸入GSM信號,在遠端機射頻口輸出GSM信號到頻譜儀,來驗證整個6G光纖傳輸的可用性。

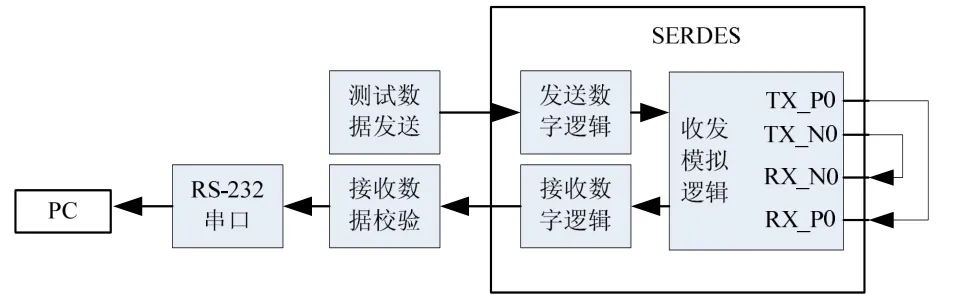

2 系統回環測試程序設計

系統回環測試是驗證測試程序和硬件設備正常的常用方法之一。根據圖1所示,可分別在GSM ADD和RDD1設備進行多種系統回環測試,比如GSM ADD自己的光纖發送口直接回環到光纖接收口,也可以使用GSM ADD自己的光纖發送口發送到RDD1的接收口,然后在RDD1中進行數據回環,再通過A口送回到F口的接收端。回環測試框圖如圖2所示:

圖2 回環測試框圖

如上圖4所示,首先在FPGA內部編寫測試數據發送代碼,發送固定格式的測試數據,如K28.5,幀號,1,2,…,255,K28.5,幀號+1,1,2…數據序列,這種數據序列可以防止整幀丟失的情況。通過SERDES的發送邏輯發送到TX差分端,外部采用兩根50Ω阻抗線回環到RX差分端,再經過SERDES的接收邏輯解碼輸出到接收數據校驗模塊,該檢驗模塊按照發送模塊的固定數據序列進行檢驗,同時把檢驗結果通過RS-232端口發送到PC機串口上進行打印。

3 光纖傳輸的實現

該節闡述了6Gbps速率下光纖傳輸的具體實現過程。

3.1 SERDES接口實現

去自SERDES接口包括153.6M的發送時鐘,32位寬的數據,4位寬的控制字選擇是發送控制字還是數據,同時注意SERDES發送數據是從最低位開始發送的。SERDES接口時序如圖3所示。

圖3 SERDES接口時序

153.6M的發送時鐘由SERDES給出,發送數據與該時鐘要對齊。8B/10B編碼規則為一個字節的最高3bit為一組,值范圍為0~7;其它5bit為一組,值范圍為0~31;當對應字節的控制位為低時發送正常數據為DX.Y,當對應字節的控制位為高時發送K碼為KX.Y。

3.2 SERDES硬核對外接口

用altera的MegaWizard產生的6G SERDES硬核如圖4所示,由于Arria II GX這一類器件目前還不支持6G速率,所以在這選用了Stratix II GX這一類器件才能在deserializer寬度上選擇32位。

圖4 SERDES硬核對外接口

SERDES 硬核對外接口詳細端口定義如表1 所示。

表1 SERDES硬核詳細端口定義

3.3 6Gbps傳輸測試框圖仿真

用對于圖2所示框圖搭建modelsim仿真平臺,對FPGA代碼和6G serdes進行仿真,仿真結果如圖5所示。

圖5 SERDES硬核對外接口

在圖5中,FPGA收發時鐘為307.2MHz,給到SERDES的參考時鐘也是為307.2MHz,其中i_from_bricx_data為收到來自 SERDES的 16bit數據,i_from_bricx_ctrl為收到來自SERDES的 2bit控制信號指示,o_to_bricx_data為發送到SERDES的16bit數據,o_to_bricx_ctrl為發送到SERDES的2bit控制信號指示。o_err_cnt為校驗結果錯誤計數器。由上圖可知,代碼按照預定的發送數據格式進行發送數據,同時SERDES接收到的數據也是與發送數據相同,仿真正確。

3.4 6Gbps傳輸數據發送

如圖6所示,圖6中的o_to_bricx_data為16位發送數據到SERDES,o_to_bricx_ctrl為2位發送控制到SERDES,從圖 6中發送的數據可以看出,發送數據滿足方案中測試數據格式。

圖6 測試數據發送

3.5 6Gbps傳輸數據接收

如下圖7所示,圖7中的i_from_bricx_data為16位接收數據來自 SERDES,i_from_bricx_ctrl為 2位接收控制來自SERDES,通過與發送數據對應的接收數據進行比較,可以看出接收數據正確。 而K碼出現的在高字節,發送K碼是固定出現在低字節的,所以,程序里面需要做K碼自動調整。

圖7 SERDES硬核對外接口

3.6 6Gbps傳輸數據誤碼測試

在對接收數據進行位置調整后,與發送數據進行比較,如出現不匹配,則誤碼計數器o_err_cnt會加1,從圖6中和圖7中可以看出誤碼計數器一直保持了0,即沒有誤碼。同時,對誤碼計數器o_err_cnt作為觸發條件,對主近端接收的數據進行校驗,對系統進行了 145分鐘測試,沒有校驗到一個誤碼。

根據誤碼計算公式,1RT=1(6X109*145*60)=1.9e-14,即誤碼率小于e-14量級。

4 結束語

本文闡述了一種新型的6Gbps速率光纖傳輸系統設計方法。該系統已經應用到TD-SCDMA和GSM多模RRU系統中。系統在應用了6Gbps速率光纖傳輸系統,射頻拉遠數在原來基礎上提高 1倍。設計好的代碼作為程序模塊可以方便的移植到多種應用平臺上,一定程度上降低了開發的難度,為大系統程序提供了更為方便的接口,也在很大程度上提高了光纖傳輸的效率。

[1] 蘇翼凱.高速光纖傳輸系統[M].上海:上海交通大學出版社,2009.

[2] 毛幼菊,朱繼光.光纖通信新技術[M].重慶:光通信研究所,2004.

[3] 徐曉庚.高速光纖通信系統傳輸特征的研究[D].武漢:華中科技大學,2006.

[4] 夏宇文.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2005.

[5] 陳瑋瑋.高速光纖通信系統中碼型技術的研究[D].南京:南京郵電大學,2005.

Design of 6Gbps data rate fiber transmission system

With the development of 3GPP technology research and development, the 2G technology GSM and the TD-SCDMA combine system are research and development. the transmission baud rate want more and more, the carrier numbers want more and more. So in transmit link should have high data rate, use fiber as transmission media, the limitations is the parallel data translate to serial data, data synchronization, serial data receive and transmit, clock recover, in this paper write the FPGA code and download to the FPGA chip ,research the upwards technology, and test all the parameter. Get the highest data rate in fiber interconnecting result.

FPGA; SERDES; fiber transmit; bit error rate

TP393

A

1008-1151(2015)02-0010-03

2015-01-13

唐寬(1983-),男,廣西全州人,供職于廣西瀚特信息產業股份有限公司;王皓奎(1974-),男,廣西桂林人,供職于廣西瀚特信息產業股份有限公司。