一種兼顧效率和電磁兼容的反激變壓器設計

曾智強 鄭心城 陳 為

(福州大學電氣工程與自動化學院,福州 350116)

近年來,便攜式、可移動式電子產品的使用越來越廣泛。而這些設備大部分都需要通過外部電源適配器來供電。這些電源適配器一般采用反激電源電路。因為其電路簡單、工作穩定可靠、易于控制、體積較小且成本也相對較低。而反激電源效率及EMI的特性優化設計一直是電源工作者的研究熱點之一。

效率是衡量電源性能的一個重要參數。隨著人們對節能和環保的日益重視,全球各國對于產品能源利用效率的要求也日益提高。文獻[1-5]利用軟開關技術和同步整流技術來減小變換器的開關損耗,從而提高整機效率。而反激變壓器作為反激電路不可或缺的關鍵器件之一,其體積、重量約占整個電路的20%~30%,損耗約占總損耗的30%[6]。因此,為了使電源設計符合電力電子技術沿著高頻、高效率、高功率密度方向發展的要求,變壓器成為其優化的首選對象。文獻[7]通過繞組交叉換位技術及改變磁心氣隙與繞組的相對位置對高頻磁性元件進行優化,從而提高整機效率。另一方面,為了減小體積和重量,從而提高變換器的功率密度,最常用的方法是提高頻率[8]。但不管是通過改變繞組的繞制方法來提高變換器的效率,還是通過增大頻率來提高變換器的功率密度,往往會帶來另一個問題電磁干擾。因為功率開關器件和磁性器件本身具有的非線性特性,在高頻工作頻率下,電壓、電流的變化率很大,會產生很強的電磁干擾。文獻[9]從共模噪聲的耦合途徑的角度考慮,基于噪聲平衡的原理,提出了增加一個額外的電容和優化變壓器繞組間的屏蔽這兩個新的方法來減少共模噪聲。文獻[10]通過增加一個補償變壓器繞組和一個電容器,實現了Buck、Boost、Fly-back、Forward、Buck-Boost等基本變流器中共模干擾的部分抵消。但通過外加補償電容和補償繞組來抑制電磁干擾的同時,會帶來額外的損耗,使得變換器的效率降低。因此對提高電源的效率的同時減小傳導共模EMI的噪聲的研究不僅具有重要的理論意義也具有很好的工程實用價值。本文以反激電源為研究對象,基于次級繞組凈感應電荷的理論模型,通過理論計算分析不同的屏蔽體接地點位置及不同的屏蔽高度對變壓器共模傳導EMI的影響。從而提出一種改進型的三明治繞法來兼顧反激變換器的效率和電磁兼容問題。

1 原理與設計

反激電源的電磁干擾源主要有兩個:一個是原邊的功率開關管,另一個是副邊的整流二極管。它們在開通和關斷過程中會產生較大 di/dt和 du/dt,這是產生電磁干擾的主要原因。從這兩個干擾源出發到接收干擾的 LISN總共有三條耦合路徑。圖 1所示為變壓器繞組加屏蔽銅箔且散熱器接整流負端的共模噪聲耦合路徑圖。圖中的耦合電容定義如下:變壓器原邊功率管漏極與散熱器間的耦合電容用電容Cp0表示;原邊電位熱點對副邊電位靜點的耦合電容用Cps表示;副邊電位熱點對原邊電位靜點的耦合電容用Csp表示。由于散熱器接整流負端的地,所以路徑③被屏蔽,電磁干擾無法到達LISN。根據圖1對反激式共模噪聲傳輸通道的分析,可建立如圖2所示的共模傳導噪聲的等效電路模型[11]。

從圖2可以看出,原、副邊的兩個共模傳導干擾源的作用極性是相反的,流過 LISN阻抗的共模傳導噪聲總電流為兩條路徑上的電流之差。因此合理控制Cps和Csp的值可以有效地減小共模噪聲。那么,如果將兩條路徑上的電容等效成一個有效電容CQ[12],只要控制有效電容CQ的大小便可以控制共模傳導噪聲總電流的大小。若已知電位分布,只要計算出電荷Q就可以得到C。所以本文抑制共模噪聲的基本思想就是使得歸算到次級繞組上的感應總電荷∑Q等于0。

圖1 繞組加屏蔽的共模噪聲耦合路徑

圖2 反激電源共模傳導噪聲的等效電路模型

1.1 屏蔽體高度對變壓器共模傳導EMI的影響

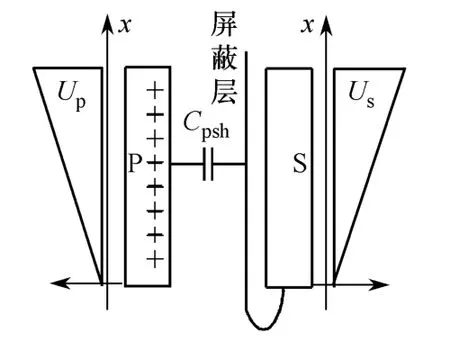

圖3表示PS繞法加部分屏蔽接原邊電位靜點的次級繞組感應電荷示意圖。假設b為屏蔽層的高度。其中,w為全屏蔽的高度,Cps為原邊繞組和副邊繞組之間的結構電容,Cssh為副邊繞組和屏蔽層之間的結構電容。

圖3 PS繞法加部分屏蔽接原邊電位靜點

根據次級繞組凈感應電荷的理論,可以得到原邊繞組、副邊繞組以及屏蔽銅箔沿高度方向的電位分布:

當繞組的高度為x的時候,原邊繞組和副邊繞組之間的電位差:

當繞組的高度為x的時候,副邊繞組和屏蔽層之間的電位差為

那么,變壓器初級繞組在次級繞組所感應出的電荷量以及屏蔽銅箔在副邊繞組所感應出的電荷量分別為Q1和Q2。副邊繞組所感應出的總電荷量為∑Q。

當b=0時,可以得到無屏蔽銅箔時,變壓器副邊繞組所感應出的總電荷量為

在如圖3所示的變壓器為PS繞法加部分屏蔽接原邊繞組電位靜點的情況下,已知參數:單位高度的Cps=0.56nF,單位高度的Cssh=0.66nF,w=9.2mm,可以畫出如圖4有效電容大小隨屏蔽層高度b變化趨勢圖。發現當b=8.84mm時候,CQ大小為 0,而不是全屏蔽的高度w=9.2mm。因此屏蔽高度有一個最優值。

圖4 有效電容大小隨屏蔽層高度變化趨勢圖

1.2 屏蔽體接地位置對變壓器共模傳導EMI的影響

圖5表示PS繞法加全屏蔽銅箔接變壓器次級繞組電位靜點感應電荷示意圖。沿初級繞組各匝線圈和屏蔽層的電位分布的表達式分別為

當繞組的高度為x的時候,原邊和屏蔽層的之間的電位差為

則變壓器初級繞組所感應出的電荷量為

圖5 PS繞法加全屏蔽接副邊繞組地

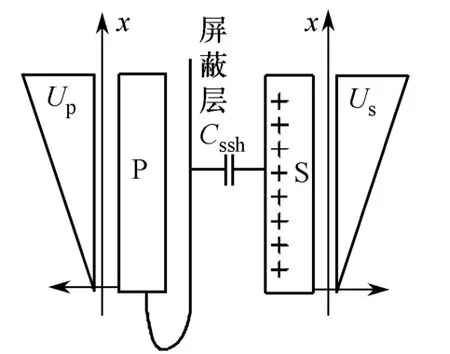

圖6表示PS繞法加全屏蔽接初級繞組地感應電荷示意圖。沿副邊各匝線圈和屏蔽層的電位分布的表達式分別為

當繞組的高度為x的時候,初級繞組和屏蔽層的層間的電位差為

則變壓器副邊繞組所感應出的電荷量為

圖6 PS繞法加全屏蔽接初級繞組地

由式(11)和式(15)可以看出,全屏蔽的∑Q比不屏蔽的還要大。所以屏蔽體接地位置會對變壓器共模傳導EMI產生影響,若屏蔽銅箔接變壓器副邊的電位靜點,全屏蔽反而比不屏蔽的效果更差。

1.3 改進型三明治繞法

圖7為改進型的三明治繞法,其中Up∶Us=15∶1,原邊繞組分成4層繞制,先原邊繞組繞兩層接著繞一層副邊繞組,然后繞剩余的兩層原邊繞組,最外一層為輔助繞組。

圖7 改進型三明治繞法

那么,沿初級繞組各匝線圈和屏蔽層的電位分布的表達式分別為

沿副邊各匝線圈和屏蔽層的電位分布的表達式分別為

當繞組的高度為x的時候,次級繞組和初級繞組間的電位差為

則變壓器初級繞組在副邊繞組所感應出的電荷量為

當繞組的高度為x的時候,次級繞組和屏蔽層的層間的電位差為

則變壓器屏蔽層在副邊繞組所感應出的電荷量為

則變壓器次級繞組所感應出的總電荷量為

由式(26)可以看出影響次級繞組所感應出的總電荷量的因素有兩個:一個是繞組的電位分布,另一個是結構電容的大小。欲改變繞組的電位分布可以通過改變繞組的層數、接地引腳的位置等。而改變結構電容則相對容易一些,本文通過調節原邊繞組與副邊繞組之間的間距d1和屏蔽層與次級繞組之間間距d2,使其滿足式(27),從而使得Cssh和Cps滿足式(27)的關系式,從而來抑制傳導共模EMI的影響。

2 實驗驗證

利用一臺反激電源iPad充電器作為測試實驗對象。輸入電壓Uac為:220V/50Hz,輸出電壓Uo為:5V/2A。樣機的主電路拓撲、控制回路和反饋回路如圖8所示。原樣機的變壓器采用PS繞法,磁心為EE19,初級繞組電感1.15mH,120匝;次級繞組電感:5.48μH,8匝。

圖8 反激電源

2.1 變壓器繞法對效率的影響

為了分析變壓器繞法對效率的影響,制作了三種不同繞法的變壓器。分別為 PS繞法,普通 PSP繞法和改進型 PSP繞法并于同一個樣機上進行實驗。

利用阻抗分析儀測量這三種變壓器的激磁電感和漏感,并在同一樣機上測試了其滿載 2A時的整機效率。表1為三種變壓器繞法對各參數影響情況。其中初級繞組電感在 1.15±10%左右。從表 1可以看出改進的PSP繞法比原樣機的PS繞法滿載效率提高了2.31%。因為PSP繞法增加了初、次級繞組之間的耦合面積,減小了變壓器的漏感,那么消耗在漏感吸收電路的能量也就相應減少,從而提高了整機的效率。但因為改進型繞法加了屏蔽層,耦合的緊密程度比普通的PSP繞法差一些,因此效率也相對低一點。

表1 不同變壓器繞法對各參數的影響

2.2 變壓器繞法對EMI的影響

三明治繞法的使用會增加初、次級繞組之間的耦合電容,而繞組間的電容是傳導共模噪聲主要的耦合途徑。另外,它還會與繞組的分布電感構成LC振蕩器會產生振鈴噪聲,所以三明治繞法會使電源的 EMI性能變差。從圖 9(a)和圖 9(b)兩個比較,PSP繞法共模總噪聲比 PS繞法共模總噪聲大10dBuA。經過改進變壓器的繞法,從圖9(c)可以看出,改進型PSP繞法的EMC性能比普通PSP繞法好,改進型PSP繞法共模總噪聲比PSP繞法共模總噪聲小25dB,共模噪聲下降明顯。經過改進變壓器的繞法甚至比PS繞法的EMC性能還好。

圖9 變壓器繞法

3 結論

本文以反激電源為研究對象,通過理論計算和實驗分析變壓器設計對電源整機效率和電磁兼容的影響,得到以下結論:

1)變壓器原、副邊之間的耦合電容是傳導共模EMI的主要傳輸路徑,只要控制有效電容CQ的大小便可以控制共模傳導噪聲總電流的大小達到抑制傳導共模EMI的效果。

2)原、副邊繞組之間的屏蔽層高度具有一個最優值使得傳導共模EMI得到有效抑制,全屏蔽的效果不一定最好。

3)原、副邊繞組之間的屏蔽層接副邊繞組的電位靜點時,其抑制傳導共模EMI的效果比不加屏蔽層還差。因此,反激變壓器原、副邊繞組之間的屏蔽層一般接在原邊繞組的電位靜點上。

4)變壓器若采用普通三明治繞法可以提高電源整機效率,但會惡化傳導共模EMI。在變壓器采用三明治繞法的基礎上,通過增加屏蔽層,并控制屏蔽層與次級繞組之間的距離可以抑制傳導共模EMI,同時提高電源的整機效率。

[1] 林氦, 趙融融, 張軍明, 等. 電容鉗位零電壓開關同步整流反激變流器[J]. 電工技術學報, 2014, 29(4):130-135.

[2] Yu-Kang L, Lin Jingyuan. Active-Clamping ZVS flyback converter employing two transformers[J].Power Electronics, IEEE Transactions on, 2007, 22(6):2416-2423.

[3] Kim M, Jung Y. A novel soft-switching two-switch Fly-back converter with a wide operating range and regenerative clamping[J]. Journal of Power Electronics,2009, 9(5): 772-780.

[4] Zhang Jm, Xie Xg, Jiao Dz, et al. A high efficiency adapter with novel current driven synchronous rectifier[C]//Telecommunications Energy Conference,2003. INTELEC '03. The 25th International, E87-B. 12,2003: 205-210.

[5] 成晶晶, 謝小高, 彭方正, 等. 基于準諧振及同步整流的反激變換器效率研究[J]. 電力電子技術, 2009,43(3): 34-35, 44.

[6] 陳為, 何建農. 電力電子高頻磁技術及其發展趨勢[J]. 電工電能新技術, 2000, 19(2): 30-34.

[7] 羅恒廉, 李智華, 陳為, 等. 高頻磁性元件的繞組設計技術[J]. 電工電能新技術, 2000, 19(2): 61-64.

[8] Mohammadi M, Adib E. Lossless passive snubber for half bridge interleaved flyback converter[J]. Power Electronics, IET, 2014, 7(6): 1475-1481.

[9] Lin Sicong, Min Zhou, Wei Chen, et al. Novel methods to Reduce Common-mode Noise Based on Noise Balance[C]//37th IEEE Power Electronics Specialists Conference, 2006: 2728-2733.

[10] Cochrane D, Chen Dy, Boroyevic D. Passive cancellation of common-mode noise in power electronic circuits[J]. Power Electronics, IEEE Transactions on,2003, 18(3): 756-763.

[11] 林思聰, 陳為. 反激式開關電源共模傳導發射模型的分析與應用[J]. 電氣應用, 2005, 24(2): 119-122,76.

[12] 陳慶彬, 陳為. 開關電源中變壓器共模傳導噪聲抑制能力的評估方法[J]. 中國電機工程學報, 2012,32(18): 73-79.