EnDat2.2通訊協議接口的設計

廖彩霞,賴 歡,董 佳

(重慶望江工業有限公司,重慶 400071)

具有精度高、體積小、抗干擾性好、數字化接口、傳輸可靠性高以及絕對定位等優點的絕對式編碼器目前被廣泛應用于工業和軍事等諸多領域。它通過循環二進制碼(格雷碼)、自然二進制碼或者PRC碼對碼盤上的物理刻線進行光電轉換,然后將連接軸轉動的角度量轉換為對應的電脈沖序列,并以數字量的形式輸出。其數據輸出有并行和串行兩種接口,其中串行方式又分為同步串行接口(SSI)和異步串行接口。SSI接口和在SSI基礎上發展起來的EnDat和BISS接口等在光電編碼器上得到了廣泛的應用。EnDat接口是德國海德漢(HEIDENHAIN)公司設計的數字式、全雙工同步串行的數據傳輸協議,具有連線簡單、精度高、傳輸速率高和抗干擾能力強等優點,是編碼器和光柵尺等數據傳輸的通用接口。

1 EnDat2.2 接口協議

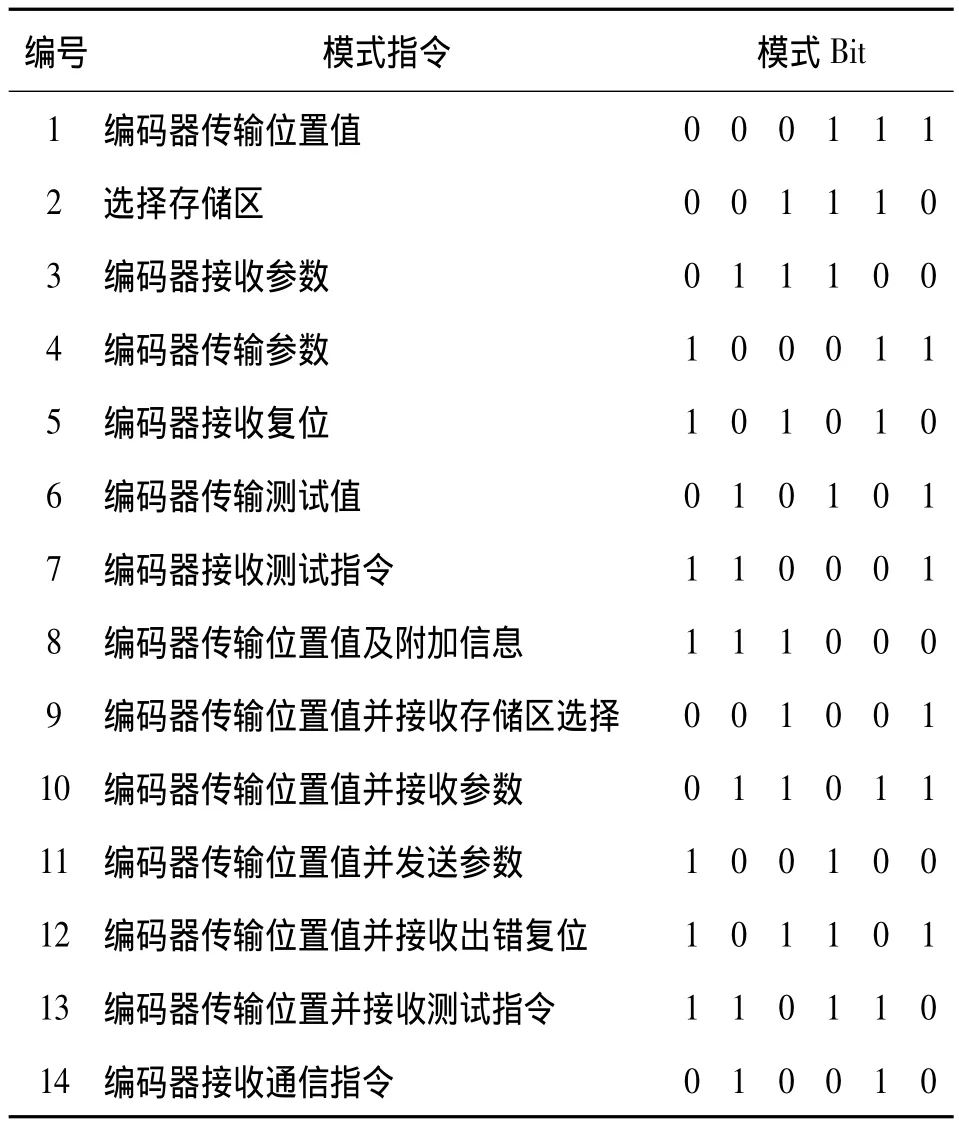

EnDat2.2數字接口傳輸的數據類型分為位置值和附加信息或參數,所傳輸的信息類型由模式指令選擇,模式指令決定被發送信息的內容,每個模式指令包括3位,每位均采用冗余或反向發送,從而保證數據傳輸的準確性。當編碼器檢測到一個錯誤的模式傳輸,它即發送一個錯誤的信息。EnDat2.2接口協議共有14種模式指令,模式指令及含義如圖1所示。

本文以編碼器傳輸位置值為例,編碼器傳輸位置值的模式指令為“000111”,如表1所示。數據包發送與數據傳輸同步,傳輸周期從時鐘的第1個下降沿開始,編碼器保存測量值并計算位置值,2個時鐘周期后,后續通訊轉換接口發送模式指令。當編碼器切換成傳輸狀態后(即10個時鐘周期后),后續通訊轉換接口開始監測數據端的上升沿,第1個上升沿為數據傳輸起始位S。編碼器發送位置值后,從起始位開始向后續通訊轉換接口傳輸數據。后續錯誤位(F1和F2)是檢測類信號,用于監測故障。編碼器從最低有效位(LSB)開始發送絕對位置值,位置值的數據發送以循環冗余校驗(CRC)結束,在數據結尾處,必須將時鐘信號置為高電平,10 ~30 μs或者1.25 ~3.75 μs后(系統時鐘大于 1MHz 時)數據線返回低電平。然后,時鐘信號啟動另一次數據發送。

圖1 模式指令及含義

表1 傳輸位置值的時序

2 接口硬件設計

該接口由CPLD和RS485差分信號接收器、發送器和外部晶振組成。CPLD采用Altera公司的MAXⅡ系列,用于實現EnDat2.2協議解釋和DSP之間的并行通信接口等功能,完成譯碼及位置數據采集的任務。DSP采用TMS320X2812,數據總線寬度為16位,DSP的數據線D0~D15連接CPLD的IO0~IO15,DSP地址線 A0~A3連接 CPLD的 IO16~IO19,DSP外部片選/XZCS0AND1連接CPLD的IO26。由于編碼器數據傳輸信號為差分信號,因此CPLD和編碼器之間通過兩塊差分驅動芯片MAX485_1和MAX485_2來連接。其中,MAX485_1用于發送模式指令和接收編碼器數據,為雙向傳輸。MAX485_2用于發送同步時鐘信號到編碼器,為單向傳輸。同時,該接口還具有數據糾錯處理功能,完全能代替廠家的專用接收芯片,降低產品成本。接口硬件設計如圖2所示。

圖2 通訊接口硬件電路

3 接口軟件設計

3.1 位置采樣原理

為了達到數據同步采樣的目的,CPLD與編碼器采用同一時鐘信號,在編碼器允許的時鐘頻率范圍內,CPLD向編碼器發送采樣時鐘信號,編碼器以此信號為工作時鐘信號,并依據數據傳輸協議在固定的時序上向CPLD傳輸位置數據。同樣,CPLD在固定的時序上接收編碼器發送的位置數據,從而完成一次數據采集。

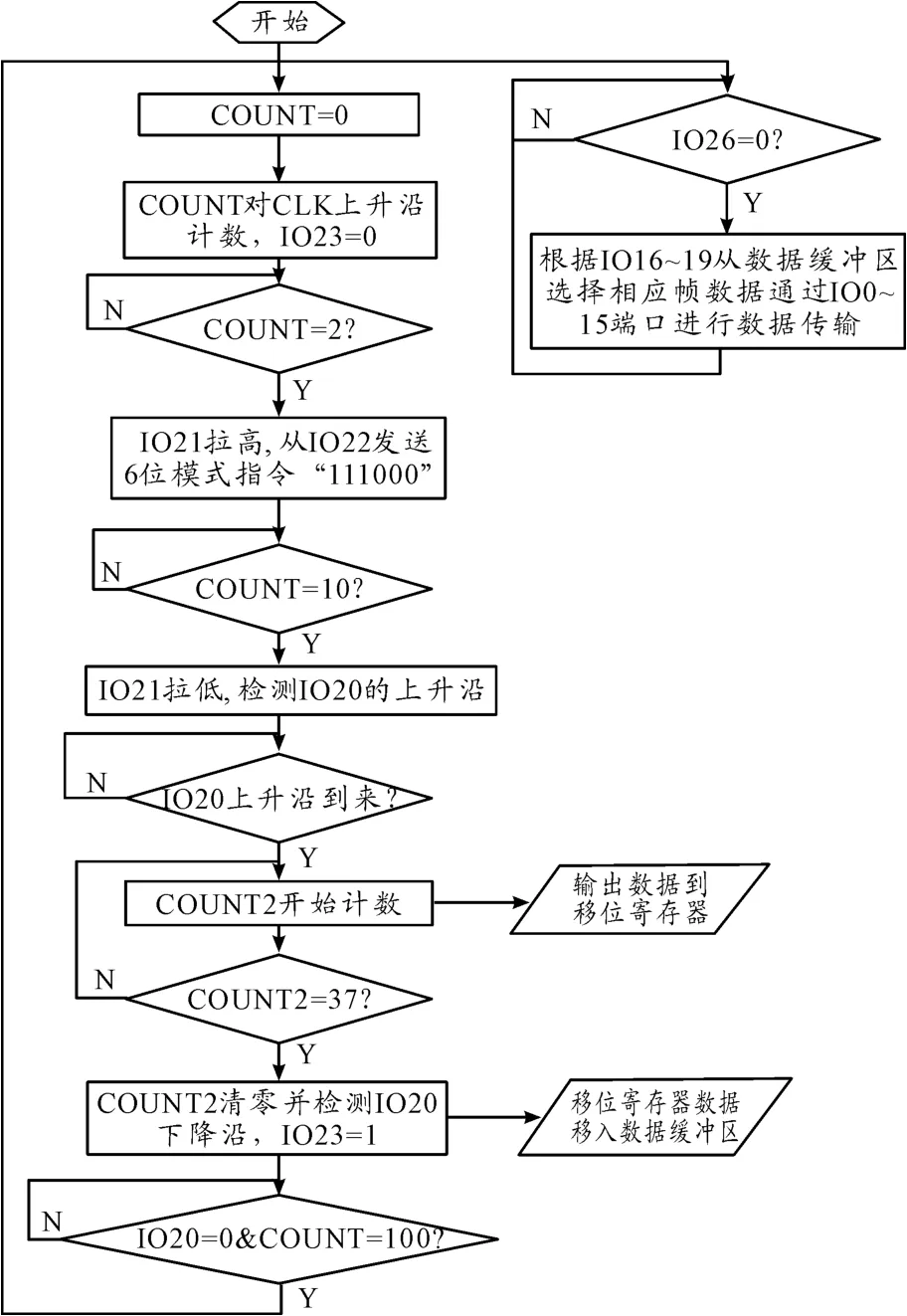

3.2 程序流程圖

該接口的程序流程如圖3所示。

3.3 模塊組成

程序由時鐘發生模塊、計數模塊、與編碼器間的發送/接收模塊、與DSP間的發送/接收模塊、數據緩沖模塊和發送/接收使能模塊6個部分組成。時鐘發生模塊產生周期為1 μs(1 MHz)的方波信號CLK,計數模塊對CLK時鐘信號計數,以判斷數據傳輸進程。

CLK與計數模塊的計數結果產生同步時鐘信號,表1所示“給編碼器的時鐘頻率”,此信號作為與編碼器間通訊同步時鐘,與編碼器間的發送/接收模塊完成與編碼器間的數據交互,與DSP間的發送/接收模塊完成與DSP的數據通訊,按照DSP讀取命令將存儲在數據緩沖區中的位置數據通過計數模塊控制MAX485_1和MAX485_2的發送/接收使能,確保與編碼器間的正確數據傳輸。

圖3 主程序流程

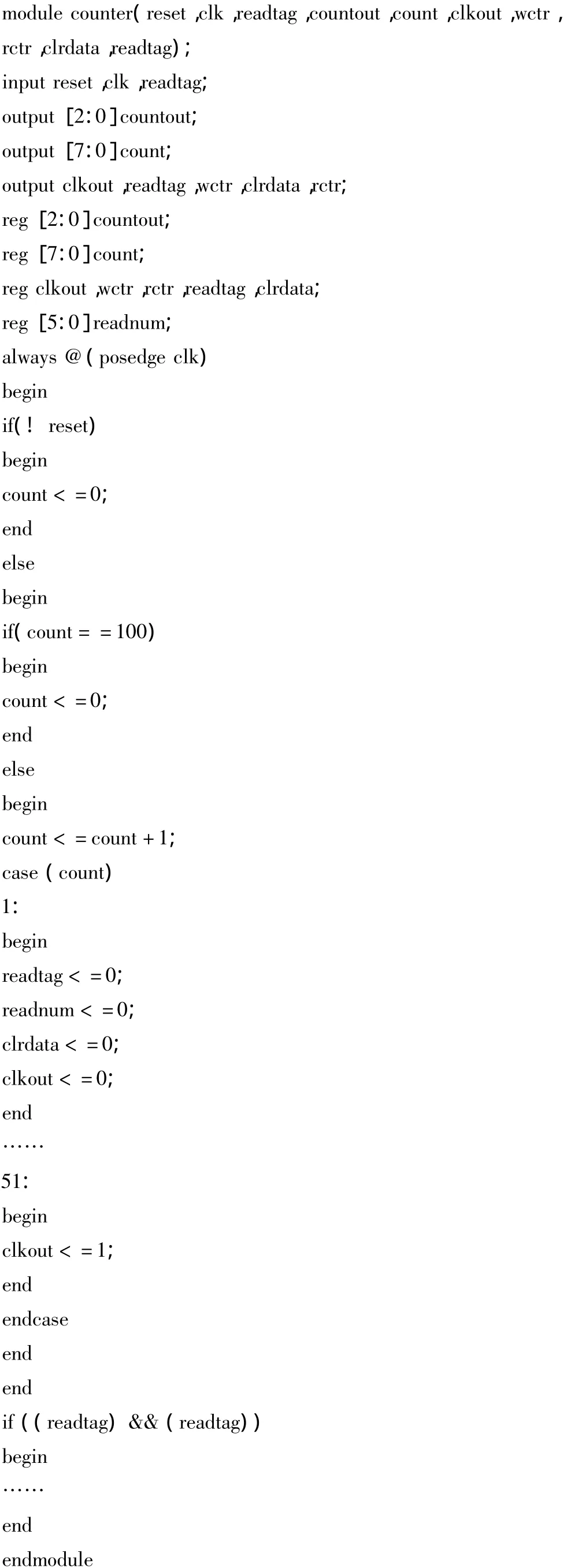

3.3.1 計數模塊

按照表1中EnDat2.2數據協議格式,分析時鐘信號和數據信號的特點,產生適合所選編碼器的時鐘信號和接收數據所需的信號,同步脈沖發生部分以硅振蕩器產生的穩固時鐘源為時鐘信號基準。CPLD對發送給編碼器的時鐘進行計數,在clk的每個時鐘上升沿計數模塊的計數變量count加l,變量count的初始值為0。由于編碼器是在時鐘下降沿讀取數據,為了讓編碼器讀取到穩定狀態的數據,通訊接口需要提前半個周期(時鐘上升沿)將數據發送到與編碼器的數據端口。因此,當計數模塊檢測到count的值為2時,與編碼器間的發送/接收使能模塊使IO21信號電平拉高,使MAX485_1處于數據發送模式,此時,發送模塊開始從數據發送端口IO22發送6位模式指令“000111”。當檢測到count的值為8時,6位模式指令已發送完畢。當檢測到count的值為10時,將與編碼器間的發送/接收使能模塊使IO21信號電平拉低,使MAX485_1處于數據接收模式。此時,開始檢測數據接收端口IO20的上升沿。當第一個上升沿到來時,啟動接收數據計數器count并加1,并將接收到的數據逐位移送到數據緩沖模塊的移位寄存器。當count計數到37時(1位S,1位F1,1位F2,29位D,5位CRC),將移位寄存器中的數據一次性移入數據緩沖區,并將計數器count清零,同時時鐘發生模塊將與編碼器的同步時鐘信號設置為高電平。此時開始檢測數據接收端口IO20的下降沿,當檢測到下降沿到來時,便可啟動新的數據傳輸。計數模塊程序代碼如下:

3.3.2 數據緩沖模塊

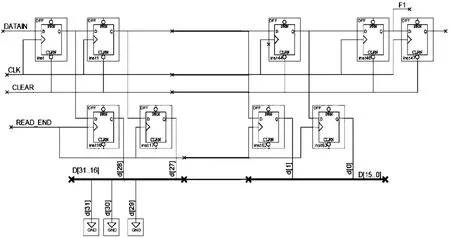

如圖5所示,數據緩沖模塊建立一個數據雙向讀寫通道,由移位寄存器和數據緩沖區兩部分組成,編碼器接收到的串行數據存放到移位寄存器中,完成后同時移入數據緩沖區,供DSP讀取。該模塊將編碼器采集到的數據進行移位處理,輸入信號DATAIN是編碼器回傳的串行數據信號,CLK、READ_END和CLEAR表示同步脈沖發生塊產生的移位、鎖存和清零信號。D[31..16]、D[15..0]為移位處理后發送到DSP的數據,F1是錯誤位,S為起始位,DSP收到F1錯誤標志即放棄讀取當前位置值。

圖4 數據緩沖模塊

3.3.3 程序仿真

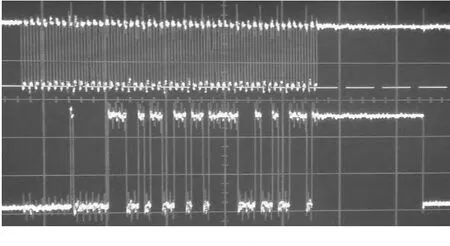

將各個模塊連接在一起后組成頂層模塊,對其進行仿真,仿真波形如圖5所示。其中Clk_in為模擬振蕩器產生的輸入波形,Clk_G為發送給編碼器的同步脈沖時鐘信號,DI_G為發給編碼器的模式指令,從仿真的輸出信號G_BUFFER[31..0]波形圖看,符合Endat接口信號標準,該接口設計達到了預期效果。

圖5 頂層模塊功能仿真波形

3.3.4 測試結果

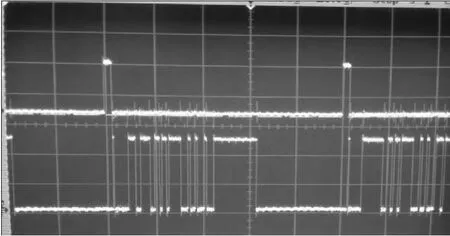

對編碼器進行上電測試。CPLD發送模式指令“000111”和同步脈沖到編碼器,示波器測出的實際波形如圖6~8所示,編碼器出來的位置數據正確,接口工作正常,滿足設計要求。

圖6 時鐘和模式指令之間的時序波形

圖7 時鐘與數據之間的時序關系

圖8 模式指令與數據之間的時序關系

4 結束語

本文設計了一種基于CPLD的EnDat2.2通訊協議接口,實現了串并轉換及譯碼邏輯等功能。該接口還具有數據糾錯處理功能,經過仿真和測試,該通訊接口取得了預期效果,完全滿足DSP和編碼器之間的數據通訊要求,基本能替代廠家的專用接收芯片,降低了產品的經濟成本,該接口設計已經廣泛應用于各種高精度轉臺伺服系統。

[1]林灶生.Verilog FPGA芯片設計[M].北京:北京航空航天大學出版社,2006.

[2]周志煒.基于FPGA的多路光電編碼器數據采集系統[D].哈爾濱:哈爾濱工業大學,2006.

[3]黃正瑾.CPLD系統設計技術入門與應用[M].北京:電子工業出版社,2002.

[4]趙曙光,預萬有,楊頌華.可編程邏輯器件原理、開發與應用[M].西安:西安電子科技大學出版社,2000.

[5]賀敬凱.Verilog HDL數字設計實訓教程[M].西安:西安電子科技大學出版社,2012.

[6]夏宇聞.Verilog數字系統設計教程[M].3版.北京:北京航空航天大學出版社,2013.

[7]程云長.可編程邏輯器件與VHDL語言[M].北京:科學出版社,2005.

[8]EDA先鋒工作室,王誠,蔡海寧.Altera FPGA/CPLD設計:基礎篇[M].北京:人民郵電出版社,2011.

[9]鄭亞民,董曉舟.可編程邏輯器件開發軟件Quartus2[M].北京:國防工業出版社,2006.

[10]馬彧.CPLD/FPGA可編程邏輯器件實用教程[M].北京:機械工業出版社,2006.