一種基于FPGA和ARM的線陣 CCD圖像采集系統設計

嚴帥

摘要: 設計了一種基于Altera的FPGA芯片EP4CE10F17C8以及基于CortexM3構架的ARM處理器STM32F103VE,該系統通過FPGA對線陣CCD進行時序的驅動,并完成像素信號的采集、硬件處理以及傳輸工作。ARM作為FPGA的外掛處理器,實現數據信息的軟件處理以及對整個系統的控制。介紹了該系統的基本原理,并給出了詳細的基于FPGA和ARM的軟硬件聯合設計方案。

關鍵詞: CCD; FPGA; ARM; 軟硬件聯合設計

中圖分類號: TP 39文獻標志碼: Adoi: 10.3969/j.issn.10055630.2015.03.013

Abstract: The CCD driving system is based on a combinational system with Altera FPGA chip EP4CE10F17C8 and ARM processor STM32F103VE which is powered by CortexM3. The system uses FPGA to control CCD by timing drive circuit as well as information acquisition, data processing and data transmission. ARM is used as an external processor for FPGA. It accomplishes data processing based on software and controlling the entire system. The paper introduces the basic principle of the system, gives the results of the design of software and hardware based on FPGA and ARM.

Keywords: CCD; FPGA; ARM; CoDesign

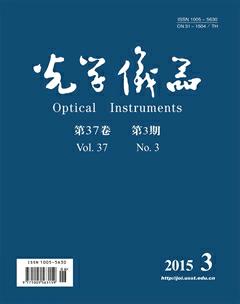

引言CCD(Charge Coupled Device)是一種可以實現光電轉換的圖像傳感器,其將圖像信號直接轉換成電荷信號,后端一般通過調理電路連接至AD轉換器件,從而獲得各像素點對應的數字信號量為嵌入式設備所用[1]。CCD圖像傳感器具有精度高、靈敏度高、自掃描和寬光譜響應范圍等諸多優點,廣泛應用在圖像掃描、條碼掃描、非接觸式位移測量、非接觸式尺寸檢測等工業測量與成像領域[2]。傳統的CCD驅動系統普遍采用單一的MCU或DSP作為整個系統驅動控制的核心,以MCU為例,其信號采集速度較慢,遇到高速信號任務時需要外接FIFO起到數據緩存的作用,處理器功能比較簡單,已經無法滿足應用于現在檢測系統的需求。采用FPGA+ARM作為該類系統的基本構架,可以利用FPGA的靈活性簡化驅動電路的設計,并利用FPGA的并行性提高數據采集處理的速度,同時外掛的ARM芯片作為整個系統的控制器,可以實現一些通用且功能豐富的嵌入式系統應用[3]。1系統組成基于FPGA和ARM的線陣CCD圖像采集系統在硬件上主要包括線陣CCD、CCD輸出信號調理電路、FPGA芯片、ARM芯片、顯示以及數據傳輸接口,其基本的原理框圖如圖1所示。

從圖1可以看出由于系統采用FPGA+ARM的系統構架,整個采集系統可以分為前端和后端兩個部分。系統的前端即FPGA之上的系統主要完成外部芯片驅動以及數據流的采集和緩存功能,FPGA提供CCD、AD芯片正常工作所需的驅動時序。線陣CCD在FPGA的驅動脈沖控制下進行自掃描,每個像素點將進行光電轉換將光信號轉換為電信號,并通過移位寄存器輸出,線陣CCD的輸出信號包含暗電流信號、直流分量信號以及各類噪聲信號,為了取得良好的信噪比需要在CCD輸出的后端接一級信號調理放大電路并配合AD芯片,AD芯片在FPGA產生的采樣時鐘的控制下將CCD的模擬信號轉成相應的數字信號,并通過FPGA進行采集[4]。ARM與FPGA數據的交互主要通過ARM總線接口控制器完成,ARM通過對對應地址的讀寫操作完成采集系統的配置以及數據的采集工作。ARM微處理器采用意法半導體的STM32f103系列芯片,其內核基于CortexM3,具有72 MHz的主頻,存儲容量包括512 kbit的Flash以及64 kbit的RAM,外設方面包括UART、SPI、USB等常用通信接口,可以方便的實現外部各類通信方式,同時該系列芯片具有靜態存儲器控制器(FSMC)可外接片外存儲器芯片,在本系統中,通過將FPGA連接至該控制器,實現ARM與FPGA的數據交互。

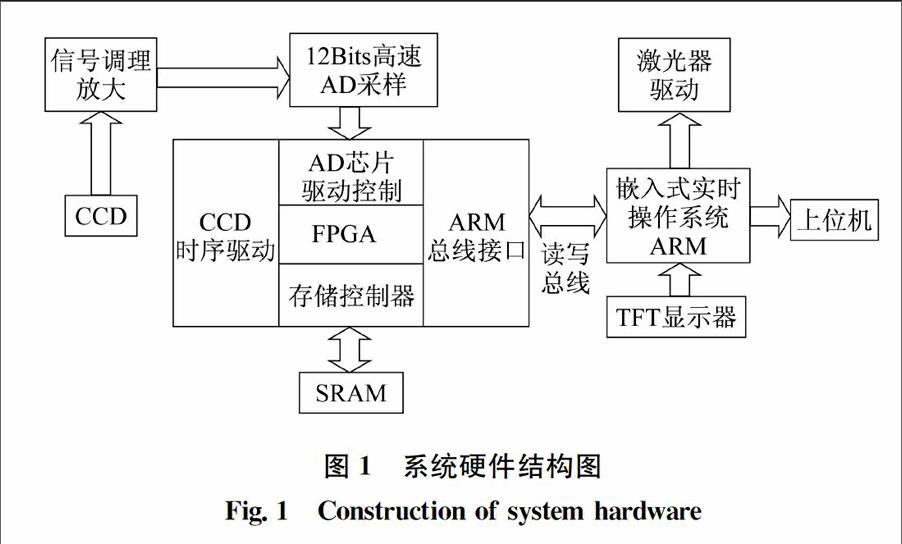

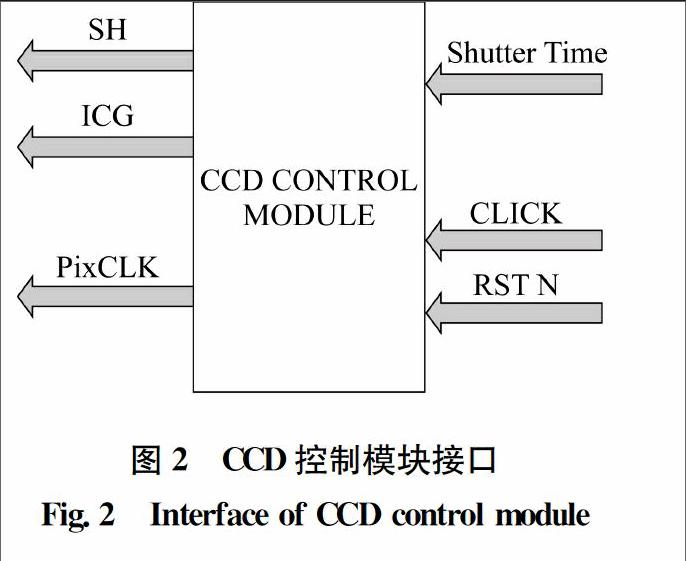

1.1線陣CCD及其驅動設計選用的CCD是TCD1304AP,該線陣CCD為日本TOSHIBA公司生產的一款高速、低暗電流線陣CCD,其內部總共具有3 694個像素,并具有電子快門功能以及采樣保持電路。其中前32個像素以及后14像素為無效像素點用作暗電流的檢測,實際有效像素點為3 648個。TCD1304AP的工作頻率為2 MHz,像素速率為0.5 MHz,接口方面處理提供工作時鐘以外,配合時序要求還需要提供ICG信號以及SH信號,其中ICG信號為幀起始信號,其上升沿的跳變控制一幀信號的開始。SH信號為電子快門功能信號,TCD1304具有獨特的電子快門功能,可由外部驅動時序決定是否開啟該功能,因此該線陣CCD具有兩種工作模式:普通模式、電子快門模式。兩種工作模式的主要區別在于SH信號。模式一中,每個CCD采集周期中間只有兩個SH脈沖信號,其對應的有效光積分時間為第一個SH脈沖的下降沿到后一個SH脈沖的下降沿之間的時間。而模式二中,有效光積分時間為SH脈沖信號的周期。實際上,有效光積分時間其實就是采樣結束后(ICG下降沿標志一幀采樣結束)第一個SH脈沖的下降沿到其前一個SH脈沖的下降沿之間的時間。在模式二中,每個SH信號下降沿之間實際都在進行光信號的采集工作,只是其他這些光電轉換后的信號并沒有被轉移到移位寄存器中得到輸出。CCD器件通過ICG的信號來判斷采集到的光信號是否有效。當ICG信號變為低電平時,CCD內部圖2CCD控制模塊接口的積分清除門將處于開啟狀態,如果在此期間有SH脈沖信號,光敏區域采集到的光電信號將被轉移到移位寄存器,并在ICG重新恢復到高電平之后移位輸出。CCD只有在滿足符合要求的驅動時序下,才能得到良好的工作效果以及可靠的信號輸出。因此,針對CCD的驅動模塊的設計是整個系統是否能獲得有效圖像數據的前提。在FPGA上針對CCD的驅動要求,要設計一個負責用于CCD驅動的模塊,其需要有輸出到CCD的驅動信號,以及系統時鐘的輸入、參數控制信號的輸入(調節電子快門)。該模塊的接口定義和驅動時序仿真圖分別如圖2以及圖3所示。

1.2ARM總線接口設計ARM總線接口用于FPGA與ARM之間進行數據的橋接,通過該接口將數據傳輸給ARM控制器做進一步處理同時接收ARM發來的對應指令并處理。其作為連接這個系統的前端與后端,是本系統在設計上的一個難點。該接口采用3位地址總線,數據總線采用16位數據線連接,即每次讀寫操作都可直接操作16位的數據。同時,總線還包括片選信號CS、讀信號RD、寫信號WR[5]。在STM32端通過其片上提供的靜態存儲器控制器(FSMC)與FPGA相連。

本系統采用用于NOR閃存的控制器時序,工作模式為異步、總線工作方式為非復用,所有的控制器輸出信號由STM32內部時鐘HCLK控制并在其上升沿變化[6]。具體采用FSMC提供的模式A作為實際工作方式。FPGA端只需對對應的時序操作進行解析即可完成數據的讀寫操作。該模塊對應的外部接口框圖如圖4所示。圖4中,DB[0]用于連接前端CCD數字信號的輸出,通過Read Clock控制將數據逐一送到Data Bus總線上,前端的數據輸出模塊實際是一個經過封裝的雙RAM讀寫控制器,其使用的數據存儲器可以是外部SRAM或者是片上通過IP核例化生成的雙口異步RAM模塊。該模塊開辟兩個RAM緩存區,分別用于緩存一幀的像素數據,并通過乒乓操作的方式采集以及送出CCD沒幀的像素數據。本設計中采用兩個大小為4 096、寬度為12 Bits的雙口異步RAM,寫時鐘通過前端采集控制,讀時鐘通過ARM的FSMC控制由FSMC模塊解析后生成對應的讀時鐘信號。2系統的總體設計對各個分模塊進行設計之后需要對整個采集系統進行整合,每個模塊的功能是否健全,輸入輸出是否合理,以及工作時鐘設置等參數是否設置正確對整個系統是否能正確運行至關重要。系統的結構框圖已經在圖1中給出,這里要注意的幾點包括,各模塊的運行時鐘需采用PLL提供的全局時鐘網絡、有效數據的讀取和緩存信號需要考慮到外部器件信號的延遲、存儲器控制器的讀寫等。經過將各模塊進行整合并通過Quartus綜合,最后通過SingalTapII檢驗實際工作情況。3結束語本文著重介紹了如何從系統的角度設計一個基于FPGA和ARM的線陣CCD圖像采集系統,并詳細介紹了CCD驅動的模塊設計以及ARM總線接口的模塊設計,提供了一種在FPGA上構建采集系統的方法,解決了以往采集系統在硬件上過于龐大和復雜的問題,從而達到小型化和智能化儀器趨勢的要求。系統的模塊的劃分具有良好的可替換性,只需稍加修改便能應用到不同類型的外部器件中。外掛的ARM處理器可以彌補所用低端FPGA在硬核處理器上的缺陷,同時滿足通用功能方面的需求,隨著嵌入式微處理器的發展以及對基于嵌入式系統研究的深入,將使得CCD圖像采集系統不論從功能上還是性能上具有更廣闊的發展空間和使用價值。參考文獻:

[1]劉立波.基于DSP的激光三角測距傳感器研究[D].上海:上海交通大學,2008.

[2]李興廣.基于FPGA的高速非接觸式位移測量系統[J].制造業自動化,2011,12(23):2224.

[3]劉爽,趙凱生,龍再川,等.基于ARM和FPGA的嵌入式CCD采集系統[J].電子·激光,2007,18(11):12961298.

[4]劉艷,趙洪,于效宇,等.一種可調線陣CCD信號采集處理系統[J].光學技術應用,2009,32(2):294299.

[5]潘松.EDA技術與Verilog HDL[M].北京:清華大學出版社,2013.

[6]EDA先鋒工作室.Altera FPGA/CPLD設計(高級篇)[M].北京:人民郵電出版社,2011.

(編輯:程愛婕)