基于FPGA的AES加密算法功耗研究

郭正澤,趙紅東,姚奕洋,陳潔萌,馮嘉鵬

(河北工業大學電子信息工程學院,天津 300130)

基于FPGA的AES加密算法功耗研究

郭正澤,趙紅東,姚奕洋,陳潔萌,馮嘉鵬

(河北工業大學電子信息工程學院,天津 300130)

AES(Advanced Encryption Standard)是美國國家標準技術研究所NIST旨在取代DES的21世紀的加密標準.詳細介紹了AES加密的算法原理,實現了基于FPGA平臺AES加密算法的設計與功能仿真.從靜態和動態兩方面分析了功耗的產生原因,研究了基于FPGA平臺的AES加密算法降低功耗的問題,以及隨著時鐘頻率的增加,系統功耗的變化趨勢.算法模塊占用邏輯資源少,加密效率高,并在保證安全性,和滿足應用需求的前提下,實現了平衡數據處理速度和系統功耗這兩個重要參數的目的.

高級加密標準(AES);FPGA;低功耗;時鐘頻率;吞吐量;安全性

AES加密算法安全性好、加密效率高、設計靈活、應用范圍廣,可適用多種安全需求領域.由于硬件實現AES算法相對于軟件來說穩定,速度快,不易受到攻擊.所以用硬件實現AES加密算法成為研究熱點[1-4].文獻[5]使用流水線處理的方法來提高硬件速度,可得到1.94 Gbps的加密速率.但這樣只考慮處理速度,忽略功耗方面的問題,成本較大;又通過對AES算法S盒和列混合變換操作的改進[6],很大程度的提高了算法速率.但這些設計占用邏輯資源過高,因此功耗大,成本也高;而面向實際,考慮在滿足速度需求的情況下以最節約硬件資源的方式實現AES算法,可以達到降低功耗的目的[7].因此,研究滿足一定速度需求的低功耗、低成本硬件加密芯片越來越受到重視[8].

1 AES加密算法總體描述

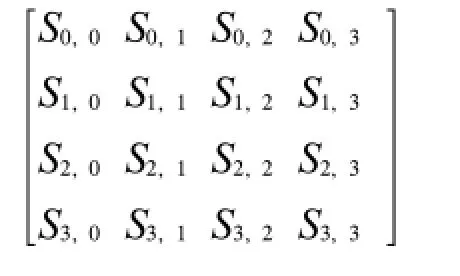

AES加密算法的實現框圖如圖1所示.在此設計中,AES算法的輸入為128位數據,在操作中都是以字節為基礎.按照標準,當輸入為128位時,中間變量由1字節構成.中間變量State用4×4字節矩陣表示[9].

圖1 AES加密算法實現框圖Fig.1 AES encryption algorithm block diagram

字節替代變換(SubByte):字節替代變換是一個非線性的字節替代,使用一個S盒對State的每個字節進行獨立的替換.該S盒是可逆的,由兩個變換復合而成[10].

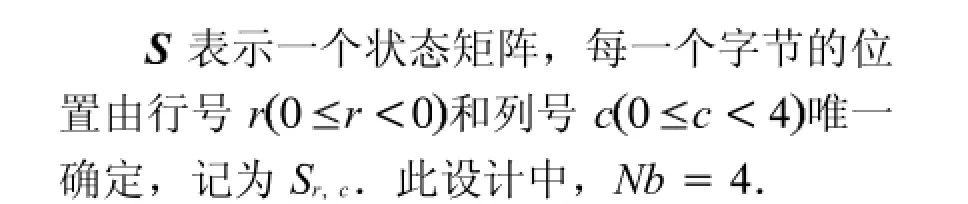

S盒按構造方式如下:

每個中間變量是一個字節(8位),將其初始化為十六進制數據.

把S盒中的每個字節映射為在有限域GF 28中的乘法逆運算,其中,元素{00}映射到它自身.

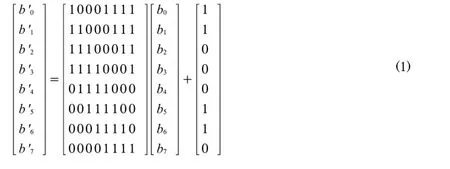

把S盒中的所有字節轉換為二進制數據表示b7,b6,b5,b4,b3,b2,b1,b0,以矩陣的形式,S盒的仿射變換可以表示為

其中b'7,b'6,b'5,b'4,b'3,b'2,b'1,b'0是進行仿射變換后的字節二進制數據表示.

行位移變換(ShiftRow):中間變量的第1行維持原順序,第2行循環向左移動一個字節,以此類推,變換如

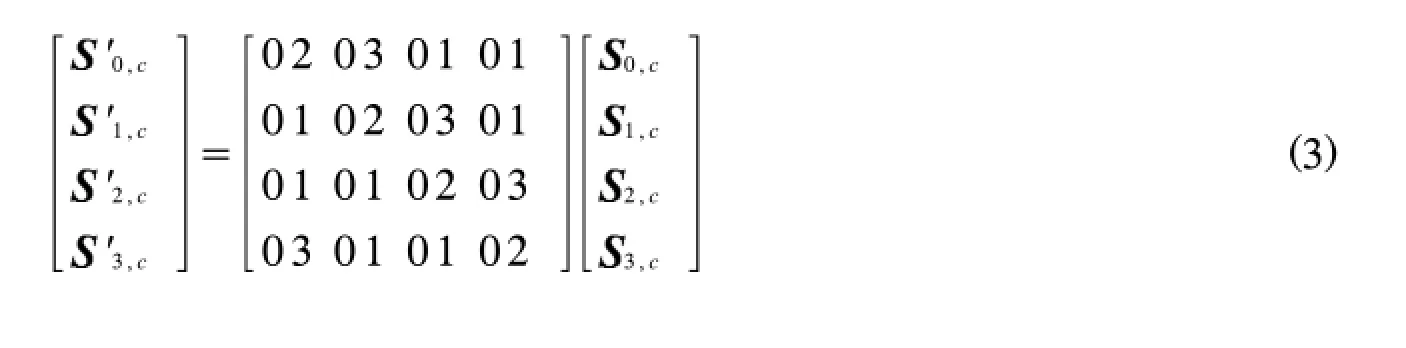

列混合變換(M ixColumns):對一個狀態的每一列去乘一個矩陣,每個列都被看成中GF 28的一個四項多項式,其乘法是在有限域GF 28內進行的,即與固定多項式aχ=03χ3+01χ2+01χ+02模χ4+1乘運算.則列混合變換后的值為S'cχ=Scχaχ.

其矩陣乘法表示如

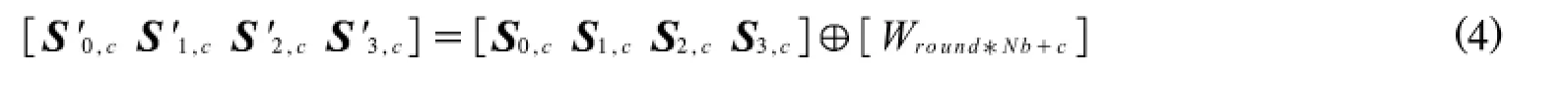

輪密鑰加變換(AddRouondKey):用比特異或將一個輪密鑰作用在狀態上.每一個輪密鑰由通過密鑰擴展算法得到的Nb個字組成,將這Nb個字異或到狀態的列上,即

密鑰擴展算法:密鑰擴展算法中包含Rotword和Subword兩個函數和.Rotword B0,B1,B2,B3類似于行位移操作,對輸入的字節進行左移操作,即Rotword B0,B1,B2,B3=B1,B2,B3,B0.SubWord B0,B1,B2,B3對輸入的字節使用S盒的替換操作SubBytes.

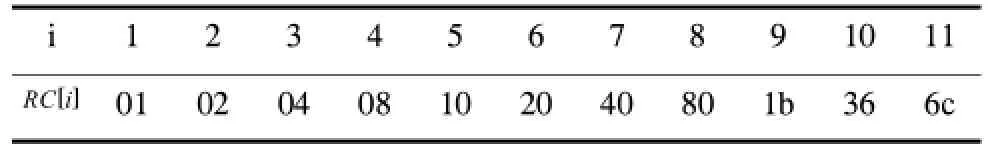

擴展密鑰的前Nk個字就是外部密鑰,后面的字W i是由前面的字W i 1和前第Nk個字W i Nk Subword Rotword W i 1 Rcon i/Nk異或得到.但是若i為Nk的倍數,W i=W i Nk,Rcon i=RC i =RC,'00','00','00'的所有可能值見表1.

表1 數組RC[i]的值Tab.1 The valueof thearray RC[i]

2 功耗的組成

2.1 靜態功耗

靜態功耗一直存在與芯片所處工作、靜止狀態無關.靜態功耗主要是由漏電流引起.隨著半導體工藝不斷先進,晶體管尺寸不斷減小,溝道長度逐漸減小,使得溝道阻抗變小,漏電流變大.此外靜態功耗不僅與工藝有關,與溫度也有很大的關系.

2.2 動態功耗

電容充放電是引起動態功耗的主要原因.很大程度上取決于電壓、工作頻率、負載.增大節點電容,提高工作頻率,內核電壓變大,都會引起動態功耗的升高.FPGA中動態功耗主要表現為內部邏輯、存儲器、時鐘、I/O端口的功耗[11].由于在設計中,靜態功耗隨著芯片的確定而確定,并且靜態功耗在系統的總功耗中占有的比例比較低,所以降低動態功耗是關鍵.

3 加密算法的功能仿真

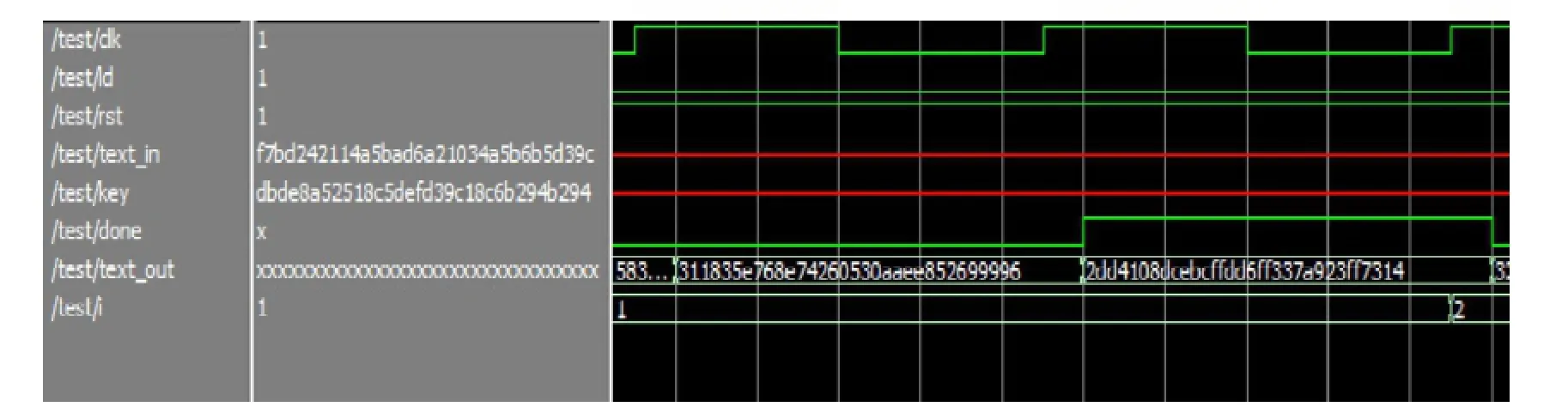

對此加密系統進行功能仿真,并將仿真所得到的結果和所給出的測試數據相比較.圖2給出了該系統在加密過程中的功能仿真結果.仿真時使用的測試數據如下(十六進制表示).

明文:f7bd242114a5bad6a21034a5b6b5d39c;

密鑰:dbde8a52518c5defd39c18c6B294b 294;

密文:2dd4108dcebcffdd6ff337a923ff 7314;

對比所給的測試數據和仿真結果可知,此系統仿真所得到的密文輸出結果與測試數據加密結果一致,能準確的執行AES加密算法.該示例所使用的時鐘頻率為50MHz,在下邊的步驟中,將分別設置不同的時鐘頻率,來進行系統的功耗分析.

4 實驗結果分析

本設計選擇了Altera公司的Stratix系列的EP1S10F780C6型號芯片,其在設計中的靜態功耗為187.50 mW.器件型號選定以后,靜態功耗不會輕易的改變.

引起FPGA動態功耗的因素諸多,文章主要研究了系統時鐘造成的動態功耗.利用Quartus II的PowerPlay功耗分析工具,依據VCD文件可對系統的功耗進行分析.在設置時,選擇run gate-levelsimulationautomatically after compilation選項,同時在nativelink settings選項下指定testbench.在對本設計進行綜合布局布線之后自動進行門級仿真,同時執行生成VCD的tcl文件,這樣就會生成門級的VCD文件,然后用PowerPlay工具加載VCD文件進行功耗的分析.

圖2 功能仿真結果Fig.2 The resultof function simulation

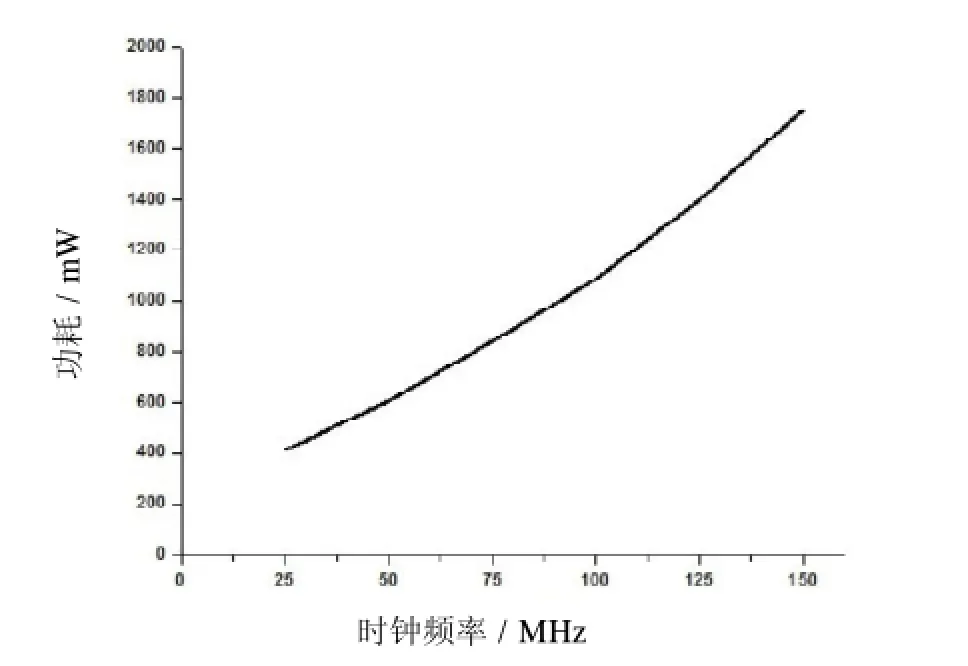

在設計testbench文件時,可設定時鐘每隔N個時間單位,高低電平翻轉一次.時間單位大小可由`timescale指定,2N倍的時間單位大小即為時鐘周期.因此,可通過設定數值N和時間單位大小來設定不同的時鐘周期,得到不同的時鐘頻率.例如文章實驗中通過` timescale來指定時間單位為1 ns,設定N為20,即可得到25MHz的時鐘頻率.可通過類似的方法得到其他需要的時鐘頻率.通過設定不同的時鐘頻率,來進行功耗分析得到的數據如圖3所示.

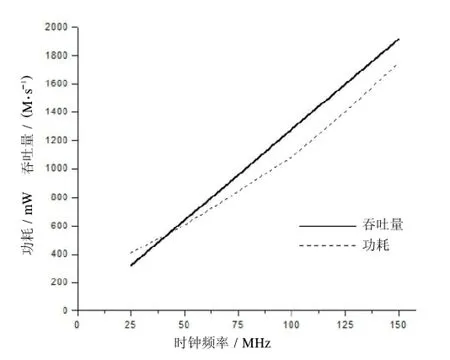

從圖可以看出,總功耗隨時鐘頻率基本成線性變換.可以通過提高或者降低時鐘的頻率來增大、減小系統功耗.但時鐘頻率的變化,不僅會影響到系統的功耗,還會影響系統速度這個重要參數.在AES算法中,數據吞吐量是速度的重要指標.所以,設計者不能一味的為了降低功耗而降低時鐘頻率.需要在功耗和吞吐量之間取得一個最佳平衡點,即合適的時鐘頻率.使得系統在既滿足吞吐量的同時,又不會有太大的功耗.如圖4所示,是吞吐量隨時鐘頻率的變化.并將功耗和吞吐量進行了對比.

圖3 時鐘、功耗關系圖Fig.3 The relational diagram of the clock and power consumption

由于器件型號選定以后靜態功耗基本固定,時鐘頻率在小于40MHz時,由于此時動態功耗還比較小,靜態功耗占有的比例比較大.所以產生相應的吞吐量,所消耗的總功耗也就相對比較大.當時鐘頻率大于40MHz時,隨著時鐘頻率的增大,動態功耗也會隨著增加,靜態功耗所占比例越來越小且小于30%.

總功耗隨時鐘頻率基本成線性變換,然而當時鐘頻率大于100 MHz時,圖3中的功耗線的斜率有較明顯的增大.由此我們可以得出:當時鐘頻率大于100MHz時,要產生相應的吞吐量,就需要消耗較多的功耗.所以如果系統設計沒有要求較高的吞吐量,應該把時鐘頻率控制在100MHz以下.

圖4 功耗和吞吐量隨時鐘頻率變化趨勢Fig.4 The tendency of the power consumption and clock w ith the change of clock frequency

針對AES硬件實現時,不僅要研究信息處理速度,更重要的應該是注重實際應用需求.很多實際應用的數據流量都在400 Mb/s以下,所以不應追求過高的吞吐量而產生過高的功耗.應該在滿足應用需求(速度和安全性)的情況下降低系統功耗.例如在本設計中,如果沒有對系統速度提出過高要求,可以根據需要,在50~100MHz時鐘頻率之間選擇合適的時鐘,以滿足速度和功耗的平衡.

5 結論

文章著重研究了在AES加密系統中,保證安全性和滿足需求的前提下,平衡功耗和速率這兩個重要參數.針對AES硬件實現主要有兩個方向,一是面向信息處理速度,另一個是面向實際應用需求.為了平衡速度和功耗,本系統時鐘頻率應該控制在40~100MHz之間,再根據系統要求的具體速度,來確定具體的時鐘頻率.由圖3可知,當時鐘頻率控制在此頻段時,仍可得到600~1 300M b/s的加密速率,滿足目前網絡上絕大部分用戶需求的千兆和百兆以太網.可見,用本文提供的方法來確定時鐘頻率,在滿足信息處理速度的同時,減小了不必要的功耗.在滿足實際應用需求的同時,實現了速度和功耗兩個參數的平衡.

[1]Li Tao,W ang Yong,Zhou jian,etal.An optimal FPGA implementationofGPON-AES[J].Telecommunications Net-work Technology,2010,10(10):53-57.

[2]Daemen J,Rijmen V.The Design of Rijindael:AES the advanced encryption standard[M].Berlin:Springer-Verlag,2002:31-148.

[3]Biham E,Biryukov A,Sham ir A.Cryptanalysis of skip jack reduced to 31 rounds using impossible differentials[M].Berlin:Springer-Verlag,1997:149-165.

[4]Phan RCW.Impossible differentialcryptanalysisof 7-round Advanced Encryption Standard(AES)[J].Information Processing Letters,2004,91(1):33-38.

[5]Elbirt A j,YipW,Chetw ynd B,etal.An FPGA based performance evaluation of the AESblock cipher candidatealgorithm finalists[J].IEEE Transof VLSISystems,2011,9(4):554-557.

[6]阮曄,張學杰.一種基于FPGA的AES算法的低功耗實現[J].云南大學學報:自然科學版,2007,29(S2):254-258.

[7]張金輝,郭曉彪,符鑫.AES加密算法分析及其在信息安全中的應用[J].信息網絡安全,2011(5):31-33.

[8]Huang Qian shan,JiXiao yong.Design of AESencryptionalgorithm basedon low-cost FPGA[J].Communications Technology,2010,43(9):156-158.

[9]楊軍,余江,趙征鵬.基于FPGA密碼技術的設計與應用[M].北京:電子工業出版社,2012:144-173.

[10]Han Shao nan,LiXiao jiang.Efficientmethodsto implementS-BOX and INVS-BOXin AESalgorith[J].Microelectronics,2010,40(1):103-107.

[11]韓雪,郭文成.FPGA的功耗概念與低功耗設計研究[J].單片機與嵌入式系統應用,2010(4):25-28.

[責任編輯 代俊秋]

The research of the power consumption of the AES encryption algorithm based on FPGA

GUO Zheng-ze,ZHAO Hong-dong,YAO Yi-yang,CHEN Jie-meng,FENG Jia-peng

(School of Electronic and Information Engineering,HebeiUversity of Technology,Tianjin 300130,China)

AES(Advanced Encryption Standard)is an Encryption Standard proposed by American national standards instituteof technology NIST to replace DESEncryption Standard in the21stcentury.Theprincipleof AESencryption algorithm was introduced in detail;the design and function simulation of the AESencryption algorithm based on FPGA platform werecomp leted.Reducing power consum ption of the AESencryption algorithm based on FPGA w asdiscussed. The causes of the power consumption were analysed from static and dynam ic aspects.W ith the increase of clock frequency,the tendency of the system pow er consum ption w as studied,too.A lgorithm module occupies less logical resources,yethashigh efficiency in encryption.Thepurposeofbalancing the tw o im portantparameters-data processing speed and power consum ption has been reached upon the preconditions of guaranteeing thesecurity andmeeting the demand ofmany applications.

advanced encryption standard(AES);FPGA;low power consumption;clock frequency;throughput;security

TP309.7

A

1007-2373(2015)01-0018-05

10.14081/j.cnki.hgdxb.2015.01.004

2014-06-20

河北省自然科學基金(F2013202256)

郭正澤(1989-),男(漢族),碩士生.通訊作者:趙紅東(1968-),男(漢族),教授.