基于HMC983+HMC984套片的頻率綜合器的設計與實現

賈素梅,郭紅俊,楊康,劉欣

(1.河北工業大學信息工程學院,天津 300401;2.邯鄲學院信息工程學院,河北邯鄲 056001;3.中國電子科技集團公司第54研究所,河北石家莊 050081)

基于HMC983+HMC984套片的頻率綜合器的設計與實現

賈素梅1,2,郭紅俊2,楊康2,劉欣3

(1.河北工業大學信息工程學院,天津 300401;2.邯鄲學院信息工程學院,河北邯鄲 056001;3.中國電子科技集團公司第54研究所,河北石家莊 050081)

高性能的頻率綜合器會直接影響到雷達、通信、遙測遙控、電子對抗等電子系統的性能,其主要技術指標包括低相噪、低雜散、小步進、寬頻帶等.本文基于某工程的實際需求,根據鎖相合成技術,采用HMC983+ HMC984套片研制了一款S頻段步進為100 Hz的頻率綜合器,針對設計中小數分頻雜散較高的特點,提出了一種可變參考頻率的方案,通過避開鑒相頻率的整數點有效降低了小數分頻中的雜散,同時,鑒相頻率的提高使得N值降低,相位噪聲惡化減小.測試結果表明,隨著鑒相頻率的提高,N值降低,相位噪聲惡化減小,樣機雜散指標最差點為72 dBc.

頻率綜合器;鎖相環;小數分頻;低雜散;低相噪

頻率綜合器是GSM、CDMA、3G、4G、GPRS、WLAN、藍牙等無線接入技術以及雷達、電子對抗、航空航天等系統中的核心部件,是維持整個電子系統正常工作的關鍵.它的主要性能指標有:寬輸出頻率范圍、低相位噪聲、低雜散、小步進等[1],而小步進、低相位噪聲、寬輸出頻率在鎖相環設計中是相互矛盾的2,小數分頻方案可以解決這一矛盾,但小數分頻固有的雜散問題成為其在頻率綜合器中廣泛應用的制約因素.本文基于HITTITE公司的新型鎖相環(PLL)套片HMC984+HMC983,采用小數分頻方案設計了一種低相噪、低雜散、小步進的S頻段頻率綜合器.

1 主要性能指標與總體方案

本文設計實現了一款S頻段頻率綜合器,主要技術指標為:工作頻率2 520~2 560MHz,步進100Hz,

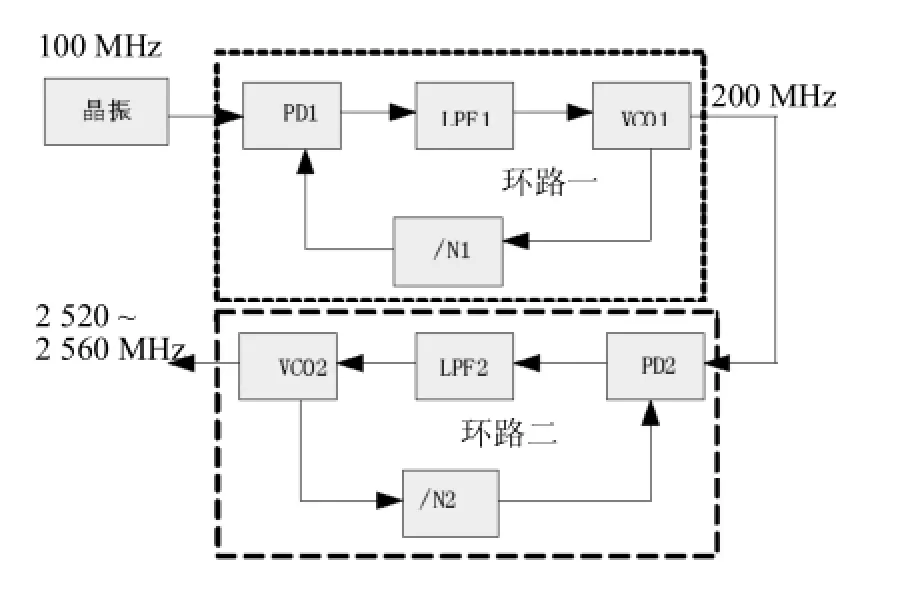

相位噪聲指標95 dBc@10 kHz,雜散指標60 dBc.從技術指標要求可以看出該S頻段頻率綜合器的步進較小,如果采用直接數字頻率合成(DDS)+鎖相環(PLL)的方案雖然可以實現,但頻率成分復雜,組合干擾多,需要大量的濾波放大電路,將導致成本增加,功耗增加,可靠性下降,體積變大.而采用整數單環鎖相環,由于鎖相環中N分頻器的N值非常大,相噪和雜散根本無法保證[3].因此,本設計考慮采用小數分頻鎖相環,但在以往的高指標頻率綜合器的設計中,較難控制的小數雜散會導致小數分頻鎖相環的精度較差,這也成為人們避免采用小數分頻鎖相環的主要原因.在本方案中,首次使用了HITTITE公司的新型低相噪套片HMC984+HMC983[4],完成小數分頻的功能,通過調整鑒相頻率的方法來避開雜散點.實現框圖如圖1所示,該頻率綜合器由雙環實現,即鎖相環PLL1和鎖相環PLL2.PLL1為整數分頻鎖相環,即除N1分頻器的N1值為整數.PLL1由鑒相器(PD 1)、環路濾波器(LPF1)、壓控振蕩器(VCO1)構成,除N1分頻器內置于PD1中,參考輸入頻率為100MHz,輸出頻率為200MHz.PLL1的輸出作為PLL2的參考輸入,PLL2為小數分頻鎖相環,即N2的值為小數.PLL2由鑒相器(PD 2)、環路濾波器(LPF2)、壓控振蕩器(VCO2)、除N2分頻器構成,輸出頻率為2520~2 560MHz.PLL1、PLL2的分頻比N1、N2由單片機控制,由單片機輸出數據改變鎖相環芯片的寄存器來實現100 Hz步進的輸出頻率.這種方案采用頻率成分少,電路實現相對簡單,大大減少了設備量[5],縮小了體積,降低了成本.

圖1 S波段頻率綜合器實現框圖Fig.1 Frequency synthesizer for S-band

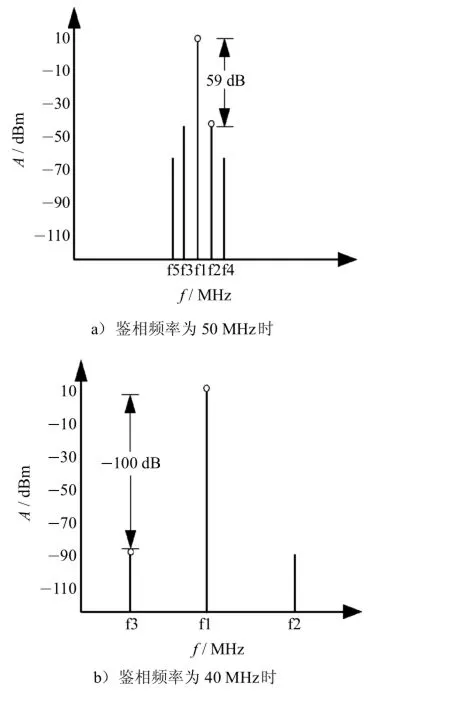

圖2 雜散改善對比圖Fig.2 The comparison of improving spurious

2 小數分頻鎖相環的設計方案

2.1 可變參考頻率降低小數分頻雜散

相比于整數鎖相環,小數分頻鎖相環解決了高鑒相頻率和高分辨率之間的矛盾,但小數分頻的固有雜散問題限制了其在頻率綜合器中廣泛應用,其中單環鑒相頻率的整數邊界點雜散又是影響小數分頻雜散的主要因素,且在距離整數邊界點越近的位置雜散越高.因此,在設計中,提出了一種可變參考頻率的解決方案,大大降低了小數分頻雜散.為了實現較高和可變的鑒相頻率,方案中設計了一個輸出頻率為200MHz的整數鎖相環,以此作為小數分頻鎖相環的參考輸入.通過單片機程序控制小數環鑒相器的除R分頻器的值,設置R值為4或5.這樣,鑒相頻率為50MHz或40MHz,具體分段情況如下:1)輸出頻率為2 520~2 549MHz,R= 4;2)輸出頻率為2549~2551MHz,R= 5;3)輸出頻率為2 551~2 560MHz,R=4.

采用該方案成功避開了整數邊界點,使雜散指標大大改善.采用可變鑒相頻率前后雜散改善對比如圖2所示.在圖2a)中鑒相頻率為50MHz,f1為2 550.1MHz,f2、f3的頻率為f1±100 kHz,f4、f5的頻率為f1±200 kHz.在圖2b)中鑒相頻率為40MHz,f1為2 550.1MHz,f2、f3為f1±1400 kHz左右.由圖可以看出,通過改變鑒相頻率的方法,雜散抑制由59 dB變為100 dB,小數分頻的雜散得到了有效抑制.

2.2 小數分頻鎖相環中的相位噪聲

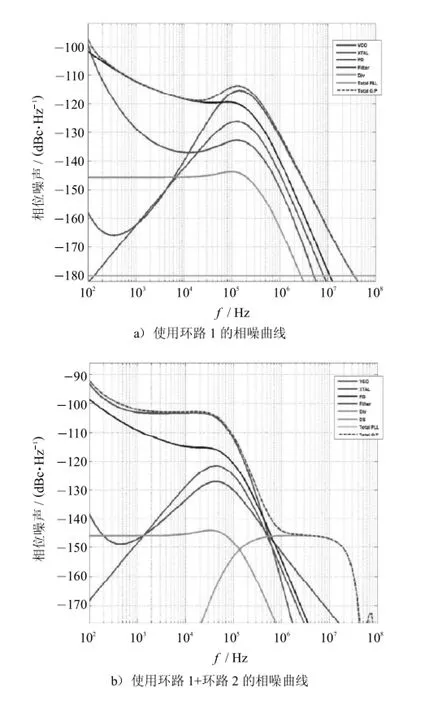

由于環路一的引入,不可避免的會惡化參考源的相位噪聲.針對本方案,使用Hittite PLLDesign工具分析了參考源相噪惡化的程度以及這種惡化對最終輸出相位噪聲的影響.圖3a)給出了僅采用PLL2輸出2550MHz的相位噪聲曲線,圖3b)給出了采用PLL1與PLL2組合輸出2 550MHz的相位噪聲曲線.

通過比較仿真結果,可以看出使用PLL1+PLL2的方案會造成1~100 kHz間的相位噪聲值的惡化,但是惡化的程度不大,而整數邊界點雜散卻得到了有效抑制.由相位噪聲仿真圖可知,該方案的相位噪聲能夠滿足指標要求.在具體PLL1的電路設計中,采用超低基底噪聲的鎖相環芯片(HMC704),超低相位噪聲的VCO(ROS-244+)來獲得更低的相位噪聲.

2.3 小數分頻器與鑒相器芯片的選取

本系統提供的參考源100MHz的頻率準確度為1× 1011,對于整數鎖相環來說,頻率準確度與外源相同.但對于小數鎖相環來說,則取決于芯片中調制器的最大位數,最小頻率分辨率的表達式如下

其中:Ffrac為小數部分的輸出頻率;N為芯片中調制的最大位數.

為了取得更高的頻率分辨率,分頻器采用HITTITE公司2011年12月份最新推出的內置48位調制器的HMC983,該芯片與鑒相器HMC984組合使用[6].小數分頻器HMC983是一款DC-7GHz的小數分頻器,采用SiGe BiCMOS結構,調制的最大位數為48位,最大鑒相頻率為50 MHz,由式1可知最小頻率分辨率為8.89×108Hz,即頻率精度最大為8.89×108Hz,可以滿足一般的工程應用.

圖3 相位噪聲對比圖Fig.3 The comparison of phasenoise

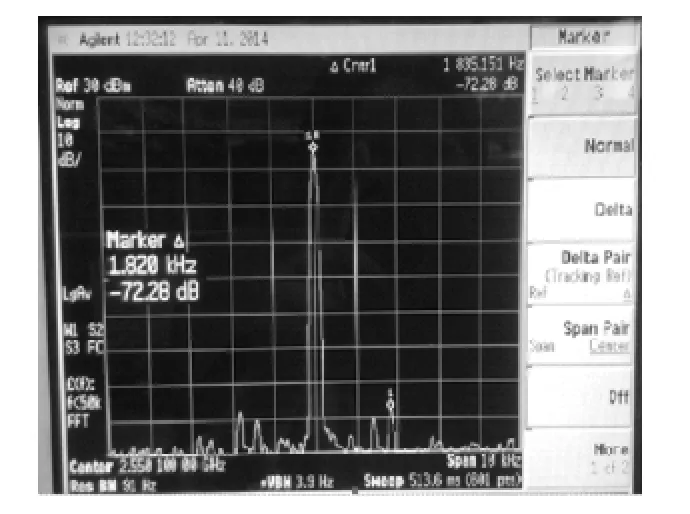

圖4 相位噪聲測試結果Fig.4 The testofphasenoise

3 設計結果

使用E4404頻譜分析儀對設計實物的相位噪聲和雜散進行了測試,分別得到2 550.1 MHz頻點的相位噪聲曲線和40 MHz鑒相、50MHz鑒相的雜散測試結果.從相位噪聲曲線圖4中可看到,在偏離載波100~106Hz頻段內曲線整體較為平滑,表明雜散抑制較好,并且偏離載波100Hz,1 kHz,10 kHz,100 kHz的相位噪聲分別為

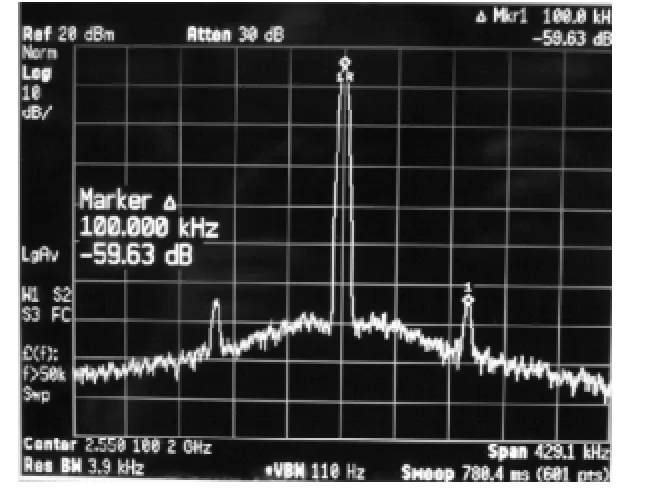

93.20dBc,101.14 dBc,99.49 dBc,108.15 dBc,完全滿足系統提出的相位噪聲指標為95 dBc@10 kHz的性能要求.40MHz鑒相的雜散測試結果如圖5,輸出頻率為2 550.1MHz,雜散抑制為

72dBc,滿足系統60 dBc的要求,輸出頻率為2550.1MHz,鑒相頻率為50MHz時的雜散測試結果如圖6所示,偏離鑒相頻率整數倍邊界點的雜散為59 dBc.從測試結果可以看出,S波段頻綜的相位噪聲與雜散抑制滿足系統指標要求,也證實了該設計方案的可行性.

4 結論

本文詳細介紹了基于HMC983+HMC984套片小數分頻頻率綜合器的設計實現,這種方案的應用改變了超小步進頻率綜合器綜必須采用DDS+PLL實現的局面,對小數分頻鎖相環在工程實踐中的大規模應用提供了指導和借鑒.

圖5 頻率綜合器雜散測試圖Fig.5 The testofspuriousof Frequency synthesizer

圖6 整數邊界點雜散測試圖Fig.6 The testof spurious spectrum at integral

[1]茅敏.HF-S波段頻率綜合器的實現技術研究[D].四川:電子科技大學,2013.

[2]莊卉,黃蘇華,袁國春.鎖相與頻率合成技術[M].北京:氣象出版社,1996:69.

[3]劉愿.基于Sigma-delta調制器的小數N頻率綜合器設計[D].陜西:西安電子科技大學,2009.

[4]Hittite Integrated Products.HMC830Datasheet[EB/OL].2014-04-03.http://www.aa. Washington.edu/AERP/CRYOCAR/Papers/sae97.pdf.

[5]劉欣.基于DDS+PLL組合的高性能頻率綜合器研究[C]//第26屆全國通信與信息技術學術年會論文集.云南:無線通信專業情報網,2011,11:333-335.

[6]HittiteProductApplication Note.Lock DetectControlofPLLs-VCOs[EB].2014-10-21.http://www.aa.Washington.edu/AERP/CRYOCAR/Papers/sae97.pdf.

[責任編輯 代俊秋]

Design and implementation of frequency synthesizer by HMC983+HMC984

JIA Sumei1,2,GUOHongjun2,YANG Kang2,LIU Xin3

(1.Schoolof Information Engineering,HebeiUniversityof Technology,Tianjin 300401,China;2.Schoolof Information Engineering, Handan College,HebeiHandan 056001,China;3.The54th Research InstituteofCETC,HebeiShijiazhuang 050081,China)

Abstrcat The performanceof radar,communication,telecontroland telemetering,electronic countermeasuresandother electronicsystems is im pacted directly by thehigh performance frequency synthesizers,itsperformance indicators include: low phasenoise,low spurious,smallstep,andw ideband.Thepaper issupported by aprojectdemand,using the theoretical analysis of phase-locked loop(PLL);The Sband frequency synthesizer is developed by HMC983+HMC984,and the frequency step of the Sband frequency synthesizer is 100Hz.This paper introducesa solution of fractionalPLL tomeet w ith the frequency step demand.A reference frequency changed solution isproposed to overcome thehigh spurious level of the fractionaldivider.The spurious level can be reduced by avoiding the integer pointsof PD frequency,Meanwhile, the phasenoisedeterioration easesw ith the decreasingof N-dividerdueto the increasingofPD frequency.The testresults show the largestspuriousof prototypemachine is-72 dBc.

frequency synthesizer;phase-locked loop(PLL);fractional-N;low spurious;low phasenoise

TN911.72

A

1007-2373(2015)02-0016-04

10.14081/j.cnki.hgdxb.2015.02.004

2014-11-10

河北省應用基礎研究計劃重點基礎研究項目(13960306D);河北省自然科學基金(F2014109015)

賈素梅(1981-),女(漢族),講師,博士.

數字出版日期:2015-04-16數字出版網址:http://www.cnki.net/kcms/detail/13.1208.T.20150416.1151.011.htm l