基于雙DSP和FPGA控制器的大功率電壓暫降儀設計

張華贏,李 翔,朱正國,姚森敬,史帥彬,黃力鵬,歐陽森,曾 江

(1.深圳供電局有限公司,廣東 深圳518020;2.華南理工大學 電力學院,廣東 廣州510640)

1 引言

隨著科技和經濟發展,以計算機、可編程控制器、嵌入式系統為核心的精密設備等敏感負荷大量接入電網,這些設備對電壓質量的要求非常高,主要由系統故障引起的電壓暫降,往往會導致敏感設備異常工作甚至死機,因而造成巨大的損失[1-2]。因此,電壓暫降造成對用電設備特別是敏感設備造成的影響已成為電能質量領域研究的熱點課題[3-5]。在研究電壓暫降對用電設備產生的影響時,有時需要測試用電設備在電壓暫降條件下的工作情況。然而,在實際過程中,要電網產生特定持續時間與波形的電壓代價很大且很難達到。因此,研制可產生特定電壓波形的裝置就顯得尤為重要。

目前,電壓暫降發生儀(電壓暫降儀)、電能質量信號發生器、電能質量干擾發生器等裝置均可產生所需的電壓波形,為測試用電設備的實驗提供條件[6-12]。文獻[6-7]研制的電壓暫降發生儀雖然采用數字信號處理器(DSP)控制電子器件的開斷,但由于其原理的限制,控制存在不夠精確、不夠靈活等不足。文獻采用單片機作為控制器,同樣由于原理限制,缺乏精確性和靈活性。文獻[9-12]基于逆變器結構,采用DSP控制,具有快速、精確、靈活等優點,但受限于DSP性能,單DSP控制器如要同時兼顧運算、輸出、故障檢測、人機交互等功能要求,必然導致控制周期延長和控制精度降低。

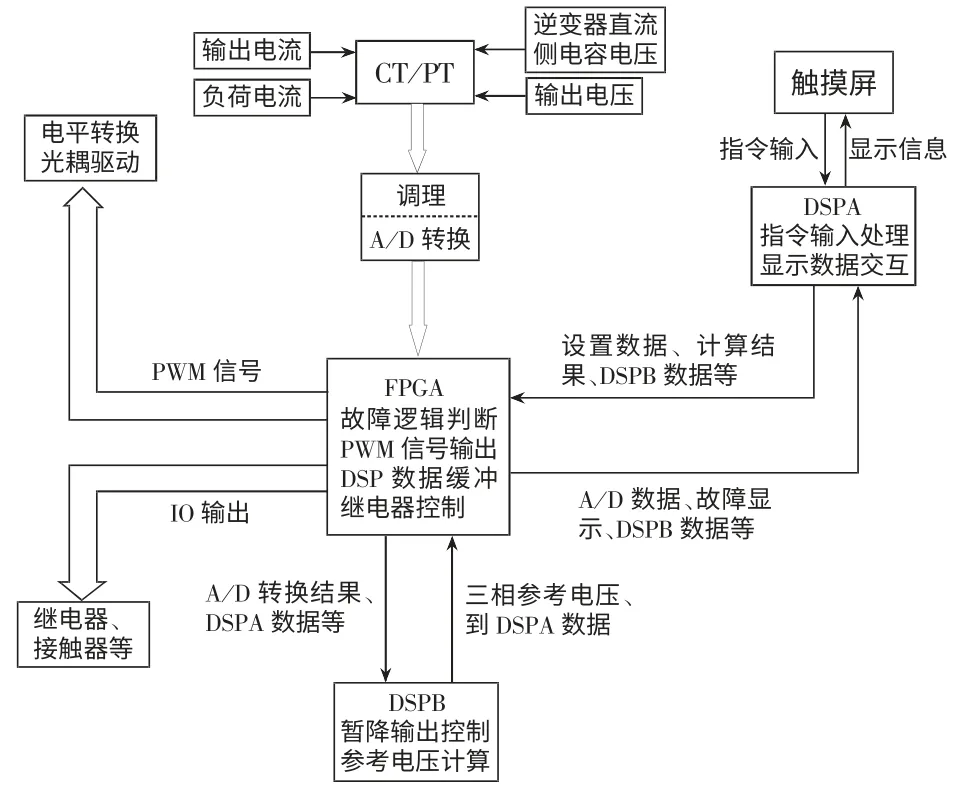

因此,為了進一步提升電壓暫降儀的性能,實現多功能、智能化控制等設計要求,本文設計了基于雙數字信號處理器(DSP)和現場可編程邏輯門陣列(FPGA)架構控制器的電壓暫降儀,其控制器采用“雙DSP(F2812)+FPGA”架構,一個DSP(稱為DSPA)負責處理數據顯示與數據輸入,一個DSP(稱為DSPB)負責產生參考波形并對輸出波形進行控制,現場可編程邏輯門陣列(FPGA)負責控制模數(A/D)轉換芯片工作、逆變器IGBT驅動信號的生成與全系統的故障檢測,一旦有故障可瞬時執行保護程序,不受DSP工作狀態影響。三者分工明確,使全系統的運行效率明顯提高。

2 主電路拓撲設計

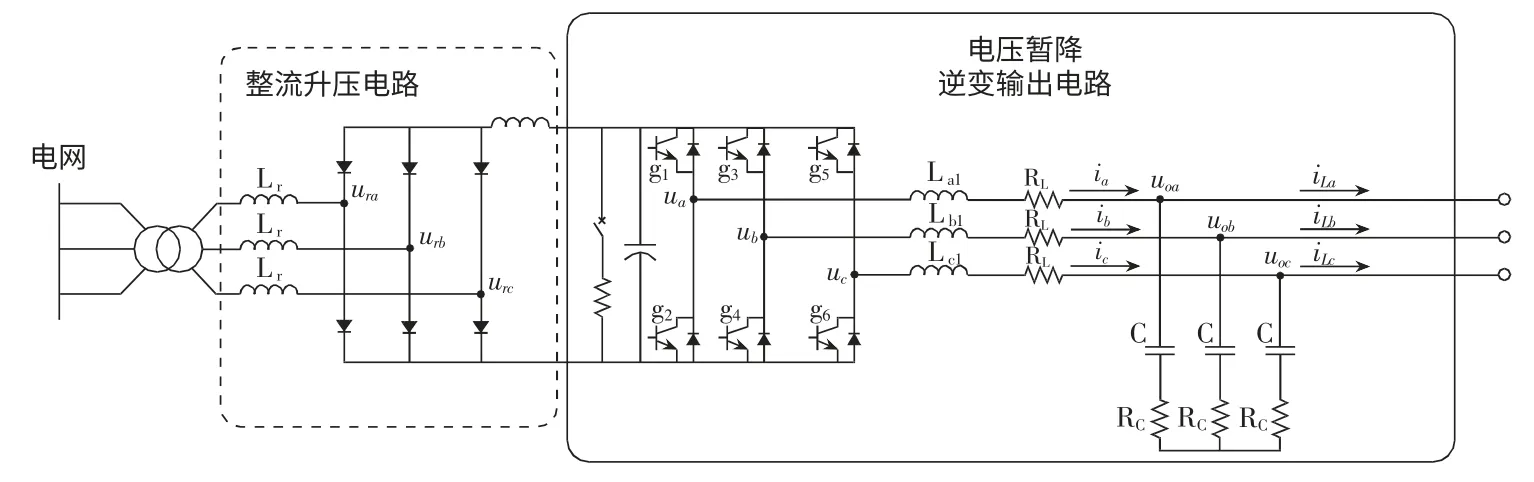

電壓暫降發生儀的主電路由整流升壓電路和電壓暫降逆變輸出電路兩部分采用“背靠背”的方式連接組成。前端為整流升壓電路,采用三相不可控整流電路進行整流升壓。電網通過一個升壓變壓器接于三相不控整流橋的交流側,直流側經一平波電抗接于電容器兩端。后端為電壓暫降逆變輸出電路,控制系統輸出的脈沖經驅動電路控制功率開關IGBT的通斷,經LC濾波器向負載提供指定電壓和電流。

實驗電路拓撲如圖1所示,本文采用LC濾波器作為輸出濾波器,其中La1、Lb1、Lc1均取190μH,RL為輸出濾波器電感的等效電阻,C 取60μF,Rc取0.11Ω,Rc用于停機時消耗直流側電容能量市電經調壓器升壓后,通過三相整流橋給逆變器直流側電容充電,充電完成后由控制器控制逆變器輸出電壓,輸出端接電阻負載。

圖1 電壓暫降儀拓撲結構圖

3 雙DSP和FPGA控制器設計

3.1 控制器硬件系統設計

本文設計的電壓暫降發生儀的控制器采用“雙DSP+FPGA”架構。其中,DSP是TI公司的TMS320F2812芯片,這是一款針對數字控制所設計的32位定點型DSP,具有強大的數據運算能力,主頻最高達150MHz,廣泛應用于嵌入式控制領域。FPGA是XILINX公司的XC2S200芯片,是一種可編程使用的信號處理器件,用戶可通過改變配置信息對其功能進行定義,以滿足設計需求,其內部有豐富的BRAM、GCLK、各種直接可利用的IP核等資源,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點,有效提高了設計的靈活性和效率。

為了提高電壓暫降儀控制器的運作效率及實時反應速度,應充分發揮FPGA邏輯判斷的優勢,應用其進行多種故障邏輯判斷和IO輸出。同時,應充分發揮DSP強大的數據運算能力,應用其進行精確的輸出控制。因此,對FPGA和兩塊DSP應作功能分配,圖2為電壓暫降儀控制器架構框圖。

FPGA主要有四方面功能:一是控制A/D轉換芯片,對外部CT/PT及調理電路后的電壓電流信號進行模數轉換并讀取結果,同時把結果傳送給DSPA和DSPB;二是作為DSPA和DSPB之間的數據交換通道;三是逆變器IGBT驅動信號輸出;四是進行全系統故障檢測及IO控制輸出。

DSPA主要負責與人機界面通訊及數據管理。DSPA讀取FPGA中的電壓電流數據和故障狀態等信息在人機界面中顯示,并傳送人機界面中的命令。

DSPB主要負責控制電壓波形的穩定精確輸出。DSPB通過FPGA與DSPA進行數據交互,讀取觸摸屏輸入的指令生成指定的電壓參考波形,并讀取FPGA中的模數轉換結果,作為電壓外環電流內環雙閉環控制器的輸入,實時控制輸出電壓,并把比較值傳輸到FPGA,和FPGA產生的三角載波進行比較得到PWM信號,PWM波經驅動模塊輸出驅動信號,控制IGBT的開通與關閉,經LC低通濾波器產生符合要求的三相交流電壓,實現所需電壓的穩定精確輸出。

圖2 電壓暫降儀控制器架構框圖

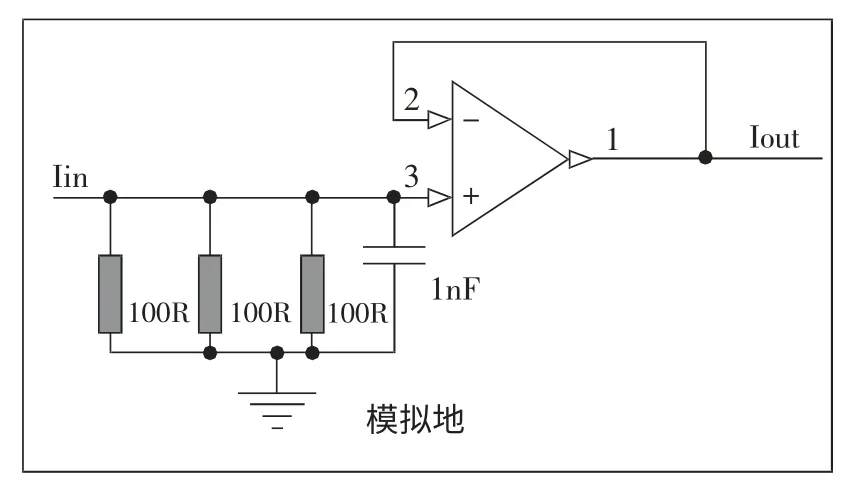

3.1.1 電壓電流轉換及調理電路

為了把電流信號轉換成可作為A/D轉換芯片輸入的電壓信號,需要設計電流調理電路對經過電流傳感器后的信號進行處理。圖3為逆變器輸出電流的調理電路。圖中運放采用LM258,1、2、3號管腳分別為運放的輸出端、反向輸入端、同相輸入端。以A相電流為例,逆變器輸出電流經過霍爾傳感器后得到小電流信號Iin,Iin通過并聯于運放同相輸入端的3個100Ω電阻轉換為電壓信號,經過運放構成的電壓跟隨器后,最終得到適用于A/D轉換芯片的電壓信號Iout,其范圍為-5V~5V。

圖3 逆變器輸出電流的調理電路

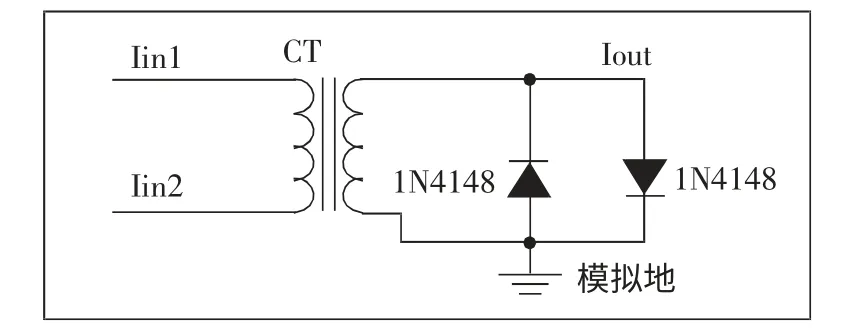

為了提高實際應用過程中使用的靈活性,對于負荷電流,可采用不同的外接電流互感器進行測量,本文設計要求外接電流互感器二次側額定輸出為5A,互感器二次側輸出電流需經板上CT進行再次轉換,本文采用的板上CT變比為5A/2.5mA,負荷電流轉換電路如圖4所示,Iin1、Iin2分別接外接電流互感器二次側兩端,Iout為變換后的電流信號。

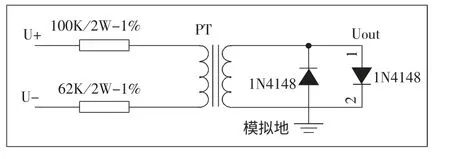

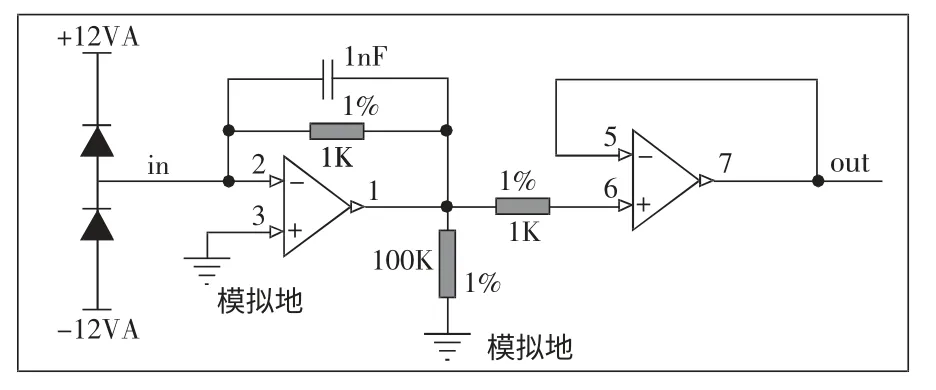

對于輸出電壓,本文采用圖5所示的電壓電流轉換電路把電壓信號轉換為電流信號,圖中PT變比為2mA/2mA,U+、U-為輸出電壓信號,Uout為與輸出電壓等比例的電流信號。圖6為負荷電流、輸出電壓的調理電路。該電路輸入為圖4的Iout或圖5的Uout,輸出為-5V~5V的電壓信號,作為A/D轉換芯片的輸入信號,圖中運放采用LM258雙運放模塊,1、2、3、5、6、7均為引腳編號,其中輸出引腳為1、7,同相輸入端為3、5,反向輸入端為2、6。

圖4 負荷電流轉換電路

圖5 電壓電流轉換電路

圖6 負荷電流/電壓的調理電路

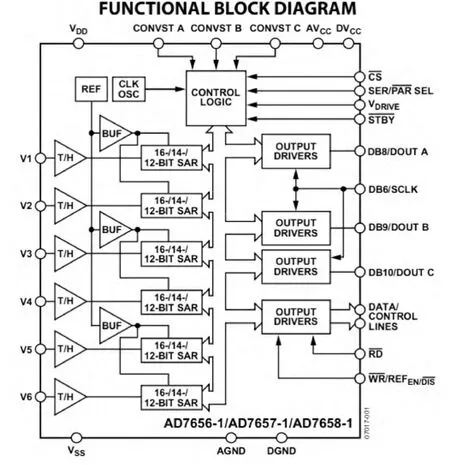

3.1.2 模數轉換電路

基于本文架構設計的控制器為數字控制系統,因此必須把電流、電壓信號模擬量轉換成數字量。電流、電壓的轉換用于輸出電壓的雙閉環控制,實現電壓波形的精確穩定輸出。另外,相關數據用于觸摸屏上的顯示。本文設計的采樣頻率為25.6kHz,對工頻電壓、電流信號每個周波(20ms)采樣512個點。A/D轉換芯片選用AD公司推出的AD7658模數轉換芯片。該芯片模擬信號輸入范圍為-5V~5V,可支持6通道12位的高速采樣轉換,轉換速率達250ksps,可完全滿足要求。圖7為AD7658的功能框圖。

圖7 AD7658的功能框圖

3.1.3 驅動電路

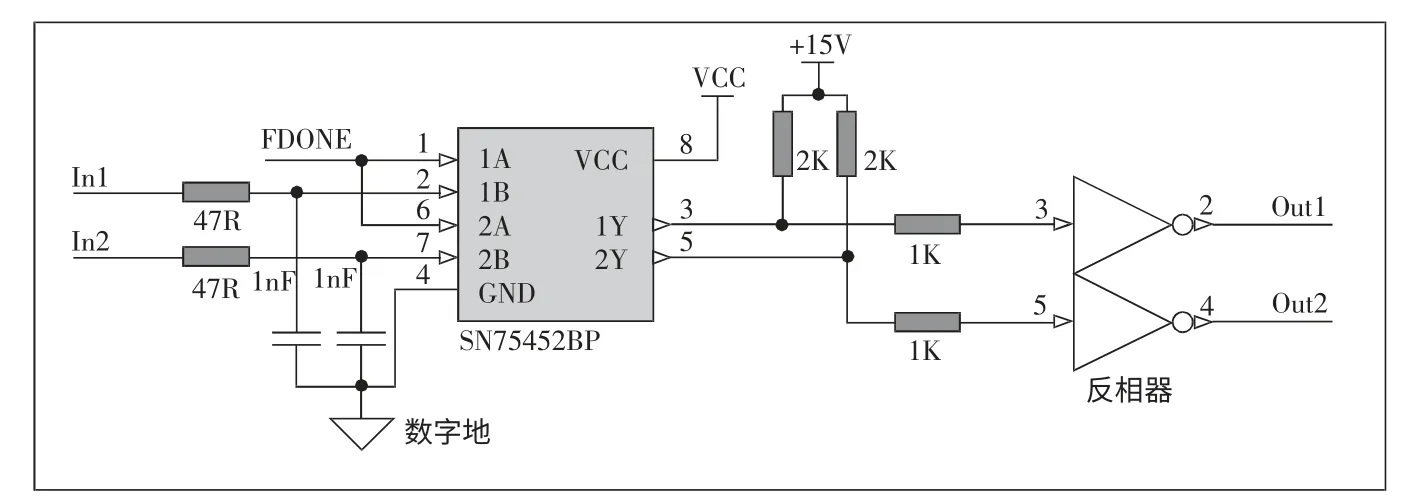

FPGA的引腳電壓為0或3.3V,不足以驅動IGBT工作,故要把其引腳電壓轉換后輸出到IGBT的驅動電路,從而控制IGBT的開斷。

圖9 電平轉換電路

電平轉換電路如圖8所示,圖中In1、Iin2為FPGA輸出的同一相的上、下IGBT PWM信號,FDONE為封鎖信號,Out1、Out2為經電平轉換后的上、下IGBT控制信號FPGA輸出的PWM信號,經光耦電路轉換成0或15V。Out1、Out2經M57962L 集成電路模塊產生IGBT的驅動信號,直接控制IGBT的開斷。IGBT的驅動電路如圖8所示,圖中C1、G1、E1分別接IGBT的集電極、門極、發射極。

圖8 IGBT的驅動電路

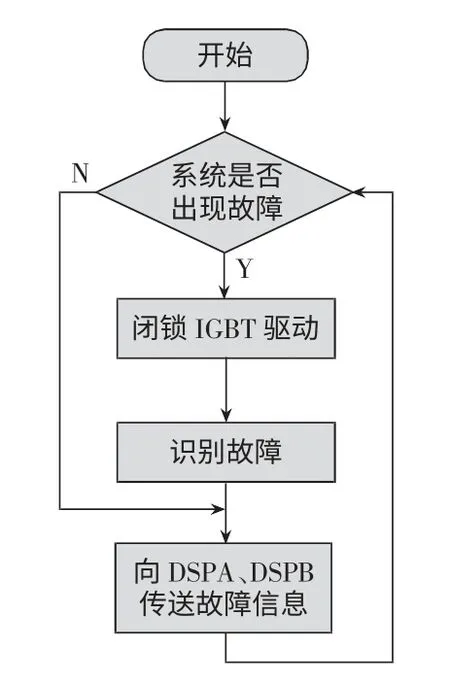

3.1.4 故障檢測電路

FPGA負責檢測全系統的故障并作出迅速反應。當出現直流側過壓或欠壓、輸出電流過流、AD轉換芯片工作異常、DSP工作異常等故障時,FPGA經內部邏輯判斷將作出故障處理,通過圖9所示的FDONE信號封鎖IGBT輸出的同時并將故障情況顯示于觸摸屏。其中DSP工作檢測和AD轉換芯片檢測由軟件程序完成,過壓欠壓檢測和過流檢測需設計一定功能的前置電路,使故障電平信號能轉換成可直接輸入FPGA的信號,以便FPGA進行實時監測。

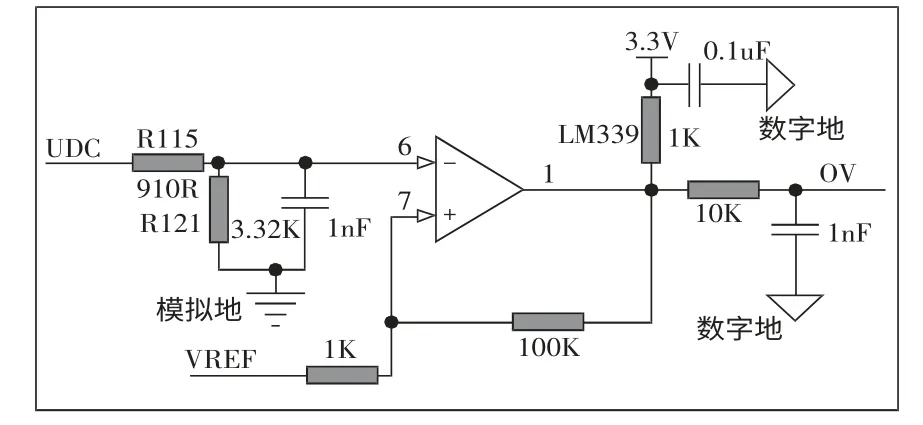

(1)過壓欠壓檢測

本文的電壓暫降儀為電壓源型逆變器,輸出指定電壓前,要確保直流側電容上的電壓已經穩定在所需范圍,若存在欠壓現象,則不能保證有效輸出,若存在過壓,則可能導致功率器件的燒壞、電容爆炸等危險。因此,必須對直流側電容的電壓進行實時檢測,迅速處理故障。

圖10為過壓檢測電路。其中,UDC為直流側電壓經霍爾傳感器后的值,根據設計,UDC為實際電壓的0.00503倍。UDC經電阻R115和R121分壓后,與基準電壓VREF=3.3V比較,過壓時OV為低電平,正常時為高電平。經計算可得,過壓臨界值為835V。

在圖11所示的欠壓檢測電路中,基準電壓VREF經電阻R116和R122分壓后與UDC進行比較,由電路原理可知,欠壓時UV為低電平,正常時為高電平。經計算可得,欠壓臨界值為298V。

必須清醒地把握打贏打好脫貧攻堅戰面臨的困難和挑戰,切實增強責任感和緊迫感,一鼓作氣、精銳出戰、精準施策,以更有力的行動、更扎實的工作,集中力量攻堅,確保堅決打贏打好脫貧這場對我省如期高水平全面建成小康社會具有決定性意義的攻堅戰。

圖10 過壓檢測電路

圖11 欠壓檢測電路

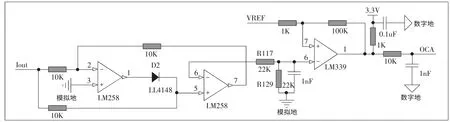

(2)過流檢測

輸出電流過大時,可能導致功率開關的燒壞等一系列損壞。因此,為了保證電路的安全可靠,必須實時對輸出電流進行檢測,以便迅速處理故障并報警。

圖12 過流檢測電路

圖12為過流檢測電路。圖3所示輸出電流調理電路的輸出信號Iout作為圖12電路的輸入。檢測過流時要檢測電流的峰值,要保證電流最大時不出現過流。因此,Iout首先要經過整流環節,然后再與參考電平比較。Iout整流后經電阻R117和R129分壓,然后與基準電壓VREF進行比較。過流時OCA為低電平,正常時為高電平。結合CT變比(2000:1)和調理電路,經計算可得輸出電流過流臨界值為396A(峰值)。

3.2 控制器軟件系統設計

3.2.1 FPGA程序設計

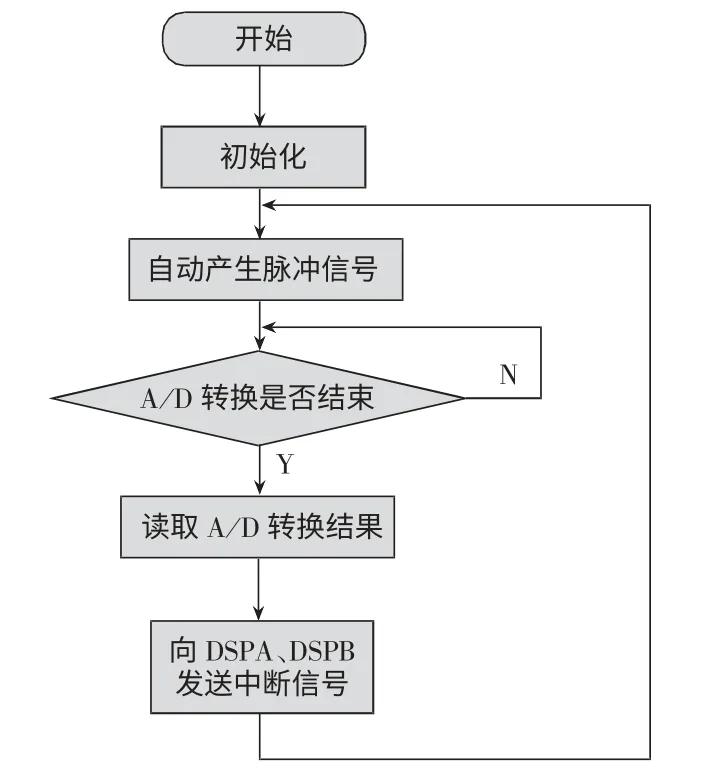

FPGA將由內部的計數器產生一系列的原始中斷脈沖信號,此脈沖頻率與采樣頻率一致,為25.6kHz,為了保證在每個中斷周期內A/D轉換芯片的模數轉換結束后DSPB和DSPA才工作,此脈沖信號寬度為10μs。

此脈沖信號將控制A/D轉換芯片、DSPB和DSPA協調可靠工作。

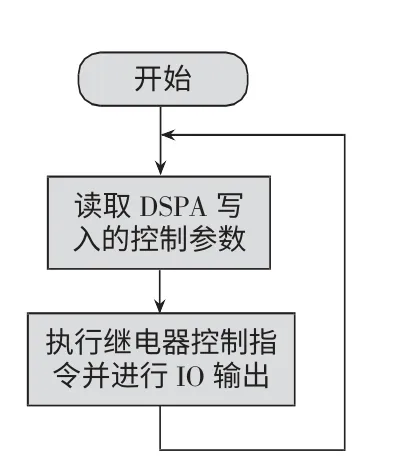

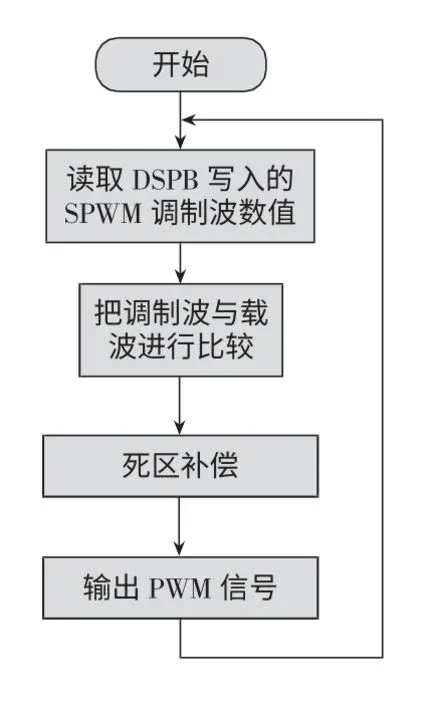

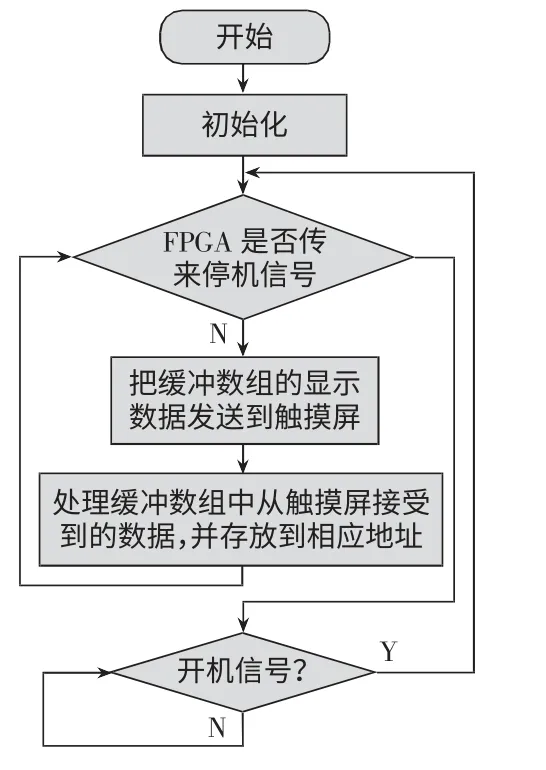

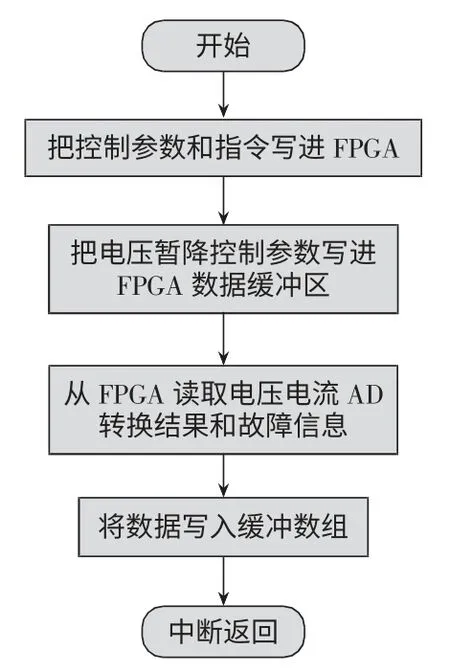

另外,FPGA還為兩個DSP進行數據交互提供數據緩沖區,進行故障檢測邏輯判斷、PWM信號輸出和普通IO輸出控制。圖13~圖16為FPGA的程序設計流程圖。

圖13 FPGA的系統時鐘脈沖序列產生模塊

圖14 FPGA的故障檢測模塊

圖15 繼電器控制IO輸出模塊

圖16 PWM信號生成模塊

圖17 DSPA的主程序設計流程圖

圖18 DSPA的外部中斷程序

圖19 DSPB主程序流程圖

DSPA是進行人機交互的重要環節,來自觸摸屏控制指令和控制參數將經過DSPA寫進FPGA,從而控制系統的運行,同時,DSPA從FPGA讀取數據,在觸摸屏上顯示出來。DSPA的程序設計如圖17和圖18所示,DSPA與觸摸屏之間通過一個緩沖數組進行數據傳輸。

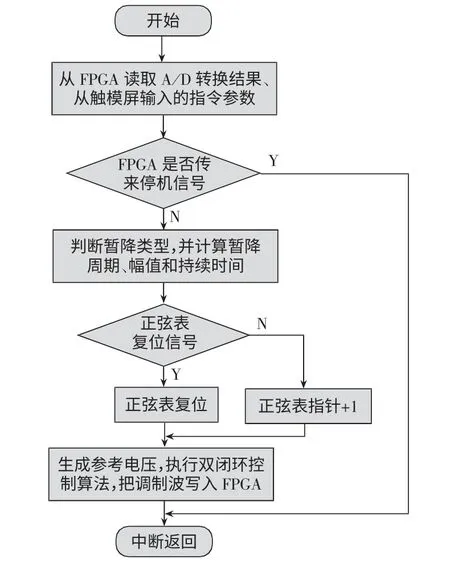

3.2.3 DSPB程序設計

DSPB是電壓控制算法的核心執行器件,主要負責輸出電壓波形的精確控制,控制算法采用電壓外環電流內環的雙閉環控制算法。圖19和圖20為DSPB的程序設計流程圖。

圖20 DSPB的外部中斷程序設計流程圖

4 實驗結果

按照上文的設計,本文搭建了電壓暫降儀整體實物圖進行測試,如圖21所示。實驗樣機為三相三線制,只能輸出線電壓,具體參數見表1。其控制器采用正弦脈寬調制(SPWM)控制方法,其中載波頻率為12.8kHz。實現了暫降(暫升)起始相位、持續時間、幅度均可調的電壓波形輸出。

圖21 電壓暫降儀整體實物圖

表1 電壓暫降儀具體參數

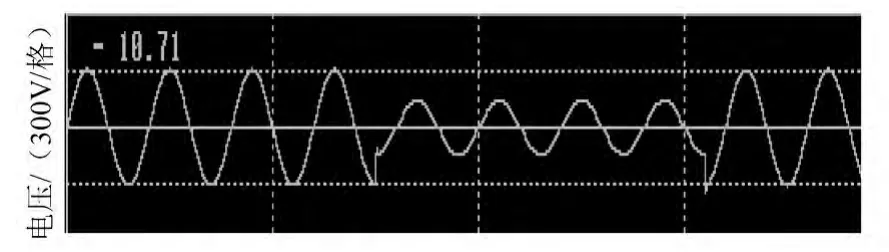

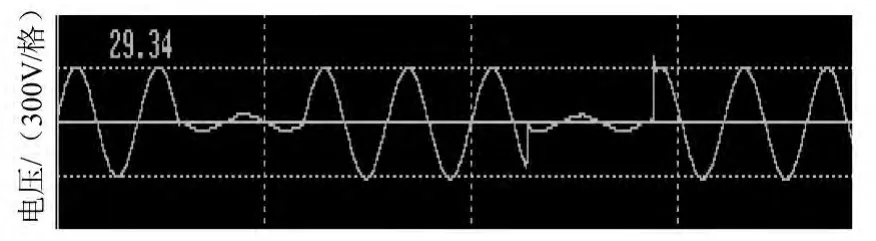

經日置HONKI3196測試,本文設計的電壓暫降儀能夠產生精度較高的有不同幅值、持續時間及相位的電壓暫降信號,可滿足各種相關的實驗需求。

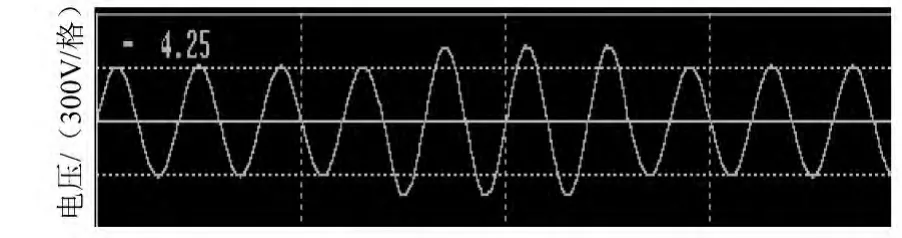

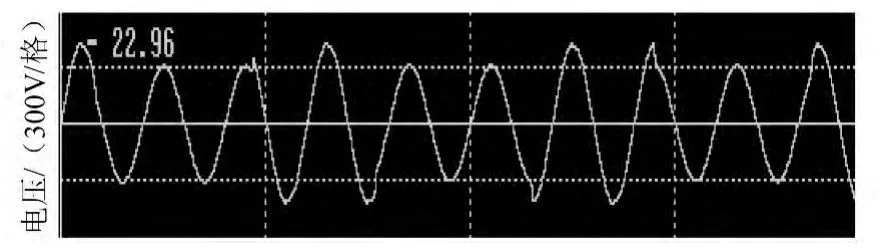

圖22~圖25為日置HONKI3196測得的電壓暫降波形示例圖,其中圖22為4周波的電壓暫降與恢復波形,暫降幅度為48%,暫降起始相位為270°。圖23為連續2次1.5周波的電壓暫降與恢復波形,暫降幅度為88%。圖24為3周波的電壓暫升與恢復波形,暫升幅度為38%。圖25為連續3次1.5周波的電壓暫升與恢復波形,暫升幅度為38%。

圖22 暫降波形1

圖23 暫降波形2

圖24 暫降波形3

圖25 暫降波形4

5 結束語

本文設計了基于雙DSP和FPGA控制器的電壓暫降儀。FPGA負責全系統脈沖信號的輸出、故障檢測和處理、PWM信號的輸出、IO控制的輸出并作為兩個DSP數據交互的平臺,其中一個DSP負責觸摸屏的數據顯示及指令讀入,另一個DSP負責對輸出電壓進行電壓外環電流內環雙閉環精確控制。該設計結合各處理器的功能特點,充分發揮其功能優勢,使整個控制系統效率得到了進一步提高。測試結果表明,該電壓暫降儀能夠產生理想的電壓暫降信號,控制器運行效率高、實時性強、控制精度高。

[1]肖湘寧,徐永海.電能質量問題剖析[J].電網技術,2001,25(3):66-69.

[2]林海雪.現代電能質量的基本問題[J].電網技術,2001,25(10):5-12.

[3]汪 穎,肖先勇,楊 達.敏感設備電壓暫降失效事件不確定性的最大混合熵評估[J].電網技術,2012,36(11):159-164.

[4]肖先勇,馬 超,楊洪耕,李華強.用電壓暫降嚴重程度和最大熵評估負荷電壓暫降敏感度[J].中國電機工程學報,2009,29(31):115-121.

[5]袁 媛,吳丹岳,林 焱,等.電壓暫降評估體系研究[J].電網技術,2010,34(6):128-133.

[6]張 威,鄭常寶,王 萍,等.基于自耦調壓器的電壓暫降發生器研究[J].電力電子技術,2011,45(3):88-90.

[7]陳增祿,姚偉鵬,毛惠豐,宋 健.一種電壓暫變發生器研究[J].電力電子技術,2007,41(3):97-99.

[8]陳文波.電壓暫降發生儀[P].中國專利:201120295494.2[P],2012-04-25.

[9]顏湘武,張 波,王樹岐,等.三相電壓暫降發生器[P].中國專利:201010188565.9[P],2010-11-17.

[10]趙劍鋒,王 潯,潘詩鋒.基于雙脈寬調制變換器和電壓滯環控制的電能質量信號發生裝置[J].電網技術,2005,29(4):41-43.

[11]趙劍鋒,王 浮,潘詩鋒.大功率電能質量信號發生裝置設計及實驗研究[J].電力系統自動化,2005,29(20):71-75.

[12]張香真,張建成.一種電能質量干擾發生器的研究及仿真[J].供用電,2004,21(1):27-29.