一種基于FPGA的視頻幾何校正系統設計方案

張 浩,凌朝東*,陳 虎,黃 信,楊 驍,湯 煒,閆 錚

(1.華僑大學 信息科學與工程學院,福建 廈門 361021;2.廈門市專用集成電路系統重點實驗室,福建 廈門 361008)

?

一種基于FPGA的視頻幾何校正系統設計方案

張 浩1,2,凌朝東1,2*,陳 虎1,2,黃 信1,2,楊 驍1,2,湯 煒1,閆 錚1

(1.華僑大學 信息科學與工程學院,福建 廈門 361021;

2.廈門市專用集成電路系統重點實驗室,福建 廈門 361008)

為了滿足大視場相關應用、尤其是大屏幕投影拼接技術應用領域對視頻圖像實時幾何校正的要求,本文對視頻圖像的實時幾何校正及其FPGA實現方法進行研究。首先,根據圖像幾何校正理論基礎,利用Matlab等工具進行算法模擬仿真,確定了視頻圖像實時幾何校正系統的基本框架。然后,根據現有的硬件平臺DE2的硬件資源情況,細致規劃系統結構,并對其中的核心部分幾何校正模塊進行仿真。最后,通過實際校正測試,斷定實驗結果達到視頻圖像實時幾何校正的預期效果。實驗結果表明:幾何校正后,投影儀投射出的圖像符合仿真結果,系統延時小于10個時鐘周期,遠小于毫秒級,且延時恒定,校正誤差不超過1個像素。此方案達到了預期視頻圖像實時幾何校正的效果,具有相當的借鑒、參考意義。

大視場;投影拼接技術;幾何校正;FPGA

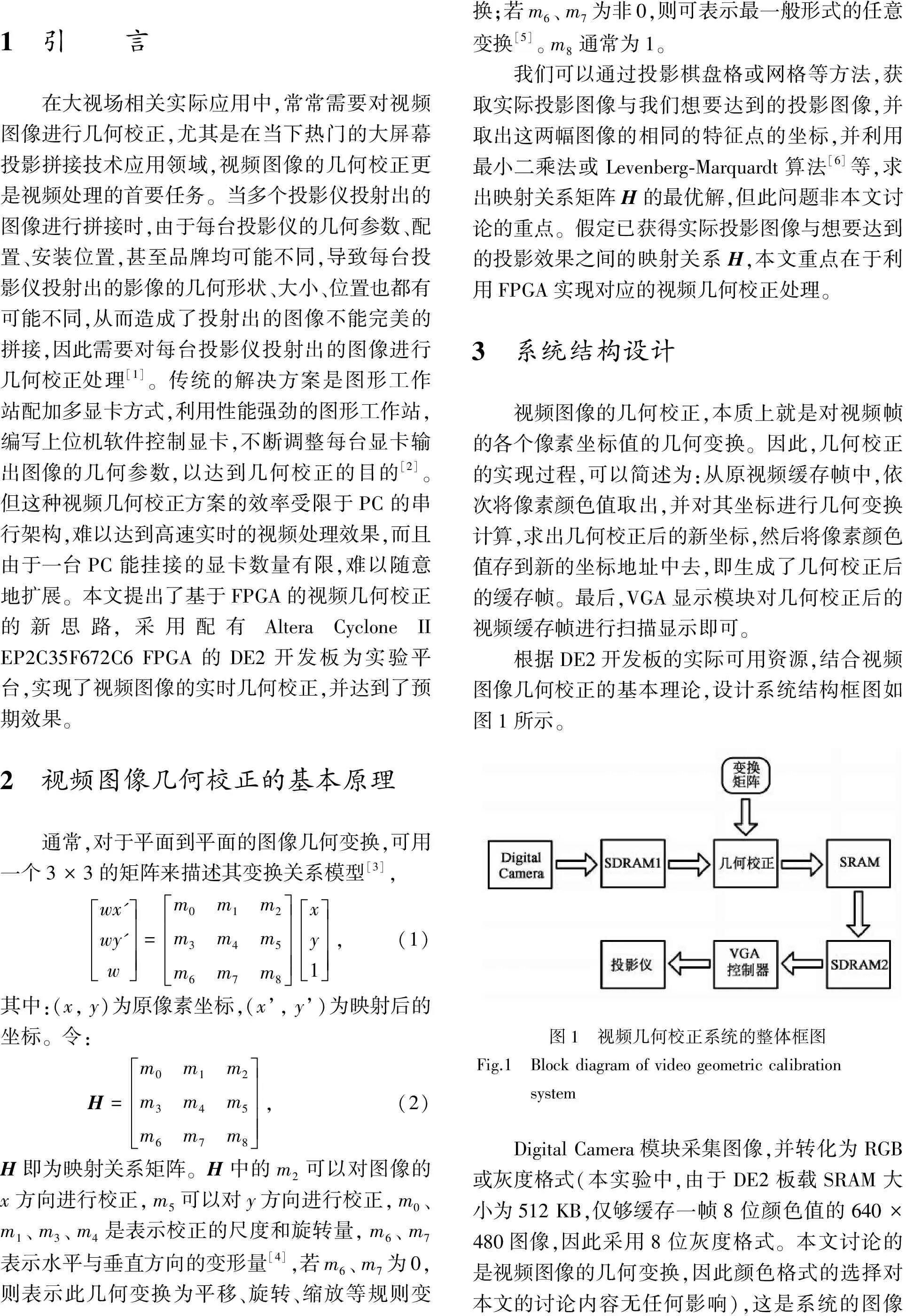

1 引 言 在大視場相關實際應用中,常常需要對視頻圖像進行幾何校正,尤其是在當下熱門的大屏幕投影拼接技術應用領域,視頻圖像的幾何校正更是視頻處理的首要任務。當多個投影儀投射出的圖像進行拼接時,由于每臺投影儀的幾何參數、配置、安裝位置,甚至品牌均可能不同,導致每臺投影儀投射出的影像的幾何形狀、大小、位置也都有可能不同,從而造成了投射出的圖像不能完美的拼接,因此需要對每臺投影儀投射出的圖像進行幾何校正處理[1]。傳統的解決方案是圖形工作站配加多顯卡方式,利用性能強勁的圖形工作站,編寫上位機軟件控制顯卡,不斷調整每臺顯卡輸出圖像的幾何參數,以達到幾何校正的目的[2]。但這種視頻幾何校正方案的效率受限于PC的串行架構,難以達到高速實時的視頻處理效果,而且由于一臺PC能掛接的顯卡數量有限,難以隨意地擴展。本文提出了基于FPGA的視頻幾何校正的新思路,采用配有AlteraCycloneIIEP2C35F672C6FPGA的DE2開發板為實驗平臺,實現了視頻圖像的實時幾何校正,并達到了預期效果。2 視頻圖像幾何校正的基本原理通常,對于平面到平面的圖像幾何變換,可用一個3×3的矩陣來描述其變換關系模型[3], wx'wy'wé?êêêêù?úúúú=m0m1m2m3m4m5m6m7m8é?êêêêù?úúúúxy1é?êêêêù?úúúú,(1)其中:(x,y)為原像素坐標,(x’,y’)為映射后的坐標。令: H=m0m1m2m3m4m5m6m7m8é?êêêêù?úúúú,(2)H即為映射關系矩陣。H中的m2可以對圖像的x方向進行校正,m5可以對y方向進行校正,m0、m1、m3、m4是表示校正的尺度和旋轉量,m6、m7表示水平與垂直方向的變形量[4],若m6、m7為0,則表示此幾何變換為平移、旋轉、縮放等規則變換;若m6、m7為非0,則可表示最一般形式的任意變換[5]。m8通常為1。我們可以通過投影棋盤格或網格等方法,獲取實際投影圖像與我們想要達到的投影圖像,并取出這兩幅圖像的相同的特征點的坐標,并利用最小二乘法或Levenberg?Marquardt算法[6]等,求出映射關系矩陣H的最優解,但此問題非本文討論的重點。假定已獲得實際投影圖像與想要達到的投影效果之間的映射關系H,本文重點在于利用FPGA實現對應的視頻幾何校正處理。3 系統結構設計視頻圖像的幾何校正,本質上就是對視頻幀的各個像素坐標值的幾何變換。因此,幾何校正的實現過程,可以簡述為:從原視頻緩存幀中,依次將像素顏色值取出,并對其坐標進行幾何變換計算,求出幾何校正后的新坐標,然后將像素顏色值存到新的坐標地址中去,即生成了幾何校正后的緩存幀。最后,VGA顯示模塊對幾何校正后的視頻緩存幀進行掃描顯示即可。根據DE2開發板的實際可用資源,結合視頻圖像幾何校正的基本理論,設計系統結構框圖如圖1所示。圖1 視頻幾何校正系統的整體框圖Fig.1 BlockdiagramofvideogeometriccalibrationsystemDigitalCamera模塊采集圖像,并轉化為RGB或灰度格式(本實驗中,由于DE2板載SRAM大小為512KB,僅夠緩存一幀8位顏色值的640×480圖像,因此采用8位灰度格式。本文討論的是視頻圖像的幾何變換,因此顏色格式的選擇對本文的討論內容無任何影響),這是系統的圖像

圖3 矩陣運算器模塊原理圖

Fig.3 Schematic diagram of matrix operation module

4.3 矩陣運算器模塊的波形仿真

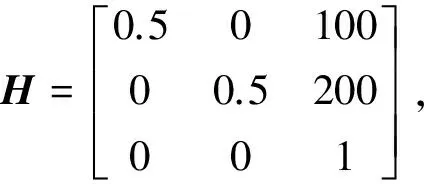

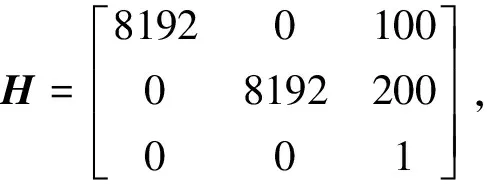

我們設定要將視頻圖像在x方向縮小2倍,并向右平移100個像素;在y方向也縮小2倍,并向下平移200個像素;視頻圖像形狀不變。易知,映射矩陣應為:

按照表1的輸入參數格式,將H變化為:

將此參數輸入仿真文件,得到仿真結果如圖4所示。由圖4以及設定的仿真條件可知,圖4中坐標(500,400)對應的輸出坐標為(350,400),(600,10)對應的輸出坐標為(400,205),其他依次類推,均符合預期的校正結果。由圖4還可知,矩陣運算模塊造成的時鐘延時約為7個時鐘周期。由于本設計系統中,所有模塊的同步時鐘均采用VGA的像素時鐘,即攝像頭將圖像幀數據存入SDRAM1時,幾何校正模塊也在同時工作,將SDRAM1的數據取出進行幾何校正,且校正速度與VGA掃描速度一致,因此整個系統的視頻幾何校正部分的延時就是這7個時鐘周期。已知分辨率640×480的視頻的像素時鐘頻率約為25 MHz[9],則7個時鐘周期的延時時間小于1 μs,遠小于毫秒級。而對常見的60幀/s的視頻,每幀時間約為1/60 s,可見本系統的視頻幾何校正部分的延時遠小于視頻每幀的顯示時間,因此不會對人的視覺觀感產生任何影響。

圖4 矩陣運算器模塊波形仿真圖Fig.4 Waveform of matrix operation module simulation

5 實驗結果與分析

5.1 視頻幾何校正結果分析

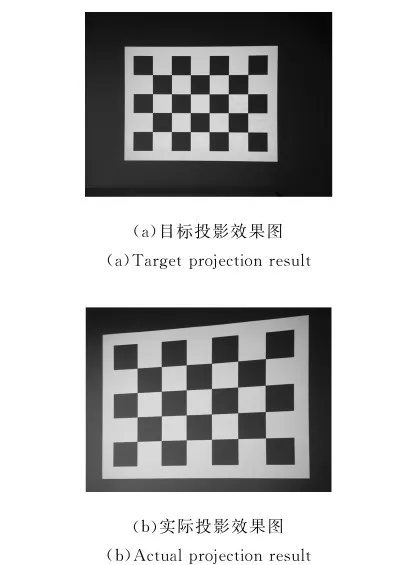

實驗分兩步進行。第一步為:首先,投影儀正對幕布,投射出完美的特征影像并拍照記錄,作為幾何校正目標投影影像。然后,將投影儀擺放任意角度,投射出不完美的不規則形狀的特征影像,保持投影儀位置固定并拍照,獲得目前實際投影影像。最后,利用Matlab等工具獲取實際影像到目標影像的映射關系矩陣H。第二步為:將第一步獲得的映射關系矩陣H輸入到FPGA中,FPGA將依據H對攝像頭采集的視頻進行幾何校正,并經由第一步中固定位置的投影儀投射到幕布上,對比目標影像,觀察是否達到預期效果。實驗器材見表2,具體過程如下。

表2 實驗器材列表Tab.2 List of the experimental equipment

圖5 目標投影效果與未幾何校正投影效果對比圖Fig.5 Comparison of target projection result and non geometric calibration projection result

目標投影效果與未經幾何校正的實際投影效果對比如圖5所示。

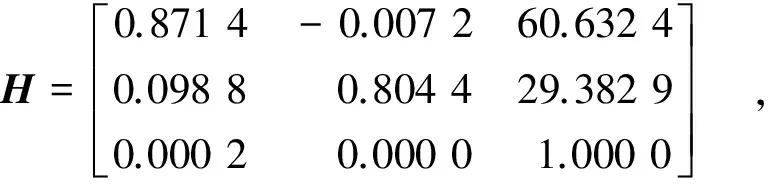

利用Matlab將目標投影效果圖與實際投影效果圖的特征點坐標進行提取,考慮相機失真因素,并用最小二乘法計算得到實際投影效果與目標投影效果的映射關系矩陣為[10]:

按照表1將H轉化為

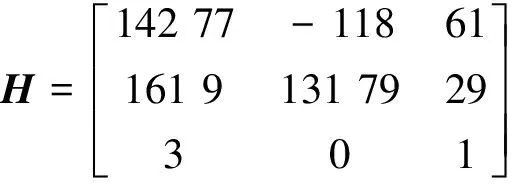

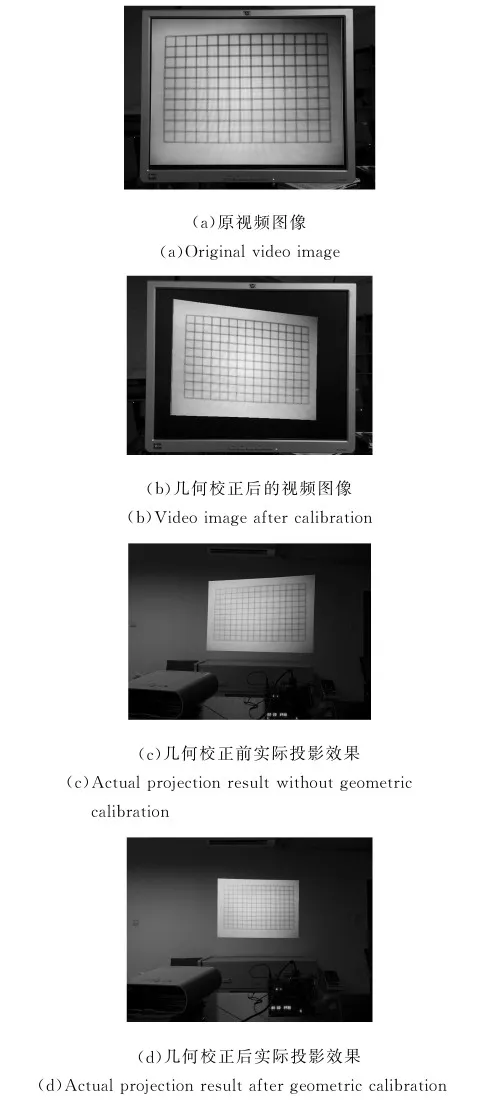

然后將H導入FPGA中,得到幾何校正結果如圖6所示。

圖6(a)是用液晶顯示器顯示的原始視頻圖像。將其直接用投影儀投射在屏幕上的顯示效果如圖6(c)。將6(a)進行映射關系矩陣為H的幾何校正之后,得到視頻圖像圖6(b),圖6(b)看似發生了不規則的變形,但將其通過投影儀投射到屏幕上時,實際投影效果如圖6(d),將圖6(d)與目標投影效果圖5(a)對比發現,投射出的影像的幾何失真得到校正,可判定實驗達到了預期的視頻幾何校正效果,從而肯定了本方案的正確性與可行性。理論上,根據Hx的不同,本設計可以對視頻圖像做任何形狀的幾何校正。

而針對多投影系統的視頻圖像幾何校正,實現方法與本實驗相同:只需先設定一個多投影拼接后的目標效果圖,然后將此圖中每臺投影儀各自分工的部分,與對應投影儀的實際投影效果進行比對分

圖6 幾何校正結果對比圖Fig.6 Comparison of geometric calibration results

析,獲得映射關系矩陣Hx(每臺投影儀對應的映射關系矩陣可能是不同的)。再根據Hx對每臺投影儀的視頻輸入源做不同參數的幾何校正即可。

5.2 幾何校正精度分析

對于本文所述的視頻圖像幾何校正方案,誤差來源主要有兩點:一是Hx的參數誤差,主要包括相機魚眼效應引起的誤差、Hx參數求解時迭代計算次數有限所引起的誤差、解出的參數由于四舍五入引起的誤差等,這部分誤差是由儀器設備、上位機算法等共同造成,非本文討論重點。二是本設計方案的系統誤差,在本設計中,由于iX、iY、oX、oY均為小于103的整數,而Hx均保留到小數點后4位,根據式(5)、式(6)可知坐標變換過程中FPGA進行相關矩陣運算的誤差最大不超過1個像素點,不會對顯示效果產生任何影響。若資源足夠,增加Hx的小數保留位數,則幾何校正的精度將更高。

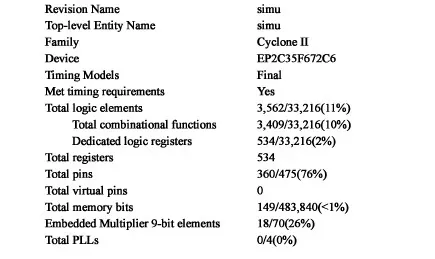

5.3 資源使用情況分析

實際資源占用情況如圖7所示。

圖7 FPGA的資源占用情況Fig.7 Use of FPGA resources

由圖7可知,對于DE2開發平臺板載的EP2C-35F672C6 FPGA,經Quartus II綜合后本方案幾何校正部分各項硬件資源占用率均不超過30%,可見本方案具有資源占用率少、效率高的優勢,因此適合工程應用。

6 結 論

本文依據大視場應用、尤其是大屏幕投影拼接技術領域對視頻圖像幾何校正快速、穩定、適宜推廣的需求,設計了一套基于FPGA的視頻圖像幾何校正方案。本文首先介紹了視頻圖像幾何校正的基本理論。然后據此設計了幾何校正的系統結構。之后根據DE2開發平臺的實際資源,詳細設計了幾何校正模塊的具體結構并進行了仿真。最后,通過觀察實際的投影校正效果,驗證了本方案的可行性。實驗結果證明:本方案系統延時小于10個時鐘周期,遠遠不到毫秒級,且延時恒定不變,幾何校正誤差最大不超過1個像素,對人的視覺觀感不會有任何影響。而且本方案資源占用率低,適合大范圍應用。雖然由于DE2平臺資源所限,未能進行更高分辨率的視頻幾何校正測試,但本方案的設計思想仍然具有相當的借鑒、參考意義。

[1] 王勝正, 楊杰. 自動多投影儀非線性幾何校正與圖像邊緣融合方法[J]. 上海交通大學學報, 2008, 42(4): 574-578. Wang S Z, Yang J. Auto-nonlinear geometry calibration and edge blending of multi-projector display system [J].JournalofShanghaiJiaotongUniversity, 2008, 42(4): 574-578. (in Chinese)

[2] 李斌. 低成本多投影儀拼接方法研究[D]. 濟南:山東大學,2005. Li B. Study on Low-cost multi-projector mosaic [D]. Jinan: Shandong University, 2005. (in Chinese)

[3] 張德豐. MATLAB數字圖像處理[M]. 北京:機械工業出版社,2009. Zhang D F.DigitalImageProcessingwithMATLAB[M]. Beijing: China Machine Press, 2009. (in Chinese)

[4] 張錚,王艷平,薛桂香. 數字圖像處理與機器視覺[M]. 北京:人民郵電出版社,2010. Zhang Z, Wang Y P, Xue G X.DigitalImageProcessingandMachineVision[M]. Beijing: Ports & Telecom Press, 2010. (in Chinese)

[5] 陶婷婷,張亞萍. 多投影顯示系統的幾何校正及邊緣融合技術研究與實現[J]. 云南師范大學學報,2014,34(1): 54-60. Tao T T, Zhang Y P. Research andrealization of geometric calibration and edge blending for multi-projector display system [J].JournalofYunnanNormalUniversity, 2014, 34(1): 54-60. (in Chinese)

[6] 劉淑. 多通道大屏幕圖像無縫拼接技術研究[D]. 北京:北京交通大學,2011. Liu S. Theresearch on multi-projectors large format mosaic [D]. Beijing: Beijing Jiaotong University, 2011. (in Chinese)

[7] Integrated Silicon Solution, Inc. IS61LV25616_Datasheet.pdf [OL]. www.issi.com, 2001.

[8] 葉茂. 多屏投影顯示系統的自動校正技術[D]. 成都:四川大學,計算機應用,2006. YE M. Automaticcalibration techniques for multi-projector display systems [D]. Chengdu: Sichuan University, 2006. (in Chinese)

[9] Video Electronics Standards Association. VESA and industry standards and guidelines for computer display monitor timing (DMT) [EB]. 2004.

[10] 蔡山,張浩,陳洪輝,等. 基于最小二乘法的分段三次曲線擬合方法研究[J]. 科學技術與工程,2007, 7(3): 352-355. Cai S, Zhang H, Chen H H,etal. Research of piecewise cubic-fitting method based on least-square principle [J].ScienceTechnologyandEngineering, 2007, 7(3): 352-355. (in Chinese)

Design of video geometric calibration system based on FPGA

ZHANG Hao1,2, LING Chao-dong1,2*, CHEN Hu1,2, HUANG Xin1,2, YANG Xiao1,2, TANG Wei1, YAN Zheng1

(1.InstituteofInformationScienceandEngineering,HuaQiaoUniversity,Xiamen361021,China;2.KeyLaboratoryofASICandSystemofXiamen,Xiamen361008,China)

In order to realize the real-time video image geometric calibration in large field of view image applications, especially in large format projection mosaic technique field, this paper analyzes the video image geometric calibration and its realization based on FPGA. First, according to the basic theory of image geometric calibration, this paper describes the simulation of algorithms with Matlab and other tools, and designs the basic frame of the video image geometric calibration system. Then, the system structure is detailed designed based on the hardware resources of DE2 platform and the geometric calibration module is simulated. Finally, based on the actual calibration test, this paper concludes that the experimental results achieve the desired target of real-time video image geometric calibration. Experimental results show that the image which has been calibrated and projected by projector is consistent with the simulation results. The delay of system is less than 10 clock cycles, far less than millisecond level, and the value of delay time is a constant. The inaccuracy of the calibration system is no more than one pixel. This design achieves the desired target of real-time video geometric calibration, which has considerable significance for reference.

large field of view; projection mosaic technique; geometric calibration; FPGA

張 飆(1969-),男,四川人,碩士,主要從事LED顯示技術、激光雷達技術的研究。E-mail:75990383@qq.com 周國清(1965-),男,江西人,博士,教授,博士生導師,主要從事遙感技術的研究。E-mail:glitezhou@yahoo.com

2014-10-14;

2014-11-06.

國家自然科學基金(No.61203369,No.61204122); 福建省自然科學基金(No.2011J01351); 福建省科技計劃重點項目(No.2013H0029) ;泉州市科技計劃項目(No.2013Z33)

1007-2780(2015)03-0459-08

TN911.73

A

10.3788/YJYXS20153003.0459

*通信聯系人,E-mail:edac@hqu.edu.cn