基于FPGA的多處理器片上系統運行時軟硬件重構

葉林鋒,謝國波,曾碧

(廣東工業大學計算機學院,廣州 510006)

基于FPGA的多處理器片上系統運行時軟硬件重構

葉林鋒,謝國波,曾碧

(廣東工業大學計算機學院,廣州 510006)

可重構系統可以根據應用程序運行時的需要動態地選擇不同配置硬件加速方案。動態可重構多處理器片上系統是一種面向多種應用/標準之間資源共享、減少能源損耗和提升系統性能(專用DSP或者定制協處理器)的有效方法。提出一種根據應用不同需求進行動態軟硬件重構的方法。

動態部分可重構;離線可重構;可重構計算;智能計算;按需計算

0 引言

隨著半導體工藝和計算機技術的不斷發展,嵌入式計算機系統滲透到越來越多的應用領域。同時,嵌入式系統的多樣性又阻礙了它在標準化和集成化方面的發展,人們希望可以將這些經過不同應用“剪裁”的嵌入式系統整合成“大而專”的嵌入式系統。日益增加的半導體數量和不斷改進的計算機系統結構雖然使得嵌入式系統擁有了前所未有的數據處理能力和吞吐能力,但面對數不勝數并且不斷變化的應用需求,傳統硬件無論是在定制化還是通用化的道路上都處于相對落后的位置。近年來,為了追趕市場的步伐,越來越多的嵌入式系統采用通用處理器+專用處理模塊的架構(例如:GPP+GPU,GPP+DSP,GPP+協處理器等)。這樣就不用為每個產品重新設計整套方案,提高了設計的可重用性,也縮減了產品的研發周期。然而,這些額外的固定加速模塊會在一定程度上增加系統的芯片利用率、面積和功耗,尤其是當系統中有多個加速模塊的時候,能效比就會變得很低。

動態可重構多處理器片上系統(Dynamic Reconfigurable MPSoC)是一種由多個混雜處理器和可重構硬件模塊組成的片上系統架構,分為固定部分和可變部分。固定部分主要用于完成一些通用的計算處理、輸入輸出管理和任務調度等工作,而可變部分將根據所運行應用的不同需求進行硬件改造并完成關鍵計算任務。近十年來,有關R-MPSoC的研究很多,不少的研究結果都證明了可重構計算在性能方面的巨大潛力,但在這樣一些硬件可重構的平臺上開發軟件仍然是非常具有挑戰性的工作。本文主要就是在此問題的基礎上探討自適應MPSoC架構上的軟硬件自適應重構流程。

1 相關工作

動態局部重構(Dynamic Partial Reconfiguration)技術使得硬件可以在運行過程中實現局部邏輯功能的重構。但由于系統中硬件相關的軟件(Hardware-dependent Software)的存在,重構之后的硬件將需要重新加載相應的HdS軟件才能正常運行。本文主要探討在整個重構的過程中,HdS軟件與重構硬件如何實現無縫切換的方法。通過本文所提出動態重構流程,用戶可以通過設計不同的重構決策算法為不同的應用場景提供更為智能和高效的軟硬件管理方案。

Fahmy[1]提出了一種在FPGA上實現運行時自適應應用程序硬件重構的系統框架,它把控制運行和處理機制分離以及抽離掉系統設計者重新配置硬件的細節。在此框架下,系統模型和軟件結構體系被用來簡化基于FPGA的自適應應用程序設計。這與本文的工作非常類似,但是Fahmy[1]論文主要是研究具體的軟件架構,而本文側重于通用的軟硬件重構流程。實時重構嵌入式系統的整體方案(hArtes[2])是可重構平臺的設計流程,它包括三個階段:算法的探索和翻譯(AET)、設計空間探索(DSE)和系統綜合(SS)。AET用C語言發展或翻譯應用程序,DSE階段包含任務劃分,任務優化和分配給適合的硬件單元。SS階段實現嵌入式硬件/軟件協同設計和HDL生成及編譯執行。hArtes設計流程的實驗結果表明,生成的設計提供了3.8倍的全面應用加速。然而,這種設計流程只適用于編譯時可重構的系統,這是因為它使用了Molen[3]編譯器作為主程序編譯器。

Hthreads[4]是一個用來指定應用程序線程在計算機處理單元(CPU)/現場可編程門陣列(FPGA)并行運行的混合程序模型。Hthreads的處理方法是通過互斥鎖來調度決策和恢復執行線程。簡單接口可重構計算(SIRC)[5]工程提供了簡單、可移植和可擴展的開源通信和同步API。它允許C++代碼在主機上運行過程中,與基于Verilog的映射在FPGA的電路進行通信,并通過內在軟件接口和內在硬件接口進行軟硬件同步。Eustache[6]提出了一個統一的配置和通信接口(UCCI)的軟、硬件解決方案,當任務在處理器上運行時它通過軟件API調用來實現,當任務被映射到硬件加速單元時通過HDL代碼生成的硬件來實現。

Huang[7]提出了一種基于應用歷史記錄的在線算法,并充分考慮了各種重配置的開銷。這項研究工作采用了內存沖突模型和涉及關鍵接口與電路問題的預定義重構區域。在線算法計算出的“總收益”是決定是否將新方案加載到FPGA協處理器的主要依據。這項研究工作提出了運行前重構方案,這是因為重新配置的決策是在應用程序執行前作出的。對于數據相關的應用程序來說,程序運行過程中的數據變化會導致系統性能瓶頸的轉移,所以此類應用需要在程序運行過程中通過算法發現和調整軟硬件方案。

由于大部分消費電子類產品都需要考慮產品上市時間,而這些產品很強調人機交互和產品體驗,因此對于這些產品研發而言,他們除了關注系統性能外,更關注產品開發人員能否快速地在基礎平臺上開發應用。相對于傳統的應用開發,基于可重構系統的應用開發需要軟硬件的協同設計,如果可以將軟硬件的關聯隱藏起來,使得軟件設計人員不需要考慮硬件的因素,將能大大簡化可重構應用程序的開發流程和復雜度。本文主要從嵌入式消費類電子產品的設計開發角度,探索可重構系統[8~9]的運行時軟硬件重構方法和流程。為了證明使本文所提方法的可行性,在FPGA上演示了多處理器片上系統的運行時軟硬件重構應用程序。

2 運行時軟硬件重構流程

運行時重構的主要目的是在應用程序運行過程中能修改程序或硬件配置而無需停止或重新啟動。本文方法適用于可以被分解為一系列具有軟件和硬件功能序列的應用程序,目標是為基于標準化接口的嵌入式系統應用,并根據不同的應用需求動態適應硬件資源進行優化架構的應用程序在R-MPSoC的開發。以下是本文使用到的相關術語:

●XManager:一個通用處理器(GPP),主要負責整個可重構多處理器系統的資源管理、任務調度、軟硬件重構和輸入/輸出。

●XWorker:一個具有可定制化指令的處理器,主要用于執行指定的計算任務。

●數據流:需要處理或者移動的數據集合。

●指令流:需要處理或者移動的指令序列。

●配置流:硬件配置所需要的二進制數據(例如:FPGA的bitstream)。

本文采用了與指定代理[10]和BORPH[11]中ghost處理器相當的方法實現軟硬件的動態重構管理。XManager負責給系統中的每個XWorker指派計算任務并在所需要的時候采集它們的計算結果,XWorker一般會被指派完成圖像處理、加密處理、音頻處理或者視頻處理等計算密集型任務。運行Linux系統的XManager是整個多處理器系統的唯一管理者,圖1是XManager進行軟硬件動態重構的完整流程。

R-MPSoC系統上電后自動地從非易失存儲器(如Flash)加載基于當前FPGA芯片的硬件方案(配置),然后分別為XManager加載操作系統和為XWorker加載啟動程序。XManager啟動含有重構算法的任務管理進程。如果沒有特定配置請求或新的重構決策,XManager就如一般的單處理器一樣執行應用任務。根據系統和配置存儲來計算分配的資源計算出更合適的配置策略后,XManager任務管理進程將做出一個重構系統的決定。XManager根據決定將新的硬件配置文件加載到系統主存中。XManager收到“READY”信號后先執行FPGA的硬件重構,然后從本地存儲器尋找和任務匹配的軟件程序并給XWorker發送復位信號來執行軟件安裝。安裝完畢后重新啟動XWorker。當XWorker準備就緒后,應用程序就可以在不同處理器和協處理器上運行。

在圖1的動態重構流程中,Mx代表在XManager上的執行步驟,Wx代表在XWorker上的執行步驟,Dx代表局部重構的執行步驟。本文的方法中,所有的局部重構步驟都由XManager執行。

以下是XManager上的執行步驟:

a)XManager從Flash等非易失性存儲設備中加載啟動文件;(M0)

b)根據啟動文件中的硬件部分對FPGA進行配置和初始化;(M1)

c)根據啟動文件中的軟件部分進行軟件環境安裝和設置,本例中將啟動petalinux操作系統;(M2)

d)XManager自動加載動態重構管理進程;(M3)

e)動態重構管理進程采用特定的算法(本文后半部分將介紹算法的例子)輸出重構決定,如果需要重構就跳轉到j,否則繼續到f;(M4)

f)XManager加載通過函數調用或者線程加載新的指令序列;(M5)

g)XManager根據指定的輸入和輸出參數完成計算任務;(M6)

h)XManager完成了所有本地執行的計算任務后,查詢XWorker的任務完成情況,如果XWorker狀態標志位DONE為1,則表示指派給XWorker的任務已經完成,否則等待;(M7)

i)XManager檢查是否任務已經完成,如果完成就跳轉到z結束此次的應用程序,否則就跳轉d繼續循環執行;(M8)

j)XManager檢查硬件加速函數表中是否已經有合適的硬件解決方案;(D0)

k)如果硬件沒有準備好就跳轉到l步驟開始重構,否則就將ENABLE標志位置1,并跳轉到f步驟繼續執行;(D1)

l)XManager從緩存、Flash和服務器等不同的存儲層次加載新的軟硬件配置文件;(D2)

m)XManager將ENABLE標志位置0,確保XWorker在重構流程結束前不會被指派新的任務;(D3)

n)XManager等待XWorker將當前的任務完成,只有XWorker為就緒狀態(DONE=1時)才能繼續下一步操作;(D4)

o)XManager對可重構區域進行硬件的局部重構;(D5)

p)重構完成后,XManager將相應的軟件執行代碼加載到指定位置;(D6)

q)XManager更新系統的硬件加速函數表,并跳轉到d步驟繼續執行;(D7)

r)程序結束。

以下是XWorker上的執行步驟:

s)XWorker從Flash等非易失性存儲設備中加載啟動文件;(W0)

t)查詢ENABLE,如果為1則跳轉到u步驟繼續執行,否則跳轉到u步驟執行;(W1)

u)XWorker從默認的地址加載任務信息,包括輸入輸出參數和地址,所執行的二進制代碼位置等;(W2)

v)XWorker開始執行計算任務并將結果輸出到指定的地址空間;(W3)

w)XWorker將狀態改為就緒(DONE=1),等待新任務或者下一個數據塊的到來;(W4)

3 動態重構決策算法

在本文所提出的運行時軟硬件重構流程中,XManager通過對系統軟硬件的資源情況和預期性能增益來決定是否進行重構。這個決策過程通常由監控、決策和重構三個環節組成。監控環節是指XManager通過對系統中所有的計算任務完成情況和時間進行記錄,決策環節是指XManager每隔一定時間就啟動決策算法計算當前系統瓶頸并尋找更優的軟硬件配置方案,重構環節中XManager將對系統進行軟硬件重構。

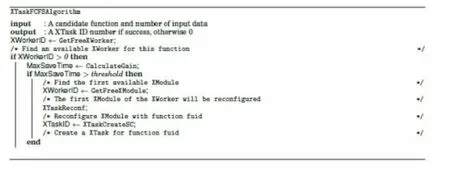

圖1 離線重構流程圖

在實際的多處理器可重構系統中,硬件的更換所引發軟硬件進程(或者說任務)的動態切換將產生額外的系統負載和延遲,如何在多個約束條件下最優化利用有限的物理邏輯資源是一個典型的多維背包問題,因此很難在多項式時間內獲得最優解。本文采用的”先到先得”算法,由于不需要考慮替換策略,只按照任務的先后次序分配硬件資源,所以大大降低了重構決策的復雜度,可以在極短的時間內做出相對優化的重構決定。

先到先得算法(FCFS:First-Come-First-Served)的輸入是硬件加速函數表(指針)和待處理數據量(無符號整數),算法的詳細過程如圖2所示。XManager通過GetFreeXWorker函數獲取系統中空閑XWorker的ID號,如果該ID號有效,則通過CalculateGain評估其加速的最大增益,如果這個增益大于系統指定的閾值(本文中的閾值是一個設定的常量,一般來說與器件進行重構的時間相關),則找出該XWorker中的可重構模塊ID并調用動態軟硬件重構函數,最后使用XTaskCreateSC創建該硬件配置的計算任務。本算法的核心思想是,只考慮空閑的XWorker和XModule的重構方案,如果沒有空閑資源,就不考慮軟硬件的重構。

圖2 先到先得算法

4 實驗結果

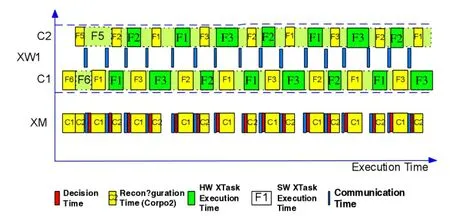

為了演示本文所描述的運行時重構流程,在XPSoC-M0W2架構編譯運行了Crypto-PGM應用。在這個演示中,采用的運行時重構決策算法是先到先得算法。這個算法只考慮了當前狀態下所需要的決策和重構時間,因此這很容易實現,并且可以取得顯而易見的性能優化。

本次實驗中,XManager用XTasks和XFunc-API生成并指派計算任務XTasks給XWorker。XWorker首先在沒有任何硬件加速的情況下執行這些XTasks。在XWorker執行XTasks期間,XManager將阻塞直至XTasks完成后,才去讀取需要的結果。這種嘗試主要為了方便獲得線性的執行時間,并因此計算出由于XTask通信、決策和軟硬件重構所產生的額外花銷。本例中的加密算法是數據相關的,因此每個計算任務處理時間與數據相關。

圖3是基于先到先得算法進行運行時重構的運行情況,本例的幾組特征描述如下:

●XPSoC-M0S2體系結構模型

●阻塞型XTask

●指令粒度:XFunction

●數據粒度:修復粒度

●決策算法:先到先進行

●基于文件解決方案:F5+F6

●重構粒度:最多兩個協處理器

●重構頻率(Fr):每次迭代一次

圖3 基于先到先得算法的運行時重構

●觀測和決策人物頻率(F):每XTask一次

5 結語

本文提出了基于FPGA的軟硬件運行時重構流程和決策算法,通過任務觀察、增益決策和重新配置三個環節實現應用程序運行過程中的動態軟硬件重構,筆者也提出因軟硬件重構所帶來的額外花銷,尤其是決策、通信和重構等帶來的延時問題不容忽視。最后通過一個圖像加密應用演示了完整的運行時軟硬件重構流程。但筆者也意識到,由于現有算法暫無考慮硬件的替換,存在著一定的局限性。在以后的研究中,將繼續深入研究動態重構算法的優化問題。

[1] S.Fahmy,J.Lotze,J.Noguera,L.Doyle,and R.Esser.Generic Software Framework for Adaptive Applications on FPGAs.Field Programmable Custom Computing Machines,2009.FCCM’09.17th IEEE Symposium on,pages 55~62,2009

[2] M.Rashid,F.Ferrandi,and K.Bertels.hArtes Design Flow for Heterogeneous Platforms.2009

[3] S.Vassiliadis,S.Wong,G.Gaydadjiev,K.Bertels,G.Kuzmanov,and E.Panainte.The MOLEN Polymorphic Processor.IEEE Transactions on Computers,pages 1~13,Sep 2004

[4] D.Andrews,R.Sass,E.Anderson,J.Agron,W.Peck,J.Stevens,F.Baijot,and E.Komp.Achieving Programming Model Abstractions for Recongurable Computing.Pages 1~11,Nov 2009

[5] K.Eguro.SIRC:An Extensible Recongurable Computing Communication API.Field-Programmable Custom Computing Machines(FC CM),2010 18th IEEE Annual International Symposium on,pages 135~138,2010

[6] Y.Eustache and J-Ph.Diguet.Reconguration Management in the Context of RTOS-Based HW/SW Embedded Systems.EURASIP Journal on Embedded Systems,2008:1~11,Jan 2008

[7] C.Huang and F.Vahid.Transmuting Coprocessors:Dynamic Loading of FPGA Coprocessors.Design Automation Conference,2009.DAC '09.46th ACM/IEEE,pages 848~851,2009

[8] J-Ph.Diguet,L.Ye,Y.Eustache,J.Crenne,P.Bomel,G.Gogniat,J.Vidal,and F.De Lamotte.Networked Self-Adaptive Systems:An Opportunity for Conguring in the Large.In ERSA'09,pages 81~90,2009

[9] L.Ye,J-Ph.Diguet,and G.Gogniat.Rapid Application Development on Multi-Processor Recongurable Systems.In FPL,Milano,Italy, 2010

[10] Y.Eustache and J-Ph.Diguet.Reconguration Management in the Context of RTOS-Based HW/SW Embedded Systems.EURASIP Journal on Embedded Systems,2008:1~11,Jan 2008

[11] H.So.Borph:An Operating System for FPGA-based Recongurable Computers.Citeseer,Jan 2007

Multiprocessor System on Chip Runtime Software and Hardware Reconfigurable Based on FPGA

YE Lin-feng,XIE Guo-bo,ZENG bi

(College of Computer,Guangdong University of Technology,Guangzhou 510006)

Determines precisely when the running application needs to be accelerated.The dynamic reconfigurable MPSoC is an interesting approach to optimize the sharing of resources between different applications/standards,minimize energy consumption and optimize system performance(DSP specific or coprocessor specific).Presents an adaptive method to perform on-the-fly HW/SW reconfiguration,according to application requirements to optimize performances.

Dynamically Partial Reconfiguration;Offline Reconfiguration;Reconfigurable Computing;Intelligent Computing;On-Demand Computing

1007-1423(2015)04-0053-06

10.3969/j.issn.1007-1423.2015.04.015

葉林鋒(1979-),男,廣東廣州人,博士研究生,講師研究方向為高性能計算、可重構計算和并行計算

謝國波(1977-),男,廣東人,博士研究生,教授,研究方向為網絡與分布式系統

2014-12-23

2015-01-25

廣東省自然科學基金(No.S2012040007326)、廣東省教育部產學研合作專項資金(No.2012B091100191)

曾碧(1963-),女,廣東人,博士研究生,教授,研究方向為嵌入式系統和智能技術