基于FPGA的Camera Link輸出編碼設(shè)計(jì)

劉 彪,王建立,呂耀文,2,曹景太

(1.中國科學(xué)院 長春光學(xué)精密機(jī)械與物理研究所,吉林 長春 130033;2.中國科學(xué)院大學(xué),北京 100049)

1 引 言

目前,數(shù)字?jǐn)z像機(jī)向著高分辨率、高幀頻的方向發(fā)展,帶來了數(shù)據(jù)傳輸速度的大幅度提升。Camera Link通過不同的配置方式可以適應(yīng)不同攝像機(jī)對(duì)于傳輸帶寬的要求,因此應(yīng)用極為廣泛[1-3]。Camera Link在傳輸物理層上采用低電壓差分信號(hào)(Low Voltage Differential Signal)電平標(biāo)準(zhǔn),有效防止了電磁干擾和信號(hào)線之間的交叉串?dāng)_(Cross Talk)[4]。同時(shí)它的數(shù)據(jù)線多路技術(shù),使線纜使用量大大縮減[5]。根據(jù)文獻(xiàn)[6],需要使用編解碼芯片實(shí)現(xiàn)Camera Link傳輸協(xié)議,文獻(xiàn)[7-8]使用DS90CR287將28路TTL信號(hào)轉(zhuǎn)換成4路LVDS信號(hào)。根據(jù)DS90CR287的功能可知,如果要實(shí)現(xiàn)FULL模式的編碼輸出則需要三塊DS90CR287芯片,這樣增加了電路板的走線、焊盤和管腳,不利于攝像機(jī)的集成化。現(xiàn)場可編程邏輯陣列(Field Programmable Gate Array)由于其靈活的可配置性能,在攝像機(jī)硬件電路設(shè)計(jì)和圖像采集卡中得到了廣泛的應(yīng)用[9-10]。從查閱的文獻(xiàn)來看,目前還沒有關(guān)于詳細(xì)介紹使用FPGA實(shí)現(xiàn)Camera Link輸出編碼的文獻(xiàn)。因此,本文在Camera Link協(xié)議的基礎(chǔ)上通過理解Camera Link輸出編碼芯片DS90CR287的編碼功能,選擇了Xilinx公司的Virtex4系列中XC4VLX15型號(hào)芯片作為核心芯片,采用VHDL硬件描述語言,在FPGA中實(shí)現(xiàn)了Camera Link協(xié)議的輸出編碼功能。在降低硬件成本的同時(shí),有效地節(jié)省了電路板的面積,有利于攝像機(jī)設(shè)計(jì)的集成化和小型化。

本文首先給出了采用FPGA實(shí)現(xiàn)Camera Link輸出編碼的具體方法;接著通過功能仿真和實(shí)物實(shí)驗(yàn)驗(yàn)證編碼的正確性;最后對(duì)全文進(jìn)行歸納和總結(jié)。

2 Camera Link輸出編碼實(shí)現(xiàn)

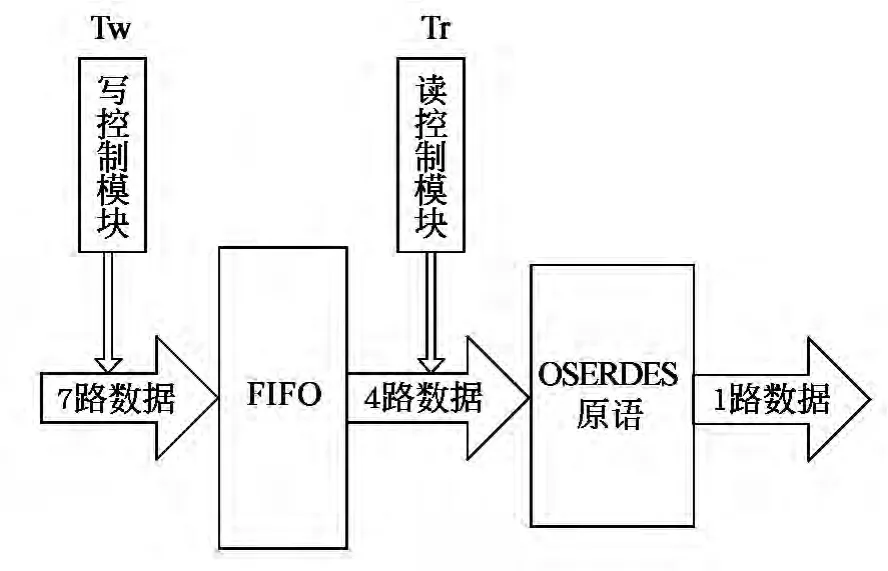

為了采用FPGA實(shí)現(xiàn)Camera Link輸出編碼的功能。本文將編碼過程分為3個(gè)步驟:(1)像素?cái)?shù)據(jù)信號(hào)映射成為Camera Link中抽象出來的PORT;(2)對(duì)數(shù)據(jù)信號(hào)和同步時(shí)鐘信號(hào)進(jìn)行Camera Link編碼;(3)并串轉(zhuǎn)換,將28路并行信號(hào)轉(zhuǎn)換成4路串行信號(hào)。圖1為Camera Link輸出編碼框圖。下面分別對(duì)這3個(gè)步驟做重點(diǎn)說明。

圖1 Camera Link輸出編碼框圖Fig.1 Diagram of Camera Link output encoding

2.1 像素?cái)?shù)據(jù)與 Camera LinkPORTA\B\C的映射

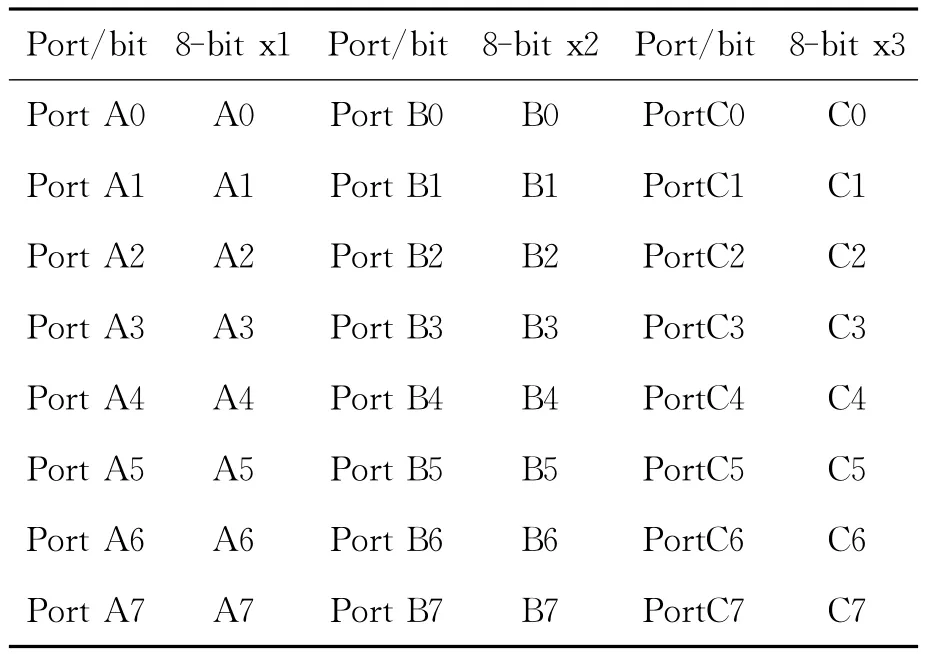

根據(jù)Camera Link編碼輸出協(xié)議,本文重點(diǎn)闡述Base型Camera Link的8-bit像素點(diǎn)的編碼方式,F(xiàn)ULL模式的拓展是簡單的。表1是Camera Link協(xié)議中抽象出來的 Port A/B/C與像素?cái)?shù)據(jù)對(duì)應(yīng)的映射關(guān)系。對(duì)于其他比特位像素點(diǎn)如10-bit,12-bit等根據(jù)Camera Link協(xié)議進(jìn)行類比映射。

表1 Base型8-bit字節(jié)分配Tab.1 Bit assignments for BASE configuration

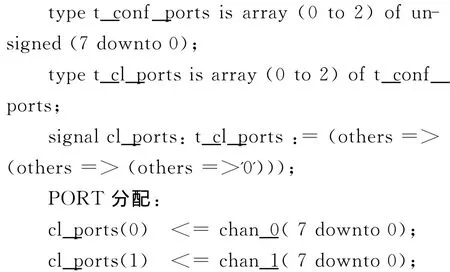

對(duì)應(yīng)上述映射關(guān)系的VHDL代碼如下所示:

定義:

其中,cl_ports信號(hào)對(duì)應(yīng)于portA\B\C,chan_0,chan_1,chan_2為8-bit像素?cái)?shù)據(jù)信號(hào)。

圖2 DS90CR287信號(hào)時(shí)序圖Fig.2 Timing diagram of DS90CR287data

2.2 數(shù)據(jù)信號(hào)和同步時(shí)鐘信號(hào)的編碼

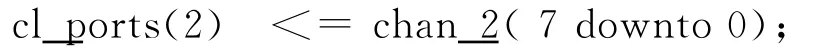

三個(gè)8bit PORT A\B\C和FVAL、LVAL、DVAL以及Spare信號(hào),一起構(gòu)成了Camera Link的28路數(shù)據(jù)信號(hào)。對(duì)這28路信號(hào)按照DS90CR287的輸入定義映射位序進(jìn)行編碼即實(shí)現(xiàn)了Camera Link的輸出數(shù)據(jù)編碼功能。Camera Link為了便于傳輸數(shù)據(jù)在采集端的正確性,在對(duì)數(shù)據(jù)編碼的同時(shí)也對(duì)采樣時(shí)鐘進(jìn)行了編碼。圖為DS90CR287數(shù)據(jù)信號(hào)和同步時(shí)鐘信號(hào)的編碼輸出時(shí)序圖[11]。28路數(shù)據(jù)信號(hào)與輸出時(shí)序圖中TxIN信號(hào)的映射如表2所示。

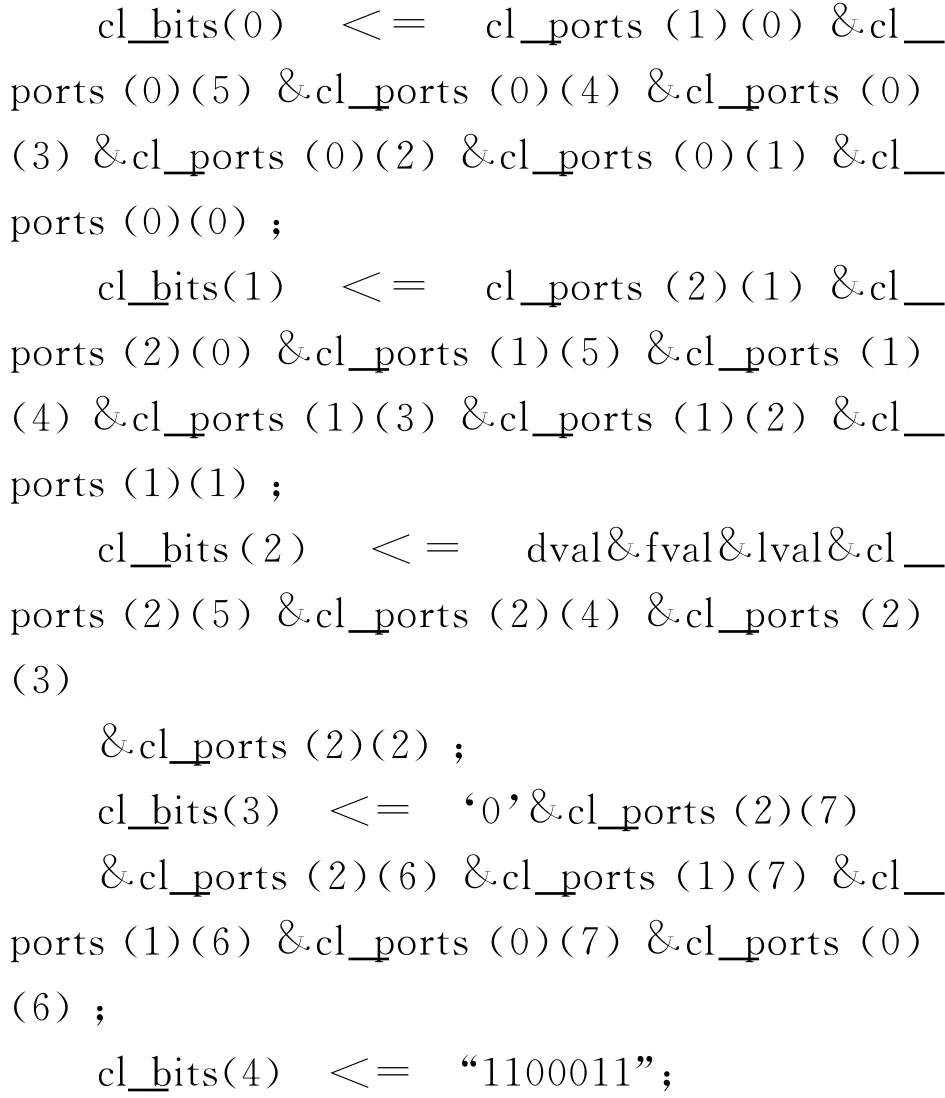

相應(yīng)的VHDL代碼如下所示:

定義:

type t_cl_bits is array(4downto 0)of unsigned(6downto 0);

signal cl_bits: t_cl_bits:= (others=>(others=>'0'));

比特分配:

其中:cl_bits是1×1維數(shù)組,cl_bits(i)是位寬為7,最左邊一位是 MSB的信號(hào)。Cl_bits(4)為數(shù)據(jù)同步時(shí)鐘信號(hào),即如圖1中的TxCLK OUT信號(hào),根據(jù)圖2的時(shí)序圖,確定cl_bits(4)的值為“1100011”。

表2 Camera Link比特分配Tab.2 Camera Link bit assignment

2.3 并串轉(zhuǎn)換

28路數(shù)據(jù)信號(hào)和同步時(shí)鐘信號(hào)編碼完成后,需要對(duì)這35路數(shù)據(jù)進(jìn)行7∶1并串轉(zhuǎn)換,以最終完成Camera Link協(xié)議的4路LVDS數(shù)據(jù)編碼輸出和1路LVDS時(shí)鐘編碼輸出。具體來說就是將已經(jīng)編碼的cl_bits(i)(其中i取0,1,2,3,4)信號(hào)進(jìn)行7∶1數(shù)據(jù)并串轉(zhuǎn)換。數(shù)據(jù)并串轉(zhuǎn)換分為兩個(gè)步驟:第一步,將cl_bits(i)中的并行7路數(shù)據(jù)轉(zhuǎn)換成并行4路數(shù)據(jù)完成數(shù)據(jù)的7∶4并串轉(zhuǎn)換。第二步,采用Virtex4FPGA內(nèi)部輸出功能模塊OSERDES[12]實(shí)現(xiàn)數(shù)據(jù)的4∶1并串轉(zhuǎn)換。并串轉(zhuǎn)換的設(shè)計(jì)框圖如圖3所示。

圖3 并串轉(zhuǎn)換框圖Fig.3 Block diagram of parallel-to-serial

具體實(shí)現(xiàn)如下:

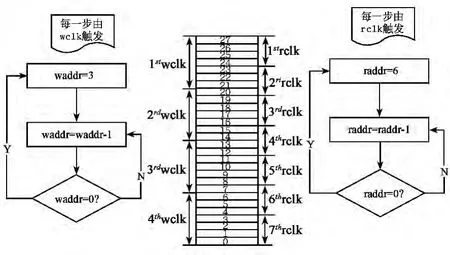

(1)使用FIFO實(shí)現(xiàn)7∶4數(shù)據(jù)轉(zhuǎn)換。該過程的重點(diǎn)是對(duì)寫和讀的控制信號(hào)的實(shí)現(xiàn)。對(duì)于每個(gè)cl_bits(i)(其中i取0,1,2,3,4),分別建立了一個(gè)28×1bit的分布式FIFO,設(shè)像素時(shí)鐘為tw對(duì)應(yīng)的頻率為fw,即FIFO寫入頻率為fw,為實(shí)現(xiàn)7∶4的數(shù)據(jù)轉(zhuǎn)換,則讀出頻率fr=7/4fw。

圖4所示為FIFO的讀寫示意圖。圖中waddr為寫節(jié)拍指示信號(hào),使用VHDL語言將其定義為2位的unsigned信號(hào),初始值為3,raddr為讀節(jié)拍指示信號(hào),定義為3位的unsigned信號(hào),初始值為6;wclk為寫時(shí)鐘,比如為40MHz,則讀時(shí)鐘rclk應(yīng)該是70MHz。

圖4 FIFO讀寫示意圖Fig.4 FIFO write and read diagram

寫進(jìn)程。第一個(gè)寫時(shí)鐘(圖中1stwclk),cl_bits(i)的MSB裝入到FIFO的27位,依次至cl_bits(i)的LSB裝入到FIFO的21位,waddr減1。第二個(gè)寫時(shí)鐘(2ndwclk),cl_bits(i)的 MSB裝入到FIFO的20地址,依次到cl_bits(i)的LSB裝入到FIFO的14位,waddr減1。以此類推,直到第四個(gè)寫時(shí)鐘,waddr為0,此時(shí)將waddr設(shè)置為3。重復(fù)以上過程。

讀進(jìn)程。定義一個(gè)4位的信號(hào)data_4b(3 downto 0),用于讀取FIFO中的數(shù)據(jù)。第一個(gè)讀時(shí)鐘(圖中1strclk),將FIFO地址為27~24的數(shù)據(jù)分別裝入到data_4b的 MSB~LSB,raddr減1。第二個(gè)讀時(shí)鐘(2ndrclk),將FIFO地址為23~20的數(shù)據(jù)分別裝入到data_4b的 MSB~LSB,raddr減1。以此類推,第七個(gè)時(shí)鐘(7thrclk),將FIFO地址為3~0的數(shù)據(jù)裝入到data_4b的MSB~LSB,raddr為0,此時(shí)將raddr設(shè)置為6。重復(fù)以上過程。

(2)設(shè)計(jì)中使用了Xilinx公司的Virtex-4系列芯片XC4VLX15作為核心芯片,使用了OSERDES原語[13]例化功能模塊OSERDES。根據(jù)設(shè)計(jì)方案,將數(shù)據(jù)率參數(shù)設(shè)置為DDR,TRISTATE_WIDTH 和DATA_WIDTH 參數(shù)設(shè)置為4,SERDES_M(jìn)ODE參數(shù)設(shè)置為“MASTER”。實(shí)現(xiàn)數(shù)據(jù)4∶1串并轉(zhuǎn)換要求。

3 仿真與實(shí)驗(yàn)

本實(shí)驗(yàn)以Xilinx公司的ISE14.1作為編譯調(diào)試軟件,使用 ModelSim SE 10.0a作為仿真平臺(tái)。本實(shí)驗(yàn)使用了Camera Link采集卡作為接收端,上位機(jī)端使用了DalsaCamExpert軟件作為人機(jī)交互端。為驗(yàn)證Camera Link編碼的正確性,實(shí)驗(yàn)分為兩個(gè)部分:(1)Camera Link編碼的時(shí)序仿真;(2)上位機(jī)端圖像數(shù)據(jù)的Camera Link編碼接收。

3.1 仿真

Testbench文件中,時(shí)鐘clk_sys為像素時(shí)鐘,設(shè)置為40MHz;clk_tx_l為FIFO讀出時(shí)鐘,根據(jù)所設(shè)置的像素時(shí)鐘,該時(shí)鐘應(yīng)該為70MHz,同時(shí)它也是OSERDES的CLKDIV;clk_tx_h(yuǎn)是2.3步驟(2)中OSERDES的CLK,為140MHz。將chan_0,chan_1,chan_2 設(shè) 置 為 全 1,chan_0< =“11111111”;chan_1< =“11111111”;chan_2<=“11111111”。LVAL和DVAL有效時(shí)間(值為邏輯1)為20個(gè)像素時(shí)鐘,每幀為2行有效數(shù)據(jù),行消影時(shí)間設(shè)置為2個(gè)像素時(shí)鐘。仿真結(jié)果如圖5所示。

圖5中,豎直虛線之間是1幀數(shù)據(jù)。包含兩行數(shù)據(jù)。為驗(yàn)證編碼的正確性,只需驗(yàn)證時(shí)鐘信號(hào)cl_bits(4)編碼的正確性就可以了,其他4路數(shù)據(jù)編碼與其完全一樣。圖中cl_bits(4)編碼后對(duì)應(yīng)信號(hào)cl_xclk,時(shí)序如圖5中放大圖所示,頻率為40MHz,高低電平比為4∶3,時(shí)序圖完全符合圖2中的時(shí)鐘信號(hào)TxCLK OUT,仿真結(jié)果驗(yàn)證了編碼的正確性。

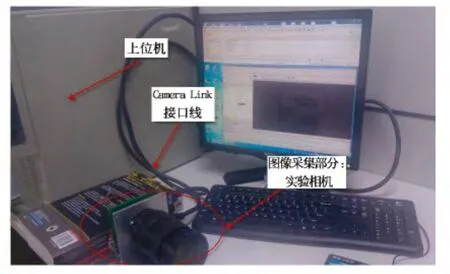

3.2 實(shí)際實(shí)驗(yàn)

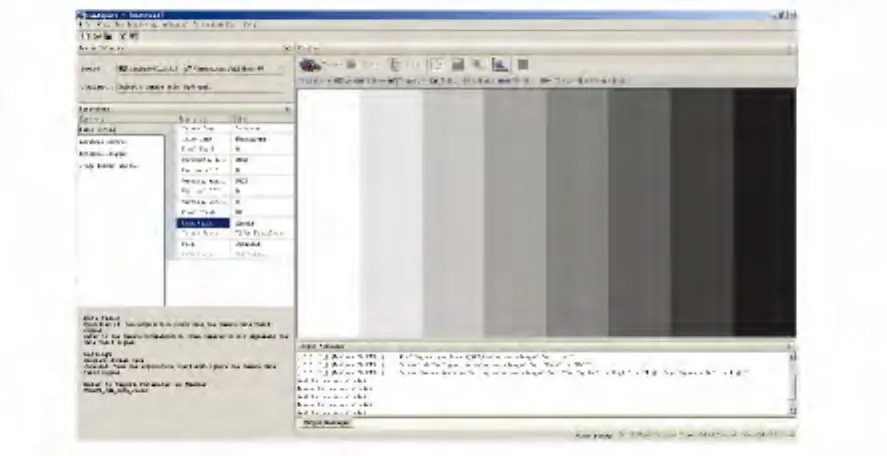

圖6是實(shí)驗(yàn)平臺(tái),采用的FPGA芯片是Xilinx公司的Virtex-4系列XC4VLX15芯片,圖像傳感器采用了CMOSIS公司的CMV2000。實(shí)驗(yàn)根據(jù)BASE型Camera Link編碼方法,通過拓展實(shí)現(xiàn)FULL模式下的圖像編碼。實(shí)驗(yàn)板將圖像數(shù)據(jù)經(jīng)過相應(yīng)的處理和Camera Link編碼,通過Camera Link傳輸線,將編碼數(shù)據(jù)傳遞到上位機(jī)的Camera Link采集卡,經(jīng)采集卡解碼,由DalsaCamExpert軟件顯示圖像相應(yīng)的信息。

圖7是上位機(jī)DalsaCamExpert軟件顯示的采集卡解碼的條紋圖像。條紋圖像為實(shí)驗(yàn)者設(shè)定。具體參數(shù)設(shè)定為:設(shè)置了8通道的數(shù)據(jù),即chan_0至chan_7,將其像素點(diǎn)的值對(duì)應(yīng)設(shè)置為255,223,191,159,127,95,63,31,構(gòu)成一定的梯度,像素時(shí)鐘為40MHz;設(shè)置LVAL有效時(shí)間為256個(gè)像素時(shí)鐘,由設(shè)置的8個(gè)通道,可知圖像每行有2 048個(gè)像素點(diǎn);設(shè)置每幀包含1024行數(shù)據(jù)。根據(jù)所設(shè)置的LVAL和FVAL信號(hào)可以知道圖像大小為2048×1024。

通過觀察分析圖7中的條紋圖像,獲得的圖像與實(shí)驗(yàn)設(shè)置的圖像參數(shù)完全符合,說明本文設(shè)計(jì)的編碼方式是可行的。

圖6 實(shí)驗(yàn)平臺(tái)Fig.6 Experiment flatform

圖7 條紋采集圖像Fig.7 Acquired image of stripe

4 結(jié) 論

為了實(shí)現(xiàn)設(shè)計(jì)Camera Link接口攝像機(jī)的集成化和小型化,本文介紹了一種采用Xilinx Virtex4系列FPGA完成Camera Link協(xié)議編碼輸出的方法。首先介紹了Camera Link接口標(biāo)準(zhǔn)以及專門輸出編碼芯片DS90CR287的時(shí)序映射圖。其次,重點(diǎn)分析了在FPGA中用VHDL語言實(shí)現(xiàn)Base模式輸出編碼的具體步驟和實(shí)現(xiàn)方法。最后,通過仿真和實(shí)際圖像采集實(shí)驗(yàn)驗(yàn)證了本文編碼方法的正確性。采用FPGA實(shí)現(xiàn)Cam-era Link輸出編碼功能,能夠減少硬件設(shè)計(jì)成本和硬件電路設(shè)計(jì)復(fù)雜度,便于設(shè)計(jì)攝像機(jī)的小型化和輕量化,在實(shí)際中具有很高的應(yīng)用價(jià)值,已在工程上得到了應(yīng)用。

[1] 劉仲宇,張濤,李嘉全,等.超小型無人機(jī)相機(jī)系統(tǒng)關(guān)鍵技術(shù)研究 [J].光電工程,2013,40(4):80-85.Liu Z Y ,Zhang T,Li J Q,et al.Key Technology of camera system for ultra-small UAV [J].Opto-Electronic Engineering,2013,40(4):80-85.(in Chinese)

[2] 辛光澤,侯宏錄,李飛,等.基于Camera Link接口的高速視頻圖像采集系統(tǒng) [J].國外電子測量技術(shù),2014,33(3):85-88.Xin G Z,Hou H L,Li F,et al.Image collection system based on Camera Link interface[J].Foreign Electronic Measurement Technology,2014,33(3):85-88.(in Chinese)

[3] 黃德天,劉雪超,吳志勇,等.基于Camera Link的高速圖像采集處理系統(tǒng)設(shè)計(jì) [J].吉林大學(xué)學(xué)報(bào):工學(xué)版,2013,43(Sup):309-312.Huang D T,Liu X C,Wu Z Y,et al.Design of high-speed image acquisition and processing system based on cameralink [J].Journal of Jilin University:Engineering and Technology Edition,2013,43(Sup):309-312.(in Chinese)

[4] LVDS Owner's Manual [M].4th Ed.Texas Instruments,2008:59-75.

[5] 魏明.基于CameraLink接口的CMOS數(shù)字相機(jī)技術(shù)研究[D].長春:長春理工大學(xué),2005:8-17.Wei M.Research on CMOS digital camera based on camera link interface[D].Changchun:Changchun University of Science and Technology,2005:8-17.(in Chinese)

[6] Specification of the Camera Link Interface Standard for Digital Cameras and Frame Grabbers[S].

[7] 張宇,楊世洪.基于CMOS圖像傳感器的高幀頻相機(jī)的設(shè)計(jì) [J].EIC,2011,18(4):41-44.Zhang Y,Yang S H.Design of high-frame camera based on CMOS image sensor[J].EIC,2011,18(4):41-44.(in Chinese)

[8] 沈鴿,王美嬌,嵇曉強(qiáng).基于CameraLink的視頻圖像采集與傳輸系統(tǒng) [J].微計(jì)算機(jī)信息,2011,27(8):99-100.Shne G,Wang M J,Ji X Q.The system of video image collection and transmission based On CameraLink[J].Microcomputer Information,2011,27(8):99-100.(inChinese)

[9] 李飛,劉晶紅,李剛,等.基于FPGA的數(shù)字?jǐn)z像機(jī)輸出視頻 DVI顯示 [J].激光與紅外,2011,41(11):1258-1262.Li F,Liu J H,Li G,et al.Displaying digital camera video on DVI monitor based on FPGA [J].LASER &INFRARED,2011,41(11):1258-1262.(in Chinese)

[10] 李勇,劉文怡.一種高速圖像數(shù)據(jù)采集存儲(chǔ)系統(tǒng)設(shè)計(jì) [J].計(jì)算機(jī)測量與控制,2013,21(2):535-539.Li Y,Liu W Y.Design of high-speed image and data storage system [J].Computer Measurement & Control,2013,21(2):535-539.(in Chinese)

[11] DS90CR287/DS90CR288A +3.3VRising Edge Data Strobe LVDS 28-Bit Channel Link-85MHZ[R].

[12] Virtex-4FPGA User Guide[R].Xilinx,UG070(V2.6),2008:386-399.