一種面向航天應用的高可靠FPGA設計架構研究

王 豪 劉 博 張旭光

上海航天電子技術研究所,上海201109

靜態存儲器(Static Random Access Memory,SRAM)型現場可編程門陣列(Field Programmable Gate Array,FPGA)功能強大,具有可重復編程、開發周期短等顯著優勢,已越來越多地應用于國內外航天領域。但SRAM型FPGA抗空間輻射能力較弱,容易發生單粒子翻轉(Single Event Upset,SEU)[1-2]問題,對衛星功能造成了不同程度的故障,因此必須采取一定的抗輻加固措施以提高其可靠性。

本文研究了一種采用三模冗余(Triple Module Redundancy,TMR)并對FPGA配置區域進行定時刷新的抗輻加固方案,同時對該方案的可靠性和安全性進行了評估,最后給出了評估結果。

1 SRAM型FPGA單粒子翻轉解決方案

SRAM型FPGA內部的配置區——配置存儲器、功能區——塊存儲器、觸發器等都是單粒子翻轉的敏感區。當一個高能帶電粒子穿過靈敏區時,將會使FPGA器件內部導通管截止、截止管導通,引起器件邏輯狀態翻轉——即單粒子翻轉[3]。因此,必須采取一定的抗輻加固措施以應對空間高能粒子對SRAM型FPGA造成的單粒子翻轉(SEU)故障。

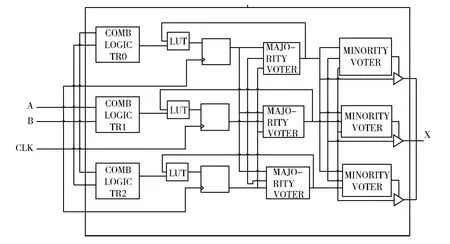

設計中常采用三模冗余(Triple Module Redundancy,TMR)[4]技術對要在 FPGA內實現的硬件設計進行保護。圖1所示為采用三模冗余架構的FPGA系統原理框圖,可以看出這種方法通過嵌入冗余處理機制到用戶應用來屏蔽故障,從而獲得正確的輸出,本質上是一種利用硬件冗余或信息冗余進行故障屏蔽的容錯方法。

圖1 三模冗余原理框圖

然而,冗余容錯方法無法改變FPGA的配置內容,所以對于發生在配置存儲器中的SEU并無糾正能力,若SEU積累將使得TMR失效,最終導致故障發作。

針對三模冗余(TMR)系統無法糾正存儲區中發生的SEU故障,本文提出一種三模冗余加回讀刷新的解決方案,應對空間FPGA單粒子翻轉。

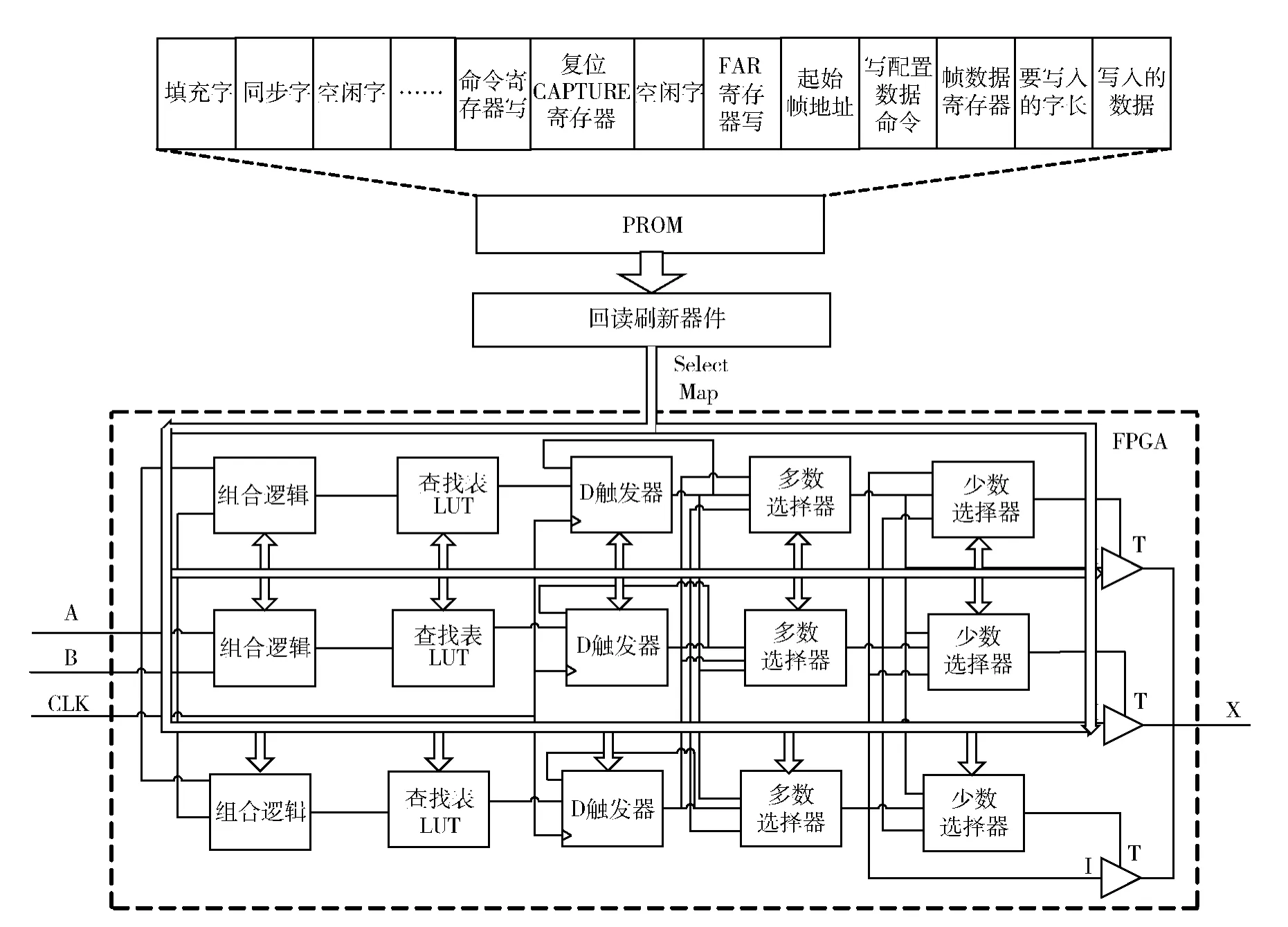

回讀刷新通過回讀刷新器件實現,有2種工作模式:回讀和刷新。回讀模式下該器件讀取FPGA內配置存儲區的數據,并與存儲在PROM中的原始配置數據進行比較,發現數據不一致的情況,就意味著配置存儲器單元發生了SEU,進而將PROM中存儲的原始配置文件重新寫入FPGA。刷新模式下不管FPGA有沒有發生SEU,均周期對配置存儲區進行刷新。采用回讀刷新加三模冗余架構的FPGA系統原理如圖2所示。其中,PROM芯片內部存儲FPGA的配置信息,該器件采用反熔絲工藝不會受空間SEU干擾;回讀刷新器件為專用ASIC芯片對空間單粒子干擾免疫,負責讀取PROM中數據并對FPGA內部配置區進行定時刷新,如果FPGA內部配置區發生SEU將對翻轉的數據進行有效糾正;FPGA內部電路采用TMR設計。

2 可靠性分析

系統可靠性是指系統在規定條件下和規定時間內完成規定功能的能力。可靠性是一個定性的概念,而實際工作中往往需要用可靠度定量地表現可靠性的高低。可靠度是指系統在初始時刻(t=0)時可靠度為1的條件下,在0~t時間內正常工作的概率。由于系統是冗余系統,系統發生故障是余度性能降級的動態過程,利用馬爾可夫過程理論能夠對余度系統進行精確的可靠性建模分析,較為真實地描述系統的實際工作過程[5-6]。

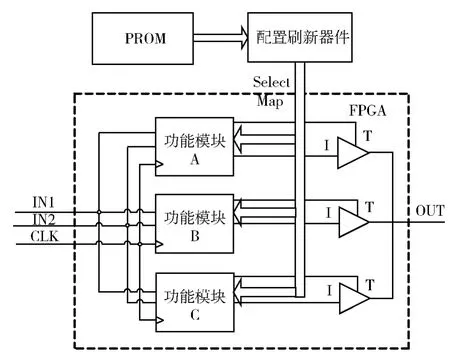

為方便討論及建模,將圖2所示的回讀刷新加TMR的FPGA系統可簡化為如圖3所示的邏輯框圖;回讀刷新器件作為SEU故障修復模塊,周期地對FPGA內部配置存儲區進行刷新。

采用TMR的系統具有23=8種狀態,當一個模塊發生故障時,不會影響系統的正常工作;而當失效模塊數≥2時,系統失效。該狀態可視為馬爾可夫吸收態。假設每個模塊的失效率都相同,均為λ,修復率為μ。

圖2 三模冗余與回讀刷新架構功能框圖

根據可靠性分析理論[7],若某模塊在時刻t正常工作,則在t+Δt時刻發生常規故障的概率為p=1-e-λΔt,當 Δt→0 該故障概率可簡化為 λΔt。

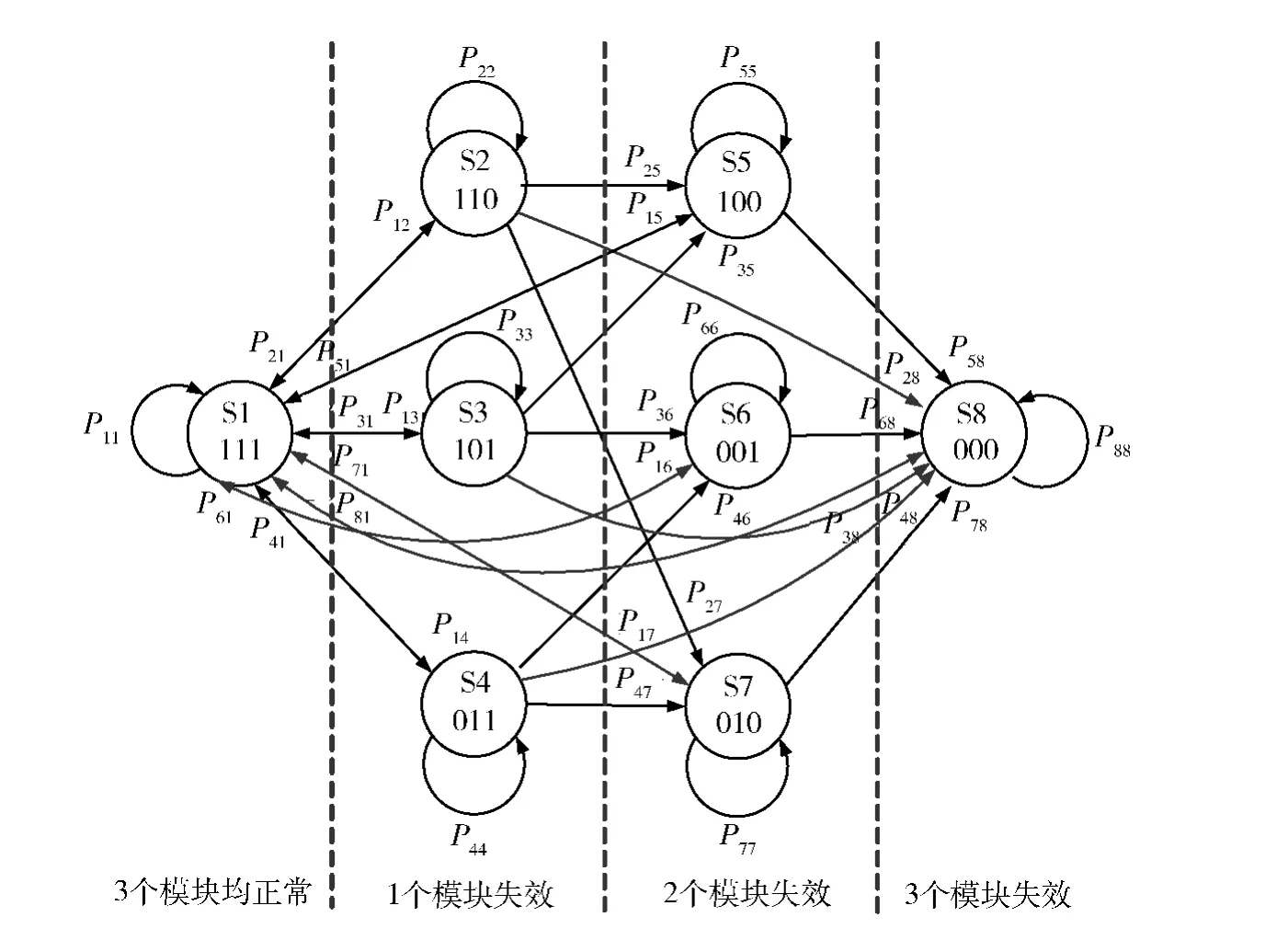

基于以上假設,對FPGA配置區進行確定周期刷新且考慮共模故障影響下的三模冗余系統的馬爾可夫模型狀態轉移如圖4所示,其馬爾可夫狀態可描述如下:

圖3 簡化后三冗余及回讀刷新FPGA系統框圖

1)狀態 S1—“111”表示 A,B,C 三個模塊均未受到SEU影響、功能均正常;

2)狀態S2—“110”表示某時刻C模塊受到SEU影響,功能異常且翻轉單元暫未得到刷新糾錯。A,B模塊正常,經三取二表決后系統仍能正常工作。

3)狀態S3—“101”表示某時刻B模塊受到SEU影響,功能異常且翻轉單元暫未得到刷新糾錯。A,C模塊正常,經三取二表決后系統仍能正常工作。

4)狀態 S4—“011”表示某時刻 A模塊受到SEU影響,功能異常且翻轉單元暫未得到刷新糾錯。B,C模塊正常,經三取二表決后系統仍能正常工作。

5)狀態S5—“100”表示某時刻 B,C模塊受到SEU影響,功能異常而且翻轉單元暫未得到刷新糾錯,經三取二表決后系統功能失效。

6)狀態S6—“001”表示某時刻 A,B模塊受到SEU影響,功能異常而且翻轉單元暫未得到刷新糾錯,經三取二表決后系統功能失效。

7)狀態S7—“010”表示某時刻 A,C模塊受到SEU影響,功能異常而且翻轉單元暫未得到刷新糾錯,經三取二表決后系統功能失效。

8)狀態 S8—“000”表示某時刻 A,B,C 模塊均受到SEU影響,功能異常且翻轉單元暫未得到刷新糾錯,系統功能失效。

圖4 采用TMR和回讀刷新的FPGA系統的馬爾可夫狀態轉移圖

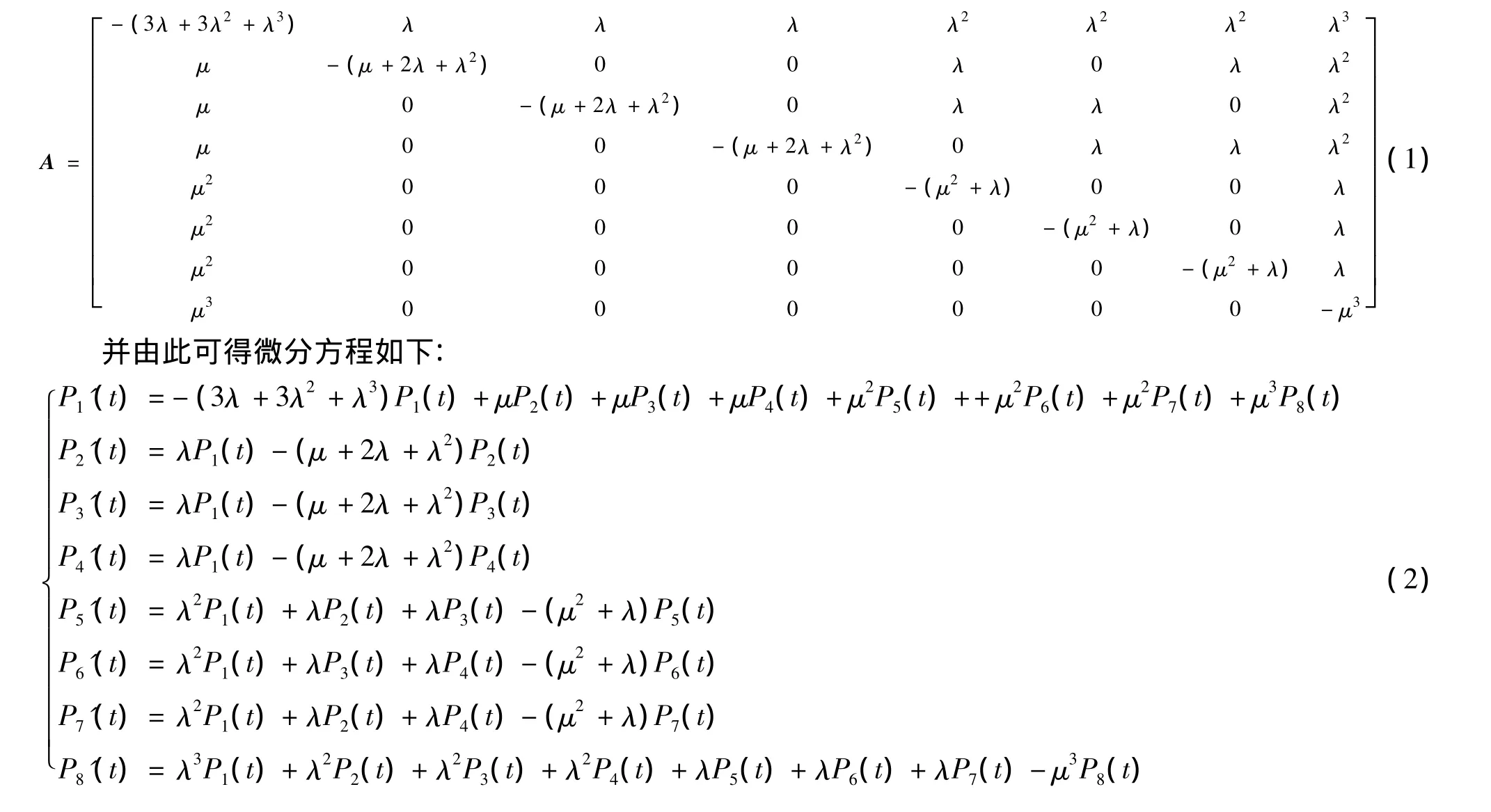

記Pi(t)=P(X(t)=i),表示t時刻系統處于狀態 i的概率,i∈ {1,2,3,...,8},令 P(t)=[P1(t),P2(t),...,P8(t)],則 P(t)滿足狀態方程:P'(t)=AP(t),其中,A為狀態轉移密度矩陣,由狀態轉移圖可知:

A和P(t)代入方程P'(t)=AP(t)中,并代入初始條件 P(0)= [1,0,0,...,0],可得到 t時刻各個狀態的概率,從而求得該系統的可靠度R(t)和安全度S(t):

3 仿真分析

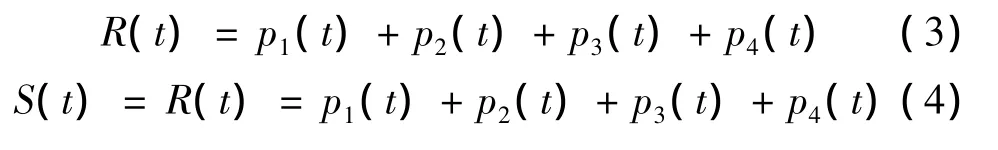

對于P(t)的狀態方程P'(t)=AP(t),可以通過Laplace變換的方法求得其解析解,進而求得系統的可靠度和安全度,但其計算工作量相當龐大,為此,采用Matlab中的求解微分方程的Ode45指令進行仿真計算[8]。其中單粒子翻轉故障率λ可參照表1所示Xilinx公司FPGA單粒子翻轉率。

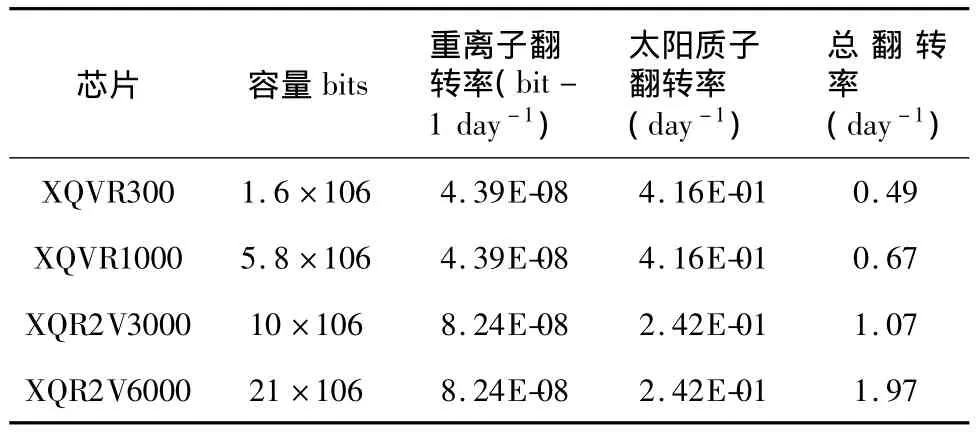

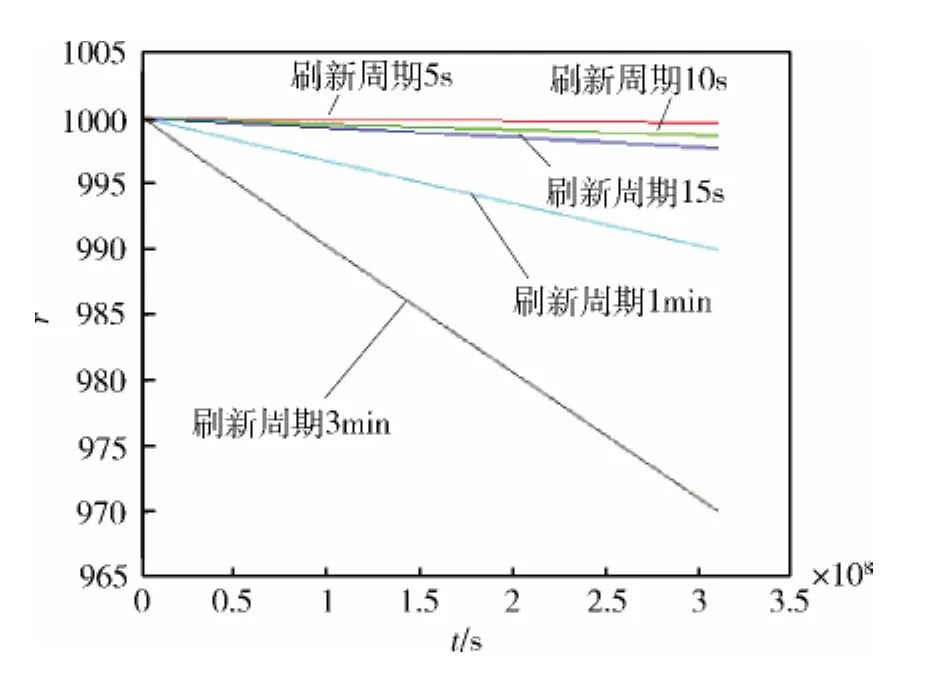

由表1可以看出隨著FPGA容量的增加,單粒子翻轉率也隨之增加。系統修復率μ與回讀刷新的頻率有關,以 5s,10s,15s,1min,3min 的刷新周期為例對采用Virtex2系列XQR2V3000型FPGA系統的可靠度和安全度進行分析。

表1 Xilinx公司單粒子翻轉率

表2 λ=1.07 day-1時參數μ對系統可靠性安全性影響

從表2可以看出,隨著參數μ的增加,三模冗余系統的可靠度和安全度均有所提高,初始時刻系統完好可靠度和安全度皆為1.000,隨著運行時間的增加,系統可靠度和安全度均有所下降。圖5所示的仿真波形為t=0~86400h,λ =1.07day-1時,三模冗余與回讀刷新系統的可靠度和安全度隨修復率μ的變化曲線。

圖6所示為 t=0~86400h,μ =0.001,λ =1.07day-1時,采用三模冗余和回讀刷新設計的FPGA系統與單模無刷新FPGA系統的可靠度[9]比對。由圖中可以看出,隨時間的增加,兩者的可靠度均有所下降,但采用三模冗余與回讀刷新的FPGA系統的可靠度明顯優于單模無刷新系統。

圖5 不同刷新周期系統可靠度r隨時間t變化曲線

圖6 三模冗余與回讀刷新系統與單模無刷新系統的可靠度比對

4 結束語

SRAM型FPGA由于具有資源豐富、可重復擦寫等優點,在宇航領域應用越來越廣,但SRAM型FPGA存在單粒子翻轉(SEU)風險,所以必須采取措施。本文提出了一種三模冗余與回讀刷新功能相結合的抗輻加固設計,并對其可靠性進行了分析和仿真,仿真數據證明該設計架構具有較高的可靠性,對宇航型號FPGA設計具有較好的參考意義。

[1] 邢克飛,楊俊,王躍科,等.Xilinx SRAM型FPGA抗輻射設計技術研究[J].宇航學報,2007,28(1):123-129.(Xing Kefei,Yang Jun,Wang Yueke,et al.Study on the anti-radiation technique for Xilinx SRAM-based FPGA[J].Journal of Astronautics,2007,28(1):123-129.)

[2] Cheatham J A,Emmert J M,Baumgart S.A survey of fault tolerant methodologies for FPGAs[J].ACM Transactions on Design Automation of Electronic Systems,2006,11(2):501-533.

[3] 邱金娟,徐宏杰,潘雄,等.SRAM型FPGA單粒子翻轉測試及加固技術研究[J].電光與控制,2011,18(8):84 ~85.(Qiu Jinjuan,Xu Hongjie,Pan Xiong,et al.Study on Testing and Harden Technique of Single Event Upset for SRAM-Based FPGA[J].Electronics Optics &Control,2011,18(8):2011:84-85.)

[4] 顧義坤,倪風雷,劉宏.Xilinx FPGA自主配置管理容錯設計研究[J].宇航學報,2012,33(10):1520~1521.(Gu Yikun,Ni Fenglei,Liu Hong.Fault-Tolerance Design of Xilinx FPGA with Self-Hosting Configuration Management[J].Journal of Astronautics,2012,33(10):1520-1521.)

[5] Swift G M,Rezgui S,George J,et al.Dynamic testing of Xilinx Virtex-II field programmable gate array(FPGA)input/output blocks(IOBs)[J].IEEE Transactions on Nuclear Science,2004,51(6):3469-3474.

[6] Graham P,Caffrey M,Johnson D E,et al.SEU mitigation for half-latch in Xilinx Virtex FPGA[J].IEEE Transactions on Nuclear Science,2003,50(6):2139-2146.

[7] 王麗華,徐志根,王長林.可維修三模冗余結構系統的可靠度與安全度分析[J].西南交通大學學報,2002,37(1):103-107.(Wang Lihua,Xu Zhigen,Wang Changlin.Reliability and Security Analysis of 3-Module Redundancy System with One Maintainable Unit[J].Journal of Southwest JiaoTong University,2002,37(1):103-107.)

[8] Dhillon B S,Subramanian P.Reliability analysis of triple modular computer systems with redundant voters and restricted maintenance[J].Journal of Quality in Maintenance Engineering,2001,7(2):151-164.

[9] 鄒見效,徐紅兵,張正遷.基于三重冗余的ETS控制系統設計及可靠性評估[J].電子科技大學學報.2010,39(5):795 ~ 799.(Zou Jianxiao,Xu Hongbing,Zhang Zhen-qian.Design and Reliability Evaluation of ETS Control System Based on Triple Modular Redundancy[J].Journal of University of Electronic Science and Technology of China,2010,39(5):795-799.)