基于FPGA的m序列信號發生器設計

蔣 權,姚振東,李 建

(成都信息工程學院 四川 成都 610225)

基于FPGA的m序列信號發生器設計

蔣 權,姚振東,李 建

(成都信息工程學院 四川 成都 610225)

m序列是一種偽隨機序列(PN碼),廣泛用于數據白噪化、去白噪化、數據傳輸加密、解密等通信、控制領域。基于FPGA與Verilog硬件描述語言設計并實現了一種數據率按步進可調、低數據誤碼率、反饋多項式為f(x)=1+x2+x3+x4+x8的m序列信號發生器。系統時鐘為20 MHz,m序列信號發生器輸出的數據率為20~100 kbps,通過2個按鍵實現20 kbps步進可調與系統復位,輸出誤碼率小于1%。

m序列;信號發生器;FPGA;Verilog

m序列是最長線性反饋移位寄存器序列的簡稱,它是由帶線性反饋的移位寄存器產生的周期最長的一種偽隨機序列。是由移位寄存器、反饋抽頭及模2加法器組成。m序列一旦反饋多項式及移位寄存器初值給定,則就是可以預先確定并且可以重復實現的序列,該特點使得m序列在數據白噪化、去白噪化、數據傳輸加密、解密等通信、控制領域使用廣泛[1-3]。因此,深入學習研究m序列具有重要的實際意義。

1 m序列信號發生器的組成

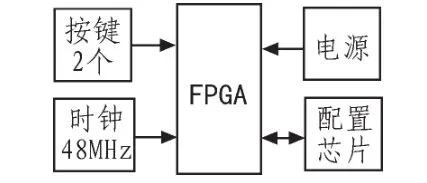

基于FPGA的m序列信號發生器硬件結構極其簡單,僅需兩個獨立按鍵(一個是復位按鍵與另一個控制數據率切換按鍵)、一個48 MHz的用于提供系統時鐘有源晶振、系統電源、一塊配置芯片、幾個簡單的電阻與電容即可實現。按鍵去抖動、按鍵復位、按鍵切換數據率、時鐘分頻等功能均在FPGA內部編程實現。

圖1 信號發生器硬件組成框圖Fig.1 Block diagram of the hardware system of signal generator

2 m序列信號發生器的關鍵設計

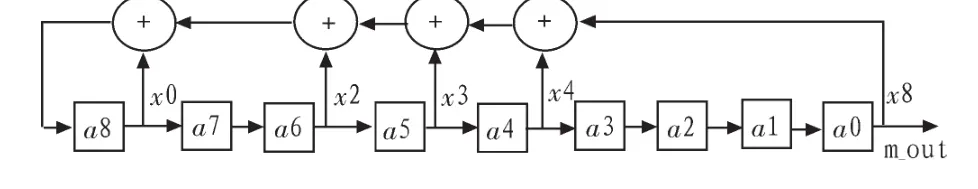

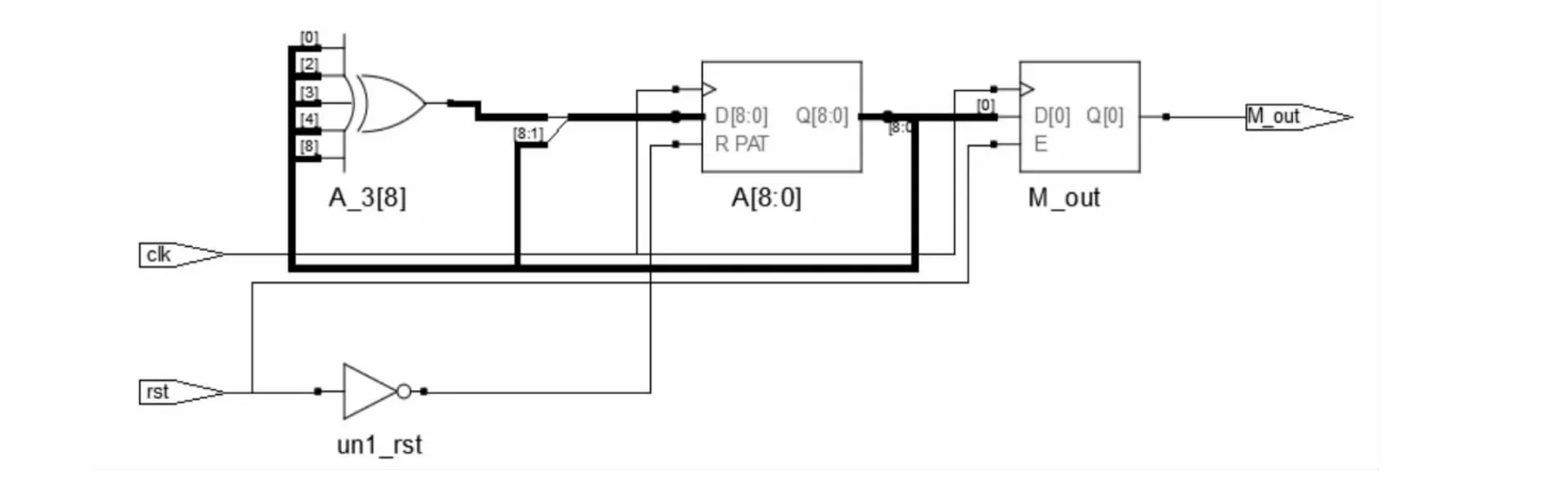

本文中m序列信號發生器的反饋多項式為:f(x)=1+x2+x3+x4+x8。其反饋及移位寄存器的關系圖如圖2所示。

從本設計中的反饋及移位寄存器的關系圖可以看出,一個時鐘周期,移位寄存器右移一位,最高位輸入為x0、x2、x3、x4及x8的異或(模2相加)。m序列的輸出是移位寄存器的最低位。圖2所示的關系是m序列呈現為隨機性、周期性的根本原因。

圖2 m序列信號發生器反饋及移位寄存器圖Fig.2 Feedback and shift register figure of the M sequence signal generator

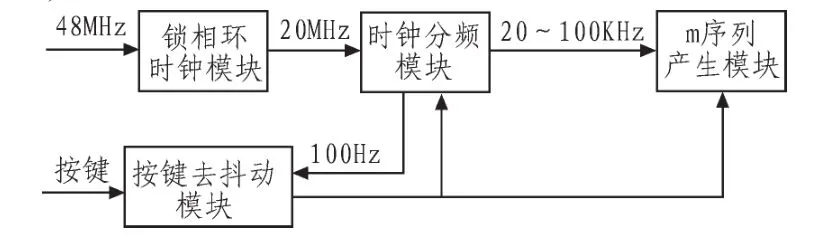

為了滿足信號發生器輸出數據率20 kbps的步進通過按鍵可調,則生成按步進20 kbps可調的時鐘是實現該功能的關鍵。當按鍵發生,時鐘的輸出頻率加20 kbps。在實際電路中,按鍵會有很大抖動,對系統會造成很大的不穩定性[4-5],因此,必須想辦法減小這樣的不利影響。在FPGA中一般使用硬件描述語言,描述一個延時電路,來實現按鍵去抖動的目的。該設計中信號發生器的FPGA內部各功能模塊及其之間的關系,如圖3所示。

圖3 FPGA功能模塊方案框圖Fig.3 Program block diagram of The FPGA function module

3 設計核心之綜合與仿真

3.1 時鐘模塊設計

在所有基于FPGA的設計中,設計滿足設計要求的時鐘信號對設計成敗起著至關重要的作用。滿足在本文所設計的m序列信號發生器的時鐘信號輸出頻率為:20 MHz、20 kHz、40 kHz、60 kHz、80 kHz、100 kHz。 輸 出 的 時 鐘 信 號 在modelsim 6.5f中的仿真波形如圖4所示。從圖4中可以看出,時鐘模塊性能滿足設計要求,設計正確。

圖4 時鐘產生模塊仿真波形Fig.4 The simulation waveform of the clock produce module

3.2 m序列產生模塊設計

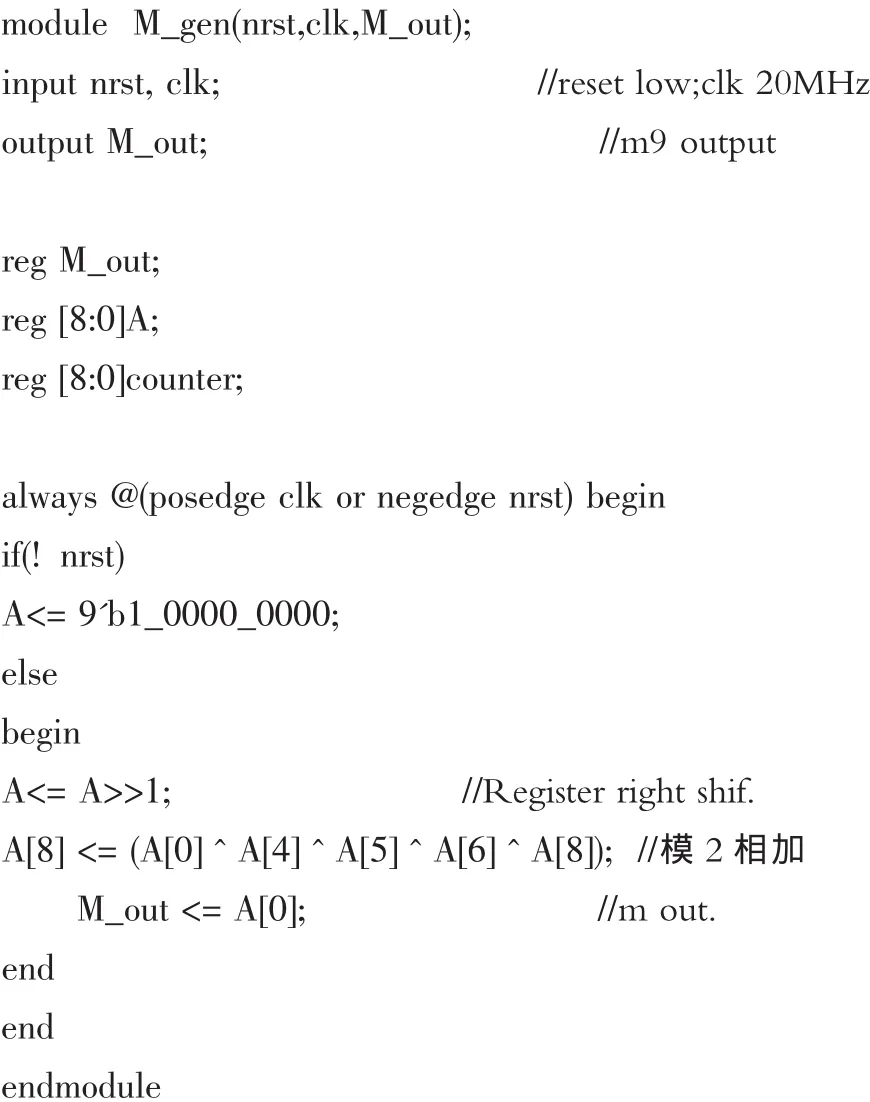

m序列產生模塊是m序列信號發生器的最核心部分。文中的 序列生氣器核心模塊的 的代碼為

圖5 m序列產生模塊Synplify綜合結果圖Fig.5 The Synplify synthesis results of the M sequence produce module

從Verilog代碼可以看出,m序列產生模塊實現極其容易,只需要一個移位寄存器、一個模2加法器即可實現m序列的產生。

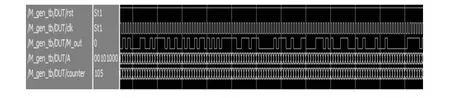

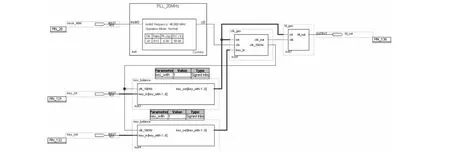

本系統中m序列產生模塊在Synplify綜合結果圖、在modelsim 6.5f中的仿真波形圖,分別如圖5、6所示。從圖5、6中可看出,該模塊產生了周期為217的周期序列,設計正確。圖7是系統的quartus II頂層模塊圖。

圖6 m序列信號發生器系統仿真波形Fig.6 The system simulation waveform of the M sequence signal generator

圖7 系統頂層模塊圖Fig.7 The module chart of system top-level

4 結論

當信號發生器的移位寄存器A的初值A=9’b1_0000_0000時,m序列的周期 T=217,輸出的周期m序列為:0000000011111010110011011111000110100110101110 110000011011011001001110011001111111011110000101010 011110110100010100001100101111010010010100101101010 101111110011101110000001011100100011000011101010001 110001001000010001。

該信號發生器實現了輸出數據率在20~100 kbps之間,并實現按20 kbps的步進可調功能;輸出數據率僅在輸出60 kbps的數據率時有較大誤差,數據率偏小約0.2%。該m序列信號發生器性能穩定,實現所有設計功能,符合設計要求。

[1]樊昌信,曹麗娜.通信原理[M].北京:國防工業出版社,2009.

[2]田耘,徐文波,張延偉.無線通信FPGA設計[M].北京:電子工業出版社,2009.

[3]肖國鎮,梁傳甲,王育民.偽隨機序列及其應用[M].北京:國防工業出版社,1985.

[4]張晶,王立松,李鐵才.數控操作面板控制功能的CPLD實現方法[J].組合機床與自動化加工技術,2007(5):51-54.

ZHANG Jing,WANG Li-song,LI Tie-cai.Implementation of Control Functions of the CNC Control Panel with CPLD[J].Combination Machine Toolsand Automatic Processing Technology,2007(5):51-54.

[5]楊澤林,郭中華.一種去抖動延時可調鍵盤電路的設計[J].電子技術,2004(9):62-63.

YANG Ze-lin,GUO Zhong-hua.Design of A to jitter delay adjustable keyboard circuit[J].Electronic Technology,2004(9):62-63.

[6]彭文劍.q元M序列的生成[J].微處理機,2006,8(4):101-103.

PENG Wen-jian.The generation of an m sequence about qary[J].Microprocessors,2006,8(4):101-103.

Design of an m sequence signal generator based on FPGA

JIANG Quan,YAO Zhen-dong,LI Jian

(Chengdu University of Information Technology,Chengdu 610225,China)

m sequence is a pseudo random sequence(PN code),widely used in whitening and dewhitening of data,encryption and decryption of transmission data in communications,control fields.Based on FPGA and Verilog hardware description language,design and realize an adjustable data rate,low data error m sequence signal generator,the feedback polynomial of which isf(x)=1+x2+x3+x4+x8.System clock of this signal generator is 20 MHz,system output data rate is from 20 to 100 kbps,through two keys can realize 20 kbps step-by-step adjustment and system reset.The value of output data rate error is less than 1%.

m sequence;signal generator;FPGA;Verilog

TN919

A

1674-6236(2014)13-0155-03

2013-10-01 稿件編號:201310003

蔣 權(1987—),男,四川南充人,碩士研究生。研究方向:信號與信息處理、軟件無線電。