數字集成電路時序優化策略

陳獻鋒,白雪飛,方 毅

(1.中國科學技術大學電子科學與技術系集成電路實驗室,安徽合肥230027;2.中國科學技術大學 信息學院23系,安徽合肥230027)

0 引言

伴隨著數字芯片進入超深亞微米工藝并且尺寸還在不斷縮小,以及現代高速通信系統數據吞吐量的不斷增大,數字芯片的工作頻率越來越高,數據位寬也越來越大。但芯片內部的各種復雜的功能,如龐大的加減乘除運算,給芯片造成了很大的片內延遲,這就極大的限制了芯片的最高工作頻率。同時集成電路尺寸縮小瓶頸的限制和復雜度的高速提升,時序必然成為令電路工程師頭疼的問題。如何在既滿足功能實現的情況下,實現數字芯片的時序收斂,將是數字電路工程師在面對復雜數字電路時能否順利流片的一個關鍵。

1 前端RTL代碼優化

1.1 硬件角度的編碼思想

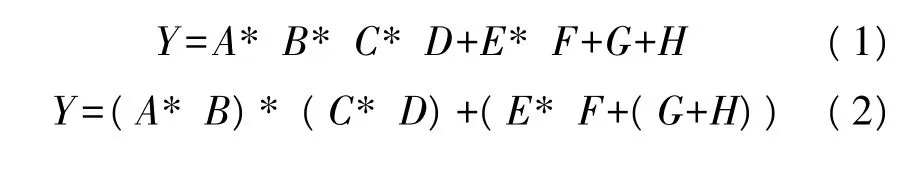

在RTL代碼的編寫過程中,實時考慮硬件資源的結構,通過代碼不同風格的變換,選擇延遲較小的代碼編寫方式。例如功能相同的式(1)和式(2)就分別對應圖1(a)和圖1(b)兩個不同延時的電路。

圖1 不同代碼編寫方式所對應的門級電路Fig.1 Different coding styles and their corresponding gate level circuit

1.2 流水線技術

某些實現復雜功能的組合邏輯電路級數很多,延遲很大,這樣就使整個系統不能運行在很高的頻率上。對于很多這樣的情況,可以采用流水線技術以大幅度提高系統運行速率。

在數字電路設計中,流水線設計是指把規模較大、層次較多的組合邏輯電路分為幾個級,在每一級插入寄存器組暫存中間數據。這樣就把原來在一個周期內執行的較為復雜的操作分成幾步較小的操作,并在多個較高速的時鐘內完成。

對于電路結構可以比較明確劃分層次的復雜組合邏輯電路比較適合用流水線技術,以縮短寄存器間的延遲,實現運行速度的提升。常見的流水線設計有流水線CPU、加/乘法器以及DSP中的多種變換[1]。流水線設計的代價是增加了寄存器邏輯以及系統復雜度。

1.3 并行結構

當一個串聯邏輯估值函數可以分解和并行地估值時,可將該函數拆分為更小的獨立操作,然后再重新組合它們[2]。例如,一個64位的乘法器可以拆分為3個32位的乘法器:

X={H,L}

X是一個64位操作數,H為高 32位,L為低32位。因此,64位的乘法可拆分為:

SUM=X1*X2={H1,L1}*{H2,L2}=

{(H1*H2),(H1*L2+H2*L1),(L1*L2)}

由此就把64位乘法器轉換為32位的乘法器和加法器(若為冪運算則可簡化為一次移位操作)的結合。隨著位數的減半,即可大大縮短延遲路徑,改善電路時序。

1.4 寄存器重定時

寄存器重定時是指在保持系統的功能不變的前提下,平等地重新分布寄存器之間的邏輯,減少任何兩個寄存器之間的最壞延遲。在RTL代碼中人為手動地均衡寄存器間的邏輯,這種方法在關鍵路徑和相鄰路徑之間邏輯高度不平衡時是一種比較有效的方法。

2 邏輯綜合優化

2.1 邏輯綜合概述

邏輯綜合(Logic Synthesis)是指數字電路由高抽象級描述,經過布爾函數化簡、優化后,轉換到的邏輯門級別的電路連線網表的過程。ASIC設計中普遍使用的綜合工具是 synopsys公司的 Design Compiler(DC)和Cadence公司的RTL Compiler。以DC為例,有了以硬件思想優化過的代碼后,首先要編寫設計的時序約束腳本,對設計進行合理的約束,但不要過約束。綜合工具根據設計人員編寫的時序約束文件對RTL代碼進行翻譯、優化、門級映射后得到門級網表,并給出時序報告。在時序報告中,若時序得不到滿足,對于一般的設計,時鐘周期10%的時序違例一般是可以通過綜合工具將其優化掉的。文獻[3]也給出了一些常用的時序優化方法。

2.2 DC的基本優化

首先根據時序報告找到時序關鍵路徑,查看關鍵路徑造成延遲的主要原因。對于路徑中延遲很大的器件,如果不是必須用到,可在綜合約束腳本中使用set_dont_use命令將其禁用以使用其他器件或組合電路替代,并重新綜合并查看關鍵路徑時序違例是否得到改善。然后通過使能compile命令的-map_effort high選項,DC會將關鍵路徑返回邏輯層次重建和重新映射,反復迭代優化[4]。同時可以通過控制DC的compile命令中的選項來達到深度優化。該命令可通過選擇以下選項優化時序:

1)邊界優化[4](boundary_optimization),DC 的邊界優化是指跨module對設計進行優化,可優化掉模塊的常數輸入邏輯、無連接的pin、模塊間直接連接的邏輯器件,一些信號的名字同時也會丟失。因此除了要保留做驗證的模塊外,可通過set_boundary_optimization命令選擇時序緊張的模塊進行邊界優化。

2)自動取消模塊組合[4],通過-auto_ungroup delay選項,該選項通過采取智能取消模塊組合策略來嘗試改善總體時序。此選項著重優化包含關鍵路徑或極可能成為關鍵路徑的模塊組合。

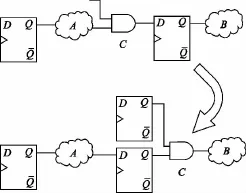

2.3 綜合中的寄存器重定時

對于高性能、時序緊湊的設計,可使用DC工具的compile_ultra命令,該命令對關鍵路徑的優化提供了相對簡單的方法。該命令的-retime選項可調節寄存器前后邏輯以減小總的時序違例[4]。與RTL代碼優化中的寄存器重定時功能類似,如圖2所示。

圖2 邏輯綜合中的寄存器重定時Fig.2 Retiming in logic synthesis

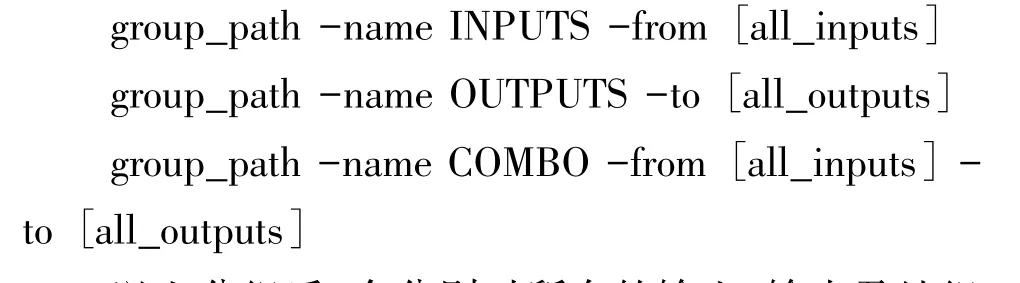

2.4 用戶自定義Path Groups

在邏輯綜合中,DC根據捕獲時鐘將各時序路徑歸進不同的path group,并在不同的path group中從各組的關鍵路徑開始優化。通過report_path_group命令可以查看在設計中定義了哪些path groups。默認情況下,當在一個path group中的所有路徑都滿足時序或者該path group中關鍵路徑的時序不能再進一步提升了,就不會再對該path group進一步優化了。然而在實際設計中,次關鍵路徑往往是和關鍵路徑是邏輯交疊或邏輯相關的,次關鍵的路徑得到優化后往往會使關鍵路徑的時序得到很大改善。甚至有時關鍵路徑的時序并非是系統必要滿足的,然而卻導致其他重要的次關鍵路徑的時序得不到滿足。而且越少的時序違例對于后端布局布線對時序的優化來說也更容易實現時序收斂。此時,我們就希望DC對次關鍵路徑進行優化。首先,可通過用戶自定義path group,將不同的路徑按類別分別定義不同的path group進行優化。例如,可按輸入、輸出和組合邏輯分組:

以上分組后,會分別對所有的輸入、輸出及純組合邏輯三部分進行優化,而不會僅僅按照系統時鐘對設計進行分組優化。其次,還可通過group_path命令的-critical_range選項對path group中的次關鍵路徑進行優化。該選項后面需要指定一個非負數值,默認值為0,表示只對關鍵路徑進行優化。若設置為0.2,則表示時序違例在關鍵路徑時序違例值20%以內的路徑均會被優化。如果要所有路徑均得到優化,則將該值設置得非常大即可,但同時會增加優化時間。一般該值設置在時鐘周期的10%以內。此外,還可通過-weight選項對path group設置權值以改變其優化的優先級,該值的范圍為0到100。權值乘以關鍵路徑的時序違例值即得到path group的路徑花費,花費越大的 path group的優先級別越高。

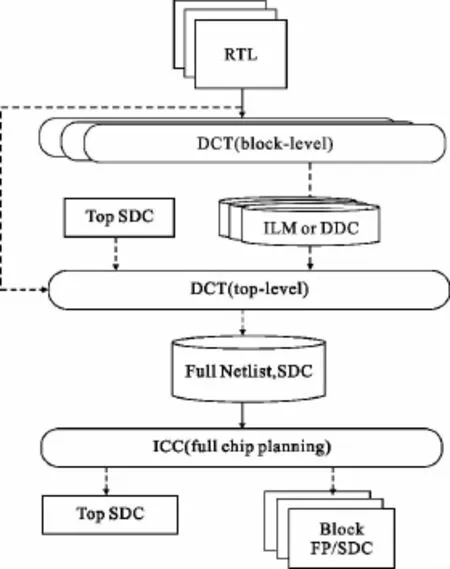

2.5 Topographical模式

在復雜、高頻的超深亞微米及以下的數字電路設計中,線延遲已成為主要的延遲之一,而且常用的線載模型(WLM)的延遲計算和版圖信息沒有相關性,因此造成了時序違例和布線沖突的不可預見性,導致布線工具為優化時序進行過多的迭代甚至達不到時序收斂。對于此類設計,如果一次綜合后或布局布線后還存在很大的時序違例,可采用DC的topographical模式。該模式首先對設計做一個預布局,隨后可根據虛擬走線的信息計算走線的延遲,得到一個與物理版圖相關的相對真實的延遲信息,使得綜合優化的結果更容易在布局布線時實現時序收斂。該模式主要包括兩個步驟[5]:

第一步,利用整個設計的 RTL代碼在DC的topographical模式下(top-down或 bottom-up)生成一個全設計的網表,然后再用該網表和時序約束文件、物理庫文件在IC Compiler中進行層次化的布局,最后得到整個芯片的一個初始布局信息。過程如圖3 所示[5]。

圖3 從RTL到floorplan流程Fig.3 Flow from RTL to floorplan

第二步,利用第一步得到的描述芯片布局信息的物理約束文件和設計網表、時序約束文件、物理庫文件再綜合,即得到了與芯片布局布線信息相關的邏輯綜合結果[5]。

2.6 優化結果查看

以上優化后會自動生成一個default.svf文件,可通過查看該文件以及對比前后綜合報告,查看以上優化選項相應的對設計做了哪些優化。

3 結語

文中重點討論了數字集成電路設計從RTL代碼到邏輯綜合過程中時序優化的幾種最主要的方法。根據不同的設計,靈活地運用各種時序優化方法對電路進行深入優化,可節省大量的芯片開發時間并得到穩定可靠的芯片。此外,在芯片物理設計階段,通過更改器件尺寸、插入buffer和spare cell、手動調整路徑等方法也可極大減少芯片時序違例情況。總之,在深入理解芯片時序的概念后,并以底層電路對應具體算法的思想去優化,才能快速準確地實現芯片時序的最優化。

[1] 王亞春,蔡德林,張夢龍,等.流水線CORDIC算法的FPGA 實現[J].通信技術,2010,43(11):169-170.WANG Ya-chun,CAI De-lin,ZHANG Meng-long,et al.The FPGA Implementation of Pipeline CORDIC Algorithm[J].Communications Technology,2010,11(43):169-170.

[2] Steve Kilts.高級 FPGA設計:結構、實現和優化[M].孟憲元,譯.北京:機械工業出版社,2009:6-8.Steve Kilts.Advanced FPGA Design:Architecture,Implementation,and Optimization[M].MENG Xianyuan,Translated.Beijing:China Machine Press,2009:6-8.

[3] 張佾.超大規模數字集成電路的時序分析與優化[D].上海:復旦大學,2008.ZHANG Yi.Timing Analysis and Optimization of Very Large Scale Digital Integrated Circuit[D].Shanghai:Fudan University,2008.

[4] Synopsys CO.,LTD.Design Compiler User Guide(Version H-2013.03)[M].USA:Synopsys,2013:210-237,287-376.

[5] Synopsys CO.,LTD.Hierarchical Flow Support in Synopsys Design Compiler Topographical Mode Application Note(Version A-2007.12-SP2)[M].USA:Synopsys,2008:12-26.