SOPC在μC/OS-II系統下的實時調試功能研究*

屈環宇,屈百達

(江南大學 輕工過程先進控制教育部重點實驗室,無錫 214122)

?

SOPC在μC/OS-II系統下的實時調試功能研究*

屈環宇,屈百達

(江南大學 輕工過程先進控制教育部重點實驗室,無錫 214122)

隨著微電子技術的飛速發展,越來越多的產品選擇基于FPGA的SOPC系統設計。本文針對SOPC系統的硬件設計及軟件的安全性、實時性、可移植性等方面的需求,在SOPC系統上移植μC/OS-II操作系統,并實現基于時間戳的調試功能。

SOPC;μC/OS-II;時間戳; FPGA

引 言

SOPC技術涵蓋嵌入式系統設計全部內容,它是由單個集成芯片完成整個嵌入式系統的主要邏輯設計功能,通過邏輯編程實現硬件和軟件上的裁減、擴充、升級。硬件技術是以PCB和電磁兼容性分析、信號完整性分析為基礎的高速電路設計技術。軟件技術是以RTOS和驅動程序為中心的軟件設計技術。本文以CYCLONE IV芯片為載體,設計了基于FPGA的SOPC系統,移植μC/OS-II實時系統,并實現時間戳功能,以利于系統實時調試。

1 SOPC硬件系統的設計

在FPGA上實現SOPC硬件系統的設計,此系統主要是由軟核系統、硬實時部分、邏輯電路組成。本文設計了基于NIOS-II軟核與μC/OS-II結合的最小實時調試系統。

NIOS-II軟核的硬件設計主要在Quartus軟件的SOPC Builder模塊中實現,它是由NIOS-II微處理器作為CPU,NIOS-II微處理器體系結構支持某些用戶自定義功能的指令,并用硬件電路實現這些指令功能,其地位與NIOS-II微處理器內部自帶指令集中的指令地位等價。NIOS-II可以根據應用的需要配置不同資源、不同速度級別的CPU、Debug單元、可配置大小的數據Cache、指令Cache、MMU、MPU、中斷及通用寄存器。

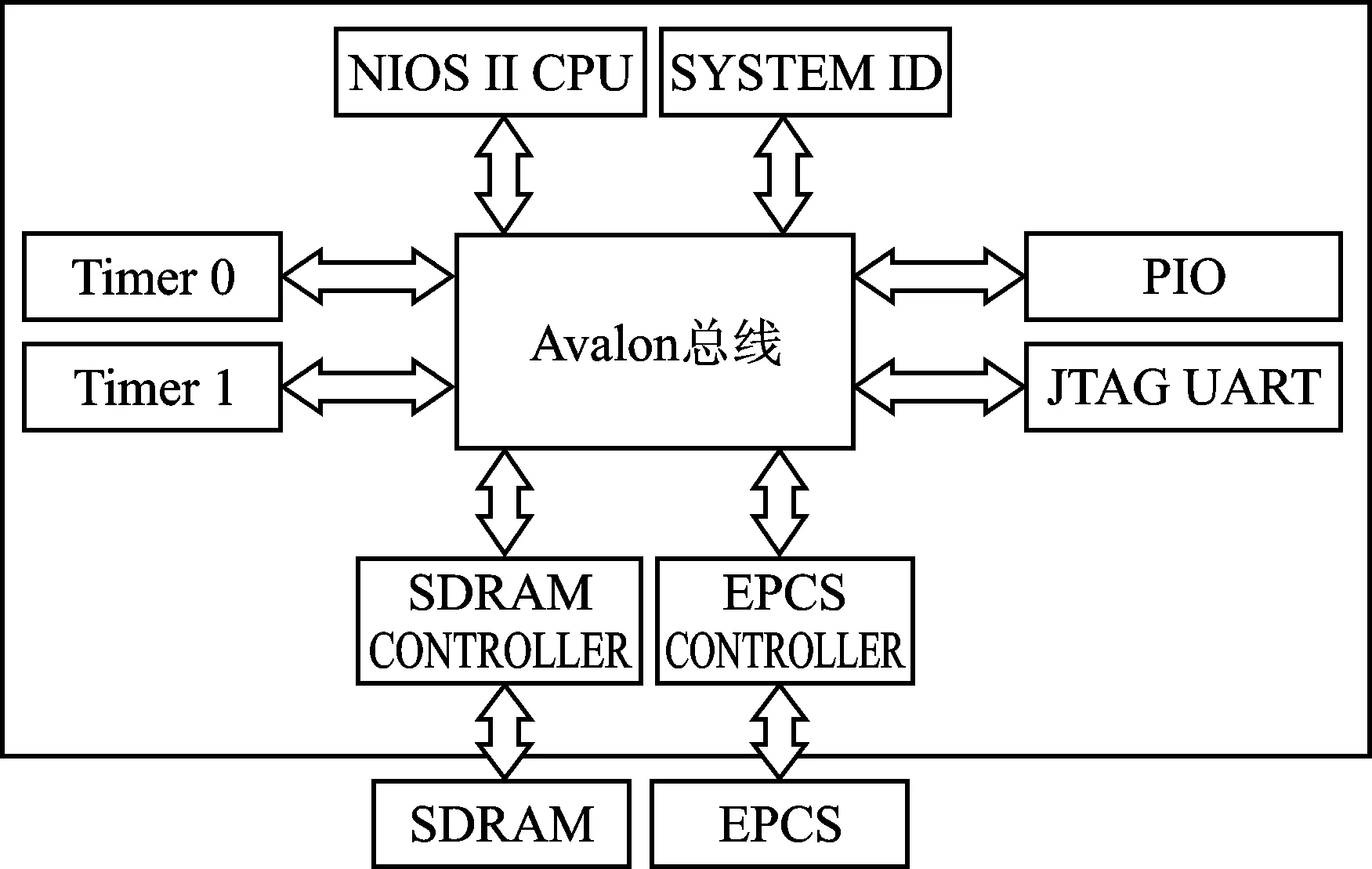

Avalon總線是NIOS-II硬件系統設計中的重要組成部分,它為CPU與外設之間指令與數據的通信提供了一種互聯規范,實現CPU指令總線、數據總線與外設的主從關系以及沖突裁決等功能。SOPC硬件系統如圖1所示。

圖1 SOPC硬件系統

CYCLONE IV系列FPGA芯片每個時鐘輸入經過一個PLL后,可產生5路時鐘輸出,每個輸出均可配置相應的分頻、倍頻、相移。本文用了2路輸出,一路提供CPU的主頻時鐘,另一路經過相移后作為SDRAM的主頻。該SOPC系統的RTL級視圖如圖2所示。

圖2 SOPC的RTL級視圖

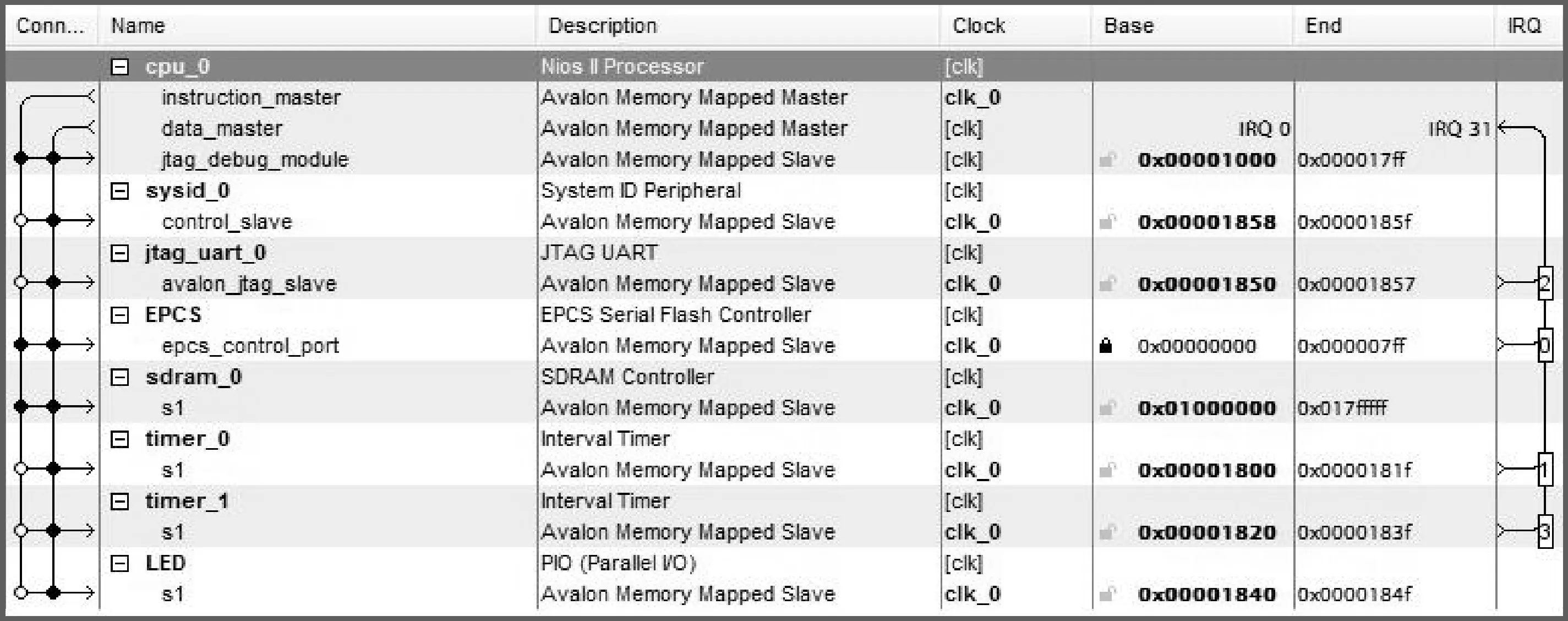

系統在SOPC Builder中的CPU與外設之間指令總線、數據總線、時鐘源、尋址地址范圍、中斷優先級等設置如圖3所示。

圖3 CPU與外設的系統關系圖

基于NIOS-II的SOPC主從關系建立好后,生成對應的硬件系統描述文件,該描述文件為NIOS-II IDE提供系統對應的硬件尋址范圍等相關內容,建立并運行TCL腳本文件,將FPGA的引腳與SOPC的硬件電路引腳相匹配。文件進行分析、綜合等操作后得到系統級的硬件配置文件。

2 SOPC軟件系統的設計

SOPC的軟件可在NIOS-II IDE平臺上開發,根據之前生成硬件系統描述文件創建相應的工作空間。每個工作空間主要由2個工程組成,一個工程主要存放SOPC的軟件代碼,另一個工程主要存放SOPC的板級硬件描述。

為方便用戶的使用,NIOS-II IDE提供了一些工程模板,其中有一個是Hello MicroC/OS-II的工程模板,創建了這個模板,就基本實現了μC/OS-II系統在ALTER NIOS-II軟核上的建立。對于實時性很強的應用,在NIOS-II IDE中可以創建一個硬件定時器,并利用時間戳來進行實時測量,從而實現CPU輸入時鐘級的實時調試。

在SOPC的硬件系統設計中,創建了兩個定時器:第一個定時器為μC/OS-II提供時基中斷,中斷間隔為1 ms;第二個定時器用于為時間戳計數提供時鐘。這兩項功能在BSP Editor中設置。

#defineALT_SYS_CLK TIMER_0

#defineALT_TIMESTAMP_CLK TIMER_1

時間戳功能的相關函數申明在sys/alt_timestamp.h頭文件中,在使用時間戳功能之前,先要調用alt_timestamp()函數開啟時間戳功能。

在μC/OS-II系統中共建立了兩個任務,任務體的代碼分別為:

t1 = alt_timestamp();

printf("時間戳(t1) = %ld ", t1);

IOWR_ALTERA_AVALON_PIO_DATA(LED_BASE, 1);

OSTimeDly(1000);

t2 = alt_timestamp();

printf("時間戳(t2) = %ld ", t2);

IOWR_ALTERA_AVALON_PIO_DATA(LED_BASE, 2);

OSTimeDly(2000);

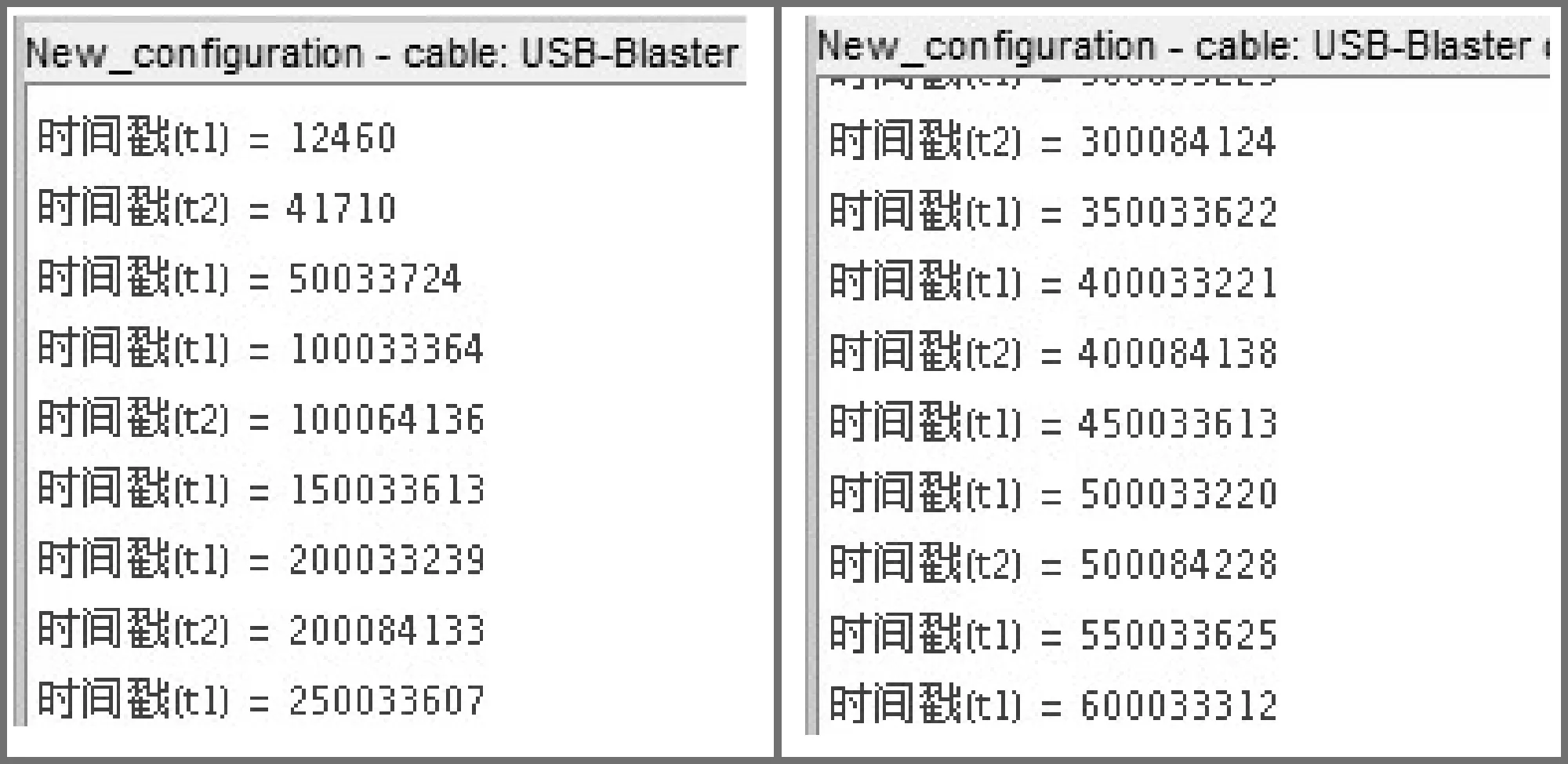

SOPC系統的輸入頻率為f=50 MHz。故時間戳的計數值每秒增量為50M,時基中斷F1=1 000 Hz。

時間戳計算方式如下:

其中,T1、T2分別為任務1和任務2每次執行的時間間隔。

編譯程序并配置運行模式為NIOS-II-HARDWARE,下載在Eclipse的Console顯示了從UART中接收到的字符輸出。由圖4可以看出,時間戳值與理想值的偏差非常微小。

結 語

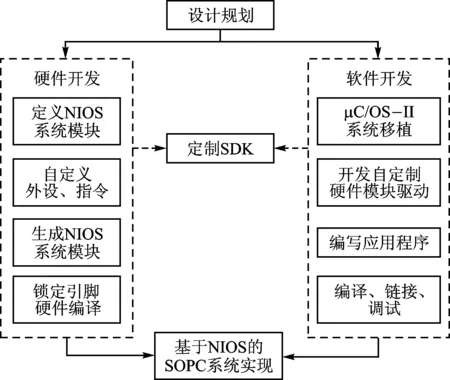

基于FPGA的SOPC系統設計涉及到硬件開發與軟件開發兩部分,其基本流程圖如圖5所示。

基于NIOS-II的SOPC發揮了軟核嵌入式微處理器的性能,用戶可以獲得超過200DMIPS的性能,在超過60

圖4 時間戳值反饋表

圖5 SOPC開發的流程圖

[1] Corporation A. SOPC Builder User Guide [EB/OL]. (2010-10)[2013-10-04]. http://www.altera.com.cn/literature/ug/ug_sopc_builder.pdf.

[2] Corporation A. Using MicroC/OS-II RTOS with the Nios II Processor Tutorial[EB/OL]. (2011-05)[2013-10-12].http://www.altera.com.cn/literature/tt/tt_nios2_MicroC_OSII_tutorial.pdf.

[3] 王剛,張瀲. 基于FPGA的SOPC嵌入式系統設計與典型實例[M]. 北京:電子工業出版社, 2009.

[4] 宋彩利. 數字系統設計與SOPC技術[M]. 西安:西安交通大學出版社, 2012.

屈環宇(嵌入式系統設計師),主要從事檢測技術及自動化裝置的研究;屈百達(教授),主要從事PLC應用技術及最新器件應用技術研發與實驗。

Research of μC/OS-II with Real-time Debugging in SOPC System

Qu Huanyu, Qu Baida

(Key Lab of Advanced Process Control for Light Industry, Jiangnan University ,Wuxi 214122,China)

With the rapid development of microelectronic technology, more and more products chooses SOPC system based on FPGA. In this paper, with the needs of security real-time, portability of SOPC system's hardware and software design, the research transplantates μC/OS-II operating system in the SOPC system,and realizes the debugging functions based on timestamp.

SOPC;μC/OS-II;timestamp;FPGA

國家級-高等學校學科創新引智計劃基金(B12018)。

TP332.2

A

迪娜

2013-10-22)