基于FPGA的CCD低噪聲測量系統設計*

夏真珍, 汪 濤, 張 俊

(重慶大學 物理學院,重慶 401331)

基于FPGA的CCD低噪聲測量系統設計*

夏真珍, 汪 濤, 張 俊

(重慶大學 物理學院,重慶 401331)

為了提高電荷耦合器件(CCD)一維尺度無接觸測量系統的精度和集成度,設計了以現場可編程門陣列(FPGA)器件為核心的測量系統。對CCD輸出信號進行低通濾波和相關雙采樣技術處理,降低了CCD信號噪聲。模擬信號轉換為12位數字信號后,傳輸至FPGA內嵌的FIFO中,提高了系統的集成度和穩定性。使用Verilog HDL語言對驅動時序發生器進行了硬件描述,并通過夫瑯禾費單縫衍射實驗來驗證系統的可靠性和精度,實驗表明:該系統穩定,精度達到0.82 %。

電荷耦合器件; 現場可編程門陣列; 低通濾波; 相關雙采樣

0 引 言

隨著光電子技術的發展,涌現出很多光電器件,電荷耦合器件[1](charge-coupled device,CCD)為一種新型光電器件,這些年來被廣泛應用于光學測量。隨著CCD性能不斷提高,測量系統快速采樣、存儲、處理和傳輸,是CCD數據采集發展的新方向。CCD分為面陣CCD和線陣CCD,而線陣CCD具有靈敏度高、光譜響應寬、測量范圍大、線性好等優點,在一維尺度測量領域顯示出其獨特的優勢[2]。

本文設計目的是提高系統一維尺度測量的集成度和精確度。因此,使用功能強大的現場可編程門陣列(FPGA)單芯片作為主控芯片,選用的是Altera公司EP3C16作為時序發生器,同時利用其內部自帶的RAM塊,建立異步FIFO,使CCD系統更小型化、集成化。同時選用東芝公司的TCD1209D作為圖像采集單元,AD公司AD 9945作為A/D轉換器。本文對噪聲進行了系統分析和處理,提高了系統的精度和抗干擾能力,實驗表明:該系統測量精度達到0.82 %。

1 系統結構

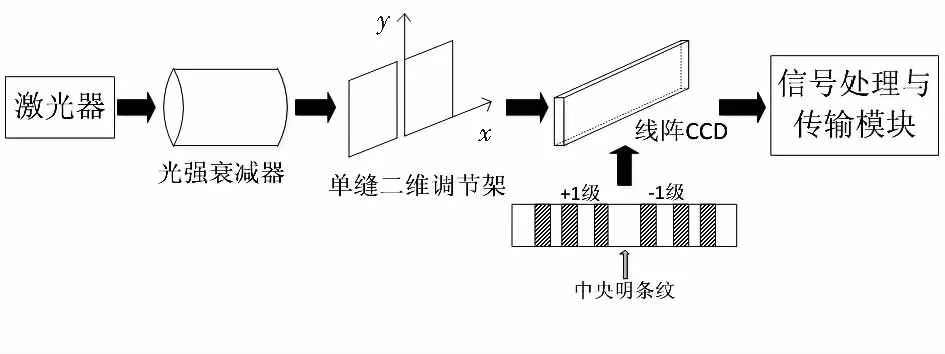

系統結構如圖1所示,當衍射光垂直投射在線陣CCD上,在驅動信號的作用下CCD將光信號轉換為模擬電信號,模擬電信號先通過一個低通濾波器進行濾波,再送入模/數轉換器中進行模擬信號處理,處理后的模擬信號轉換為數字信號,并傳送至FPGA內部異步FIFO存儲器中緩存起來,然后由FPGA內部并口轉串口模塊將數據串行輸出,最后數據通過串口上傳至PC機,完成數據傳輸[3],如圖1系統結構框圖所示。

圖1 系統結構框圖Fig 1 Block diagram of system structure

2 系統硬件模塊

2.1 圖像采集單元

系統選用東芝公司的TCD1209D作為感光元件,這種CCD靈敏度較高、暗信號電壓較小、動態范圍較大,非常適合用于尺寸測量。它有2 048個有效像元,像元尺寸為14 μm×14 μm,相鄰2個光敏單元的中心距為14 μm。該CCD工作需要6路驅動時序,由FPGA產生,包括移位脈沖φ1,φ2,信號輸出脈沖φ2B,轉移脈沖SH,復位脈沖RS,箝位脈沖CP。

2.2 低通濾波部分

圖2 Sallen-key型低通濾波器電路圖Fig 2 Circuit diagram of Sallen-key low-pass filter

2.3 A/D轉換部分

CCD模擬信號經過低通濾波電路后,傳送至A/D轉換器中。選用AD公司生產的AD9945,這是一種適合本系統CCD應用的完整模擬信號處理器。該芯片最高采樣頻率為40 MHz,而本系統CCD信號頻率為1 MHz,完全能滿足本系統設計需要。同時它的信號鏈中包含相關雙采樣器(correlated double sample,CDS),可以減小各種系統噪聲,包括復位噪聲、熱噪聲、1/f噪聲等。CDS原理[4,5]就是用2個采樣保持脈沖,其中一個為預采樣脈沖(SHP),另一個為數據采樣脈沖(SHD),對CCD輸出信號中的每個像素進行先后2次采樣。當預采樣脈沖有效時,先對每個像素中的浮置柵電平部分進行一次預采樣并保持;當數據采樣脈沖有效時,再對信號采樣并保持。2次采樣差即為真正的CCD視頻信號,工作原理如圖3所示。

圖3 相關雙采樣工作原理Fig 3 Working principle of CDS

同時AD 9945通過一個10位的串行數字接口編程設置CCD信號的增益,使設計簡化。增益范圍為6~40 dB,增益調整的公式為VGA Gain(dB)=(VGA Code×0.035 dB)+5.3 dB。最后,CCD信號通過一個12位的A/D轉換器輸出,將模擬信號轉換為12 bit數字信號傳輸至FPGA內建的FIFO中。

2.4 數字信號傳輸部分

為了使A/D轉換出來的數字信號能正確傳送至上位機,本系統在FPGA內部建立異步FIFO來緩存數據。FIFO的存儲介質為一塊雙端口RAM,由于經過A/D轉換后的數字信號為12位,所以,異步FIFO設計成12位位寬。同時由于TCD1209D有2 048個像元,將RAM的深度設為2 k。CCD信號頻率為1 MHz,將寫時鐘頻率設為1 MHz。串口傳輸速率設為9 600波特率,則FIFO讀時鐘頻率應大于9 600/12 Hz,所以,將讀時鐘頻率也設置為1 MHz。當寫時鐘上升沿到來時,判斷寫信號是否有效,寫入一個12位數據到RAM中;當讀時鐘脈沖上升沿到來時,判斷讀信號是否有效,若有效則從RAM中把一個12位數據讀出來。

數據從FIFO存儲器讀出后,進入并口轉串口模塊,12位并行數據以串行方式傳遞給串口,再上傳至上位機軟件,顯示出衍射波形。

3 系統數據采集過程

電路板上電開始后,先讓FPGA進行初始化,其內部建立的異步FIFO進行復位。然后系統延時1 ms,因為AD9945上電需要1 ms來復位。當PC機向串口發送讀取數據的命令后,FPGA開始產生CCD和AD驅動信號,A/D轉換器不斷將轉換后的數據送到輸出口D0~D11。由于AD采樣后轉換輸出的數字信號要延時10個轉換周期,為了能準確地寫入FIFO,寫信號要延時10個A/D轉換周期,即在A/D轉換信號的第11個周期時為寫信號的第一個周期,這樣才能將數據寫入到FIFO中[6]。

當FIFO寫入2 048個數據時,它會產生滿信號,此時FIFO停止寫數據,等待下一次FPGA寫使能信號來時才開始寫數據。當FIFO數據讀完時,它會產生空信號,此時發送寫使能信號,進行下一幀數據傳輸。并轉串模塊將FIFO中讀取出來的數據通過串口發送到PC機,完成一次數據傳輸。數據傳送完一幀后,檢驗串口是否有PC機讀取數據信號,進入下一次循環狀態,如圖4所示。

圖4 數據采集流程圖Fig 4 Flow chart of data collection

4 系統測試與分析

本系統通過單縫衍射實驗來驗證系統的精確度和穩定性。衍射現象分為兩大類:夫瑯禾費衍射和菲涅耳衍射,本系統僅以夫瑯禾費衍射 (即平行光衍射)來驗證系統性能,衍射光強分布測試光路搭建如圖5所示。用He-Ne激光器做光源,激光經過光強衰減器后,垂直照射在狹縫上,產生的衍射光垂直投射在線陣CCD上,經過后續信號處理與傳輸模塊將數據上傳至PC機上顯示。調節光路時需注意:狹縫的寬度、狹縫距離CCD的距離、衍射光斑的清晰度和對稱性、衍射光斑和線陣CCD的平行度,這些因素都會對CCD接收衍射光強產生直接影響[7]。

圖5 夫瑯禾費衍射光強分布測試光路Fig 5 Testing optical path of light intensity distribution of Fraunhofer diffraction

平行光照射在寬度為b的狹縫上發生衍射現象,衍射花樣為明暗相間的條紋,中央是最亮最寬的明條紋,兩側是對稱的明暗相間的條紋,寬度逐漸減小。衍射光平行照射在線陣CCD上,其光強分布規律為

I=I0sin2μ/μ2,μ=(πbsinφ)/λ,

(1)

式中b為狹縫寬度,λ為入射光波長,φ為衍射角。當-λ≤bsinφ≤λ時為中央明紋,光強I0為最大值;當bsinφ=±(k+1/2)λ,k=1,2,3,…為各次級亮紋位置。代入式(1)可知,理論上0級、±1級光強比為1︰0.045 08。

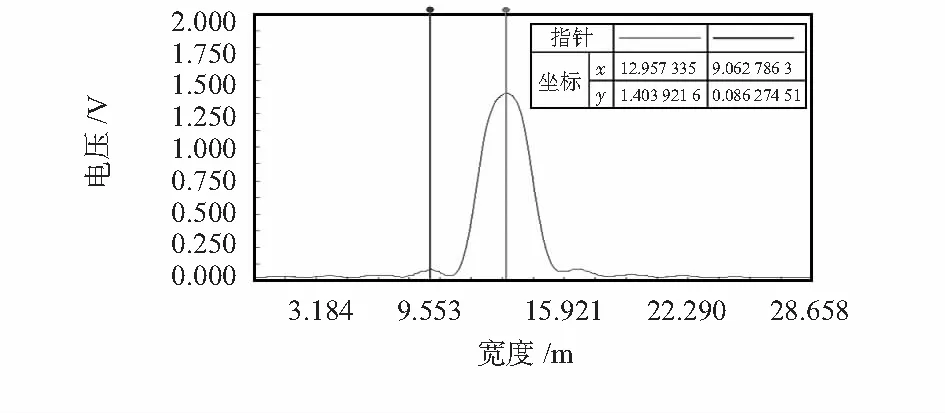

圖6為單縫衍射實驗中測得的衍射光強分布,圖中橫坐標為CCD像元坐標,縱坐標為每個相元輸出的電壓值。從圖上可以清晰地看到±4級衍射光,暗電流加雜散光引起的噪聲電壓大小為0.02 V。通過計算得出0級與±1級光強比為0.045 45,與理論值的誤差為0.82 %,說明本系統噪聲抑制的較好,精度較高。

圖6 單縫衍射光強分布實驗數據Fig 6 Experimental data of light intensity distribution of single slit diffraction

5 結 論

基于FPGA設計的CCD測量系統,取代了以往設計中基于CPLD和單片機的測量系統,利用FPGA的多種優勢,提高了系統的集成度和可靠性。同時本系統對噪聲進行了較好的處理,大大提高了系統精度。本系統還可以拓展到其它應用中,例如:無接觸測量尺寸、位移測量等,當換用信號頻率更高的CCD時,還可以將本系統運用到無接觸振動測量中。

[1] 王慶有.CCD應用技術[M].天津:天津大學出版社,2000:30-45.

[2] 王 鑫,陳 驥,曹久大,等.線陣CCD高速數據采集與實時處理系統[J].光電子· 激光,2008,19(2):174-177.

[3] 浦國斌,張 濤,范志永.基于USB 2.0接口的CCD數據采集系統設計[J].微計算機信息,2008,24(12-1):74-75.

[4] 程鵬飛,顧明劍,王模昌.CCD視頻信號處理電路設計[J].科學技術與工程,2006,24(6): 3847-3850.

[5] 王華偉,劉 波,曹劍中.CCD信號處理電路設計研究[J].科學技術與工程,2007,16(7):4153-4156.

[6] 陶純匡,尹 剛,汪 濤.基于ARM和FPGA的CCD低噪聲測量系統的設計[J].電子測量技術,2010,33(3):64-71.

[7] 潘華錦,張 麗,馬春庭.利用CCD測量單縫衍射的光強分布[J].計量與測試技術,2009,36(3):57-58.

Design of low-noise CCD measuring system based on FPGA*

XIA Zhen-zhen, WANG Tao, ZHANG Jun

(School of Physics,Chongqing University,Chongqing 401331,China)

In order to improve the precision and integration of one dimension CCD non-contact measurement system, a system based on FPGA device is designed.Through low pass filtering and correlated double sampling technology process,CCD signal noise is reduced.After analog signal is converted to 12 bit digital signal,it is transfered to FIFO memory embedded into FPGA,which enhances integration and stability of system.Driving schedule generator is described with Verilog HDL.Besides,a single slit Fraunhofer diffraction experiment is conducted to validate reliability and precision of the system,experiment demonstrates that the system is reliable and the precision reaches 0.82 %.

CCD;FPGA;low pass filtering;correlated double sampling

2013—10—08

中央高校基本科研業務費資助項目(0233005205010)

TP 216

A

1000—9787(2014)04—0087—03

夏真珍(1988-),女,安徽銅陵人,碩士研究生,主要研究方向為FPGA嵌入式開發。