基于PXA320嵌入式手持終端電源管理的設計*

李 頎,胡海強,翟 佳

(陜西科技大學電氣與信息工程學院,西安710021)

隨著全球節(jié)能需求的不斷提高和各種工業(yè)現(xiàn)場對嵌入式手持設備功能要求不斷提高,使得對嵌入式手持終端電源管理[1-2]的要求也在不斷地提高。電源管理是將電源有效分配給系統(tǒng)的不同組件。優(yōu)秀的電源管理能夠將電池壽命延長兩到三倍。開發(fā)設計一款具有性能穩(wěn)定且低功耗[3-4]的嵌入式手持設備顯得越來越重要。針對這一問題,本文介紹了基于PXA320嵌入式手持終端電源管理系統(tǒng)的設計方案。

1 PXA320電源管理

1.1 手持終端核心處理器的芯片介紹

Marvell公司的PXA320為32 bit的兼容 ARM V5TE構架,其性能高于ARM11,其最高運行頻率可達624 MHz~802 MHz并且實現(xiàn)軟件完全兼容。其提供了豐富的硬件接口資源支持多種Flash包括Nand和Nor設備,采用16 bit DDR隨機存儲器最高頻率可達260 MHz。內(nèi)部64 bit高速總線交換和多通道技術使得處理速度更快。26 MHz的MMC/SD接口3個、3.6 Mbit/s的UART接口3個以及26 MHz的SSP接口4個方便連接各種外部設備。專用LCD接口和攝像頭接口支持多種類型的LCD和Camera設備。多達128個GPIO接口可靈活使用等。Intel的SpeedStep技術可以通過軟件和硬件動態(tài)調整工作電壓與工作頻率,有效提高電池在使用視頻、音頻播放功能以及其他各種應用時的續(xù)航能力。同時該系列的處理器與PXA27X系列相比,新元件減少的功耗多達60%。

1.2 PXA320電源管理方式

PXA320處理器總共提供了6種電源模式,分別為:正常模式、閑置、深度閑置、待機、睡眠和深度睡眠。其中后6種模式歸結為空閑電源模式。為降低系統(tǒng)功耗,PXA320要最多時間地處于空閑電源模式。這樣外圍設備例如:Flash、SDRAM等也會隨之進入空閑模式。

進入空閑狀態(tài),主要是通過編程實現(xiàn)。通過向PWRMODE[M]寄存器寫入0b001可進入閑置模式。該模式下,除了CPU時鐘停止工作,其他外部和系統(tǒng)都正常工作。通過向待機配置寄存器Standby Configuration Register(PSTR)賦值并配置存儲器控制器可進入待機模式。該模式下,所有處理器行為停止,對CPU中斷進行監(jiān)控。通過對睡眠模式配置寄存器進行設定,使睡眠和深度睡眠狀態(tài)DC-DC轉換器開始工作,停止LCD控制器。在該模式下,所有處理器行為停止,對CPU核的中斷請求忽略。除了RTC處理器的內(nèi)外部時鐘停止。

1.3 系統(tǒng)正常模式下供電需求

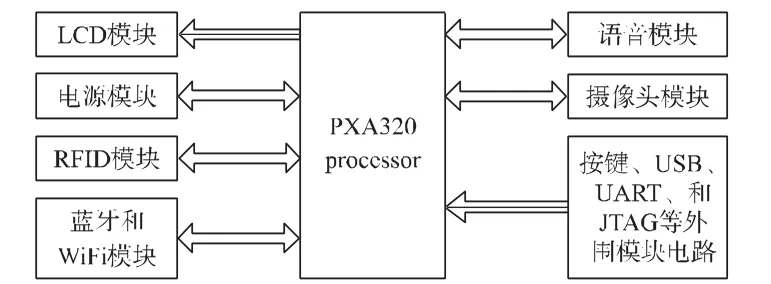

在正常模式下,PXA320及其外圍部件都需要供電。該手持終端基于高性能PXA320處理器的各種接口實現(xiàn)了強大的擴展性。手持終端的系統(tǒng)硬件框圖如圖1所示。其中主處理器PXA320是實現(xiàn)手持終端的核心芯片。外部電源通過智能電源管理芯片LP3972為系統(tǒng)提供電源。NANDFLASH選用三星公司的K9F1G08GUOM,存儲容量為1G,總線結構為1 G×8 bit。DDR SDRAM選用2片型號為K4X1G163PC,容量大小為64 M×16 bit。外圍模塊是由RFID模塊、藍牙和WiFi模塊、語音模塊、攝像頭模塊和LCD模塊等組成。

CC1101的供電電壓為1.8 V~3.6 V;藍牙BTS4025芯片所需的接口電壓和工作模式電壓為3.0 V。WiFi芯片AR6002GZ的電源有四路:內(nèi)核處理器1.2 V、EEPROM電源1.8 V、接口電平3.0 V和電池電源。WM9713L芯片運行的電壓范圍為1.8 V~3.6 V。

圖1 系統(tǒng)硬件框圖

2 電源管理硬件的實現(xiàn)

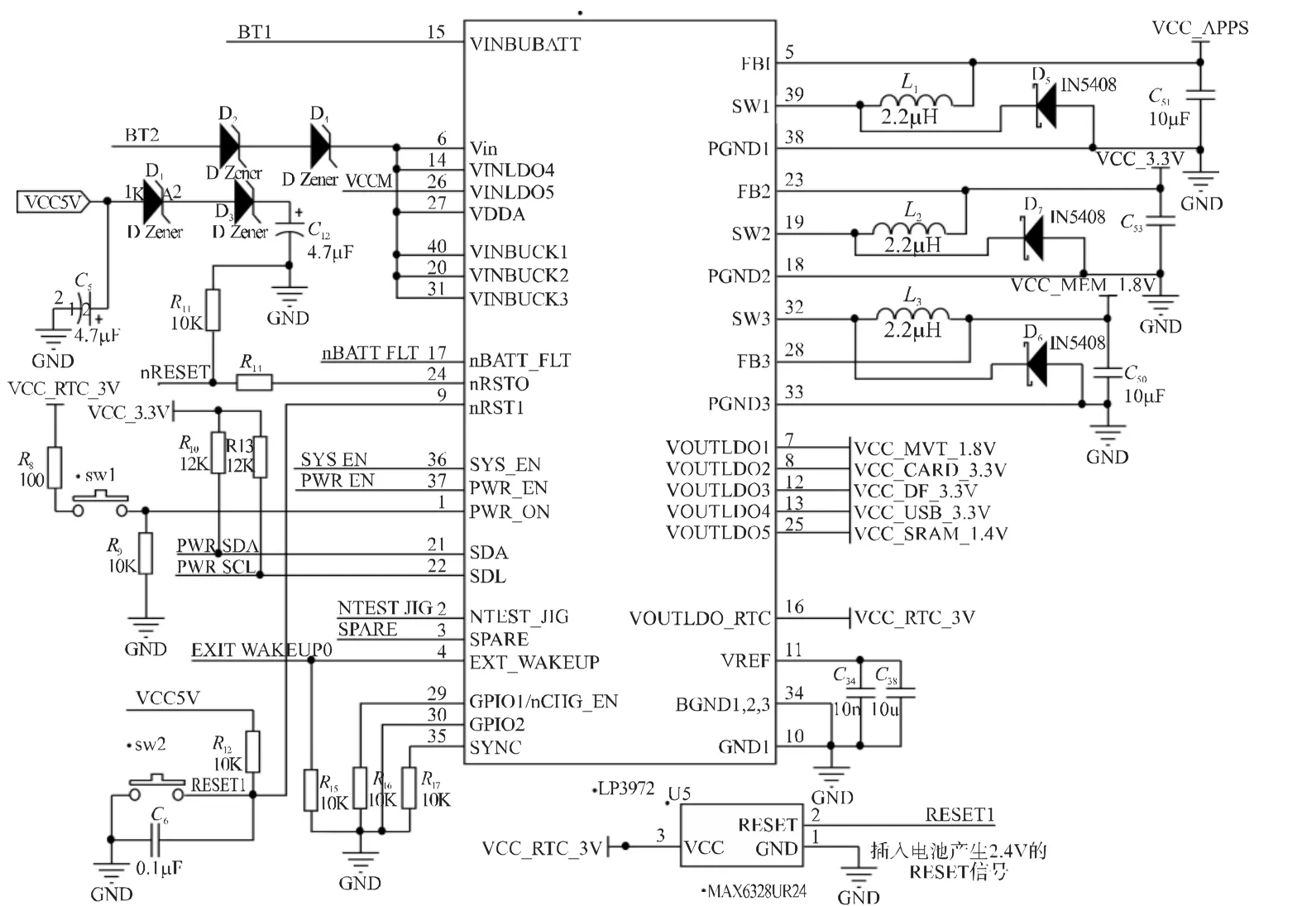

LP3972是一個多功能可編程電源管理芯片。它提供了6路的LDO輸出和3路DC-DC輸出電源。其中2路動態(tài)可調的DC-DC提供處理器內(nèi)核與內(nèi)部靜態(tài)存儲器,另2路DC-DC提供IO接口、外部存儲器和其他外部設備。除電源轉換功能外,芯片還提供了I2C接口可軟件控制各路電源輸出的電平以及開關狀態(tài)、電池電壓的低電檢測功能和復位信號輸出功能。DC-DC開關電源降壓電路相比較于線性LDO電源,具有更高的效率,可以做到更大的電流。DCDC1提供PXA320處理器的核心電壓。DC-DC2輸出電壓為3.3 V,其驅動電流為1 600 mA,主要用于大部分外圍設備和與之相對應的接口電壓的匹配供電。DC-DC3主要用于為外部存儲器供電,包括內(nèi)存DDR和閃存FLASH。PXA320處理器可以通過IIC總線并結合Linux操作系統(tǒng)可以對其進行控制,實現(xiàn)動態(tài)電壓頻率調節(jié)、休眠喚醒、各模塊電壓的控制和調節(jié)RFID模塊的關閉打開等功能。系統(tǒng)供電電源硬件電路圖如圖2所示。

圖2 系統(tǒng)供電電源硬件電路圖

3 電源管理芯片驅動軟件的實現(xiàn)

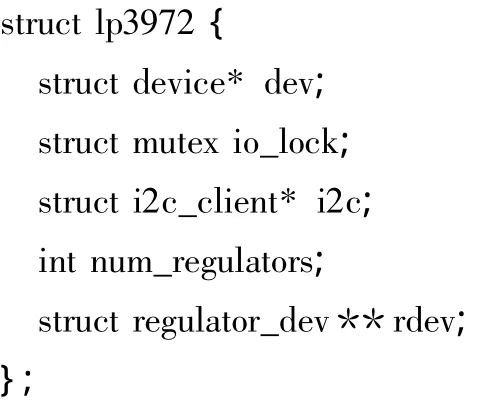

首先要定義的是平臺設備結構。該平臺結構包含與物理設備相關的信息。LP3972設備結構定義如下:

由于LP3972芯片由6個LDO和3個DC-DC輸出需要控制,在LP3972結構體內(nèi)又定義了4個結構體類型。

LP3972智能電源管理芯片是由于其與處理器通過IIC總線連接。處理器可通過該總線向LP3972發(fā)送和接收數(shù)據(jù)來實現(xiàn)對其輸出電壓值的有效控制。下面程序為在linux下PXA320處理器對LP3972芯片的讀寫操作。

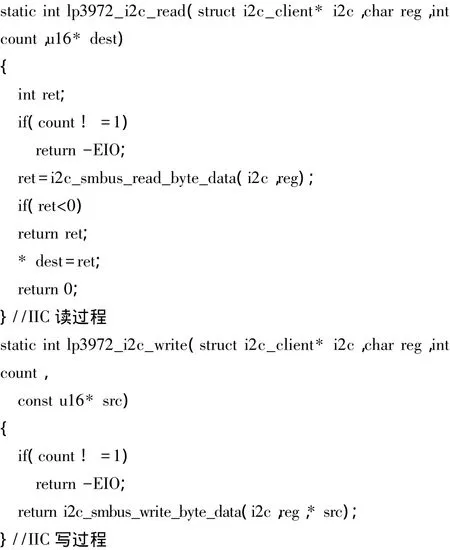

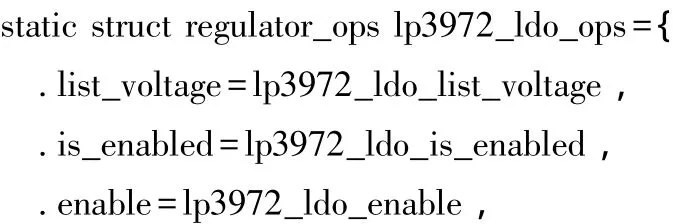

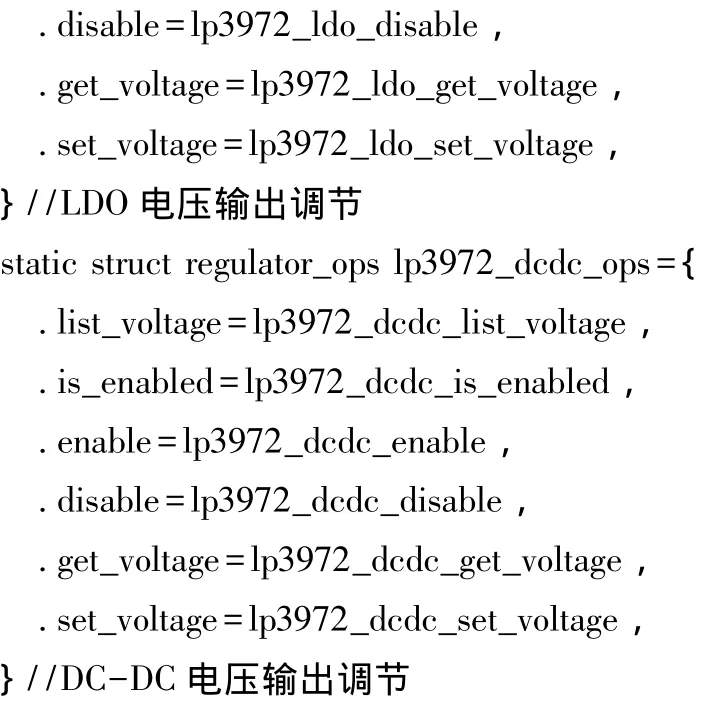

下面程序為處理器對LP3972智能電源管理芯片6路LDO和3路DC-DC輸出電壓的調節(jié)。其主要是通過使該程序中事先定義好的輸出LDO的值有效,然后通過IIC總線傳輸給LP3972,LP3972最終獲得該值。如圖3所示為電壓調節(jié)流程圖。

圖3 電壓調節(jié)流程圖

4 工作過程

為避免對處理器造成損壞,PXA320的供電必須按照特定的順序提供。PXA320的上電復位過程描述如下:

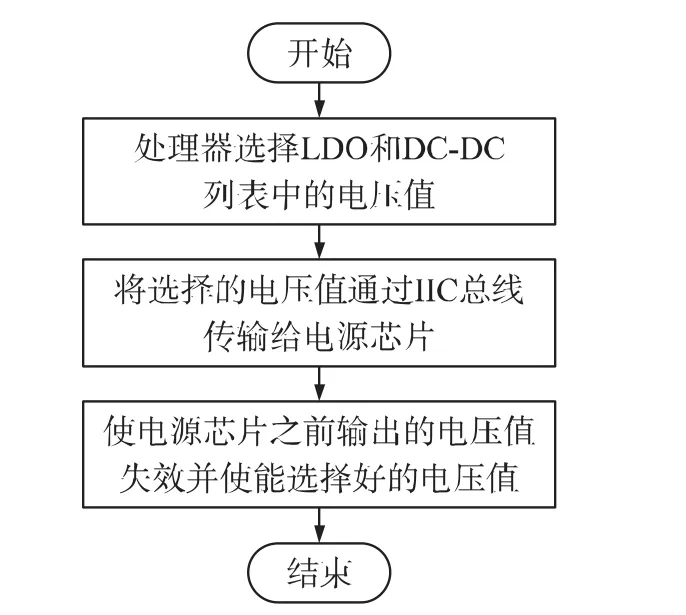

LP3972電源管理芯片向 PXA320處理器的VCC_BBATT引腳提供一個固定的電壓,并使復位信號nRESET有效。通過nRESET信號保持50 ms后無效,和在LP3972使nBATT_FAULT無效來提示PXA320處理器的電源供應正常。當SYS_EN信號有效,電源管理芯片使能高電源供應區(qū)域,處理器進入125 ms的倒計時,此時處理器的VCC_PLL、VCC_OSC13M(13MHz晶體振蕩器電壓)、VCC_BG(基準源電壓)以及VCC_MVT(內(nèi)部邏輯以及I/O控制器的電壓)首先被供應電壓,其他高電源區(qū)域的電壓隨即有效。125 ms倒計時,內(nèi)部鎖相環(huán)以及13 MHz晶振供電后,處理器開始執(zhí)行代碼。125 ms倒計時結束后,處理器置PWR_EN信號有效,使能低電源供應區(qū)域。PXA320處理器啟動后,為保持電源選通,首先應設置相應的 GPIO口輸出高電平到LP3972的POWERRACK引腳。如果等待一段時間后,POWERRACK仍為低電平,則 LP3972的 LDO和DC-DC輸出重新切斷。圖4為通過LP3972來對PXA320系統(tǒng)開關機流程圖。

圖4 系統(tǒng)開關機流程

5 結論

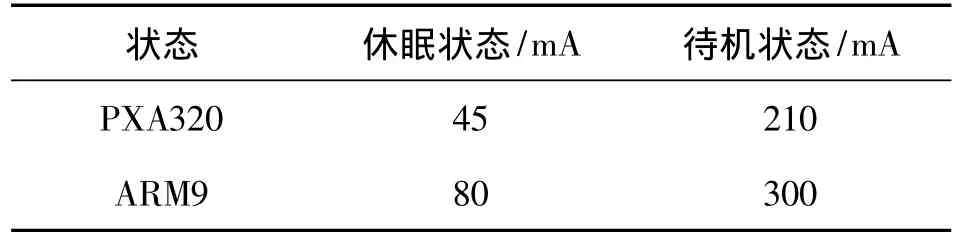

LP3972電源管理芯片在5 V輸入時,其DCDC的轉換效率最高可達到95%。本文在休眠狀態(tài)和待機狀態(tài)對該手持設備與通用ARM9手持設備進行了電流測量比較,結果如表1所示。

表1 系統(tǒng)功耗

測量結果可以看出以,對以PXA320為核心且采用LP3972電源管理芯片的手持設備進行了軟硬件設計后,手持設備的功耗降低。通過對其整體性能的測試,在實驗階段該手持終端軟硬件可以穩(wěn)定的運行。

[1]周建政,呂柏權.基于Linux嵌入式的電源管理的研究[J].儀表技術,2008,1(1):59-61.

[2]CliveW.Dynamic ManagementofEnergy Consumption in Embedded Systems[J].Information Quarterly,2003,2(3):- .

[3]陸希玉,唐昆,崔慧娟.基于嵌入式系統(tǒng)的低功耗設計[J].微計算機信息,2005(10):4-6.

[4]Daisuke M,Yutaka I.Process Oriented Power Management[C]//Proc of the 2nd International Symposium on Industrial Embedded Systems.Lisbon,Portugal:[s.n.].2007.

[5]LP3972 Power Management Unit for Advanced Application Processors[S].2008.

[6]Steve B Furber, , ,et al.Power Management in the Amulet Microprocessor[C]//IEEE Design and Test of Computers.2001.

[7]Yung-Hsiang Lu, , ,et al.Computing System-Level Power Management Policies[C]//IEEE Design and Test of Computers.2001

[8]嚴惠瓊,都思丹.新型National系列半導體電源芯片分析綜述[J].南京大學學報(自然科學),2007,1(43):35-46.

[9]李丹.嵌入式系統(tǒng)的電源特性[J].成都大學學報(自然科學版),2008(1):56-58.

[10]狄巨星,趙建光,司亞超,等.嵌入式無線安防監(jiān)控系統(tǒng)電源研究[J].電源技術,2012(7):1033-1045.