一種低功耗CMOS晶振電路設(shè)計(jì)*

彭偉娣,張文杰,謝 亮,金湘亮

(湘潭大學(xué)材料與光電物理學(xué)院,湖南湘潭411105)

隨著信息科學(xué)技術(shù)的迅猛發(fā)展,低功耗設(shè)計(jì)成為集成電路發(fā)展的趨勢。石英晶振振蕩器作為頻率標(biāo)準(zhǔn)和頻率選擇的“心臟”元件,被廣泛應(yīng)用于航天和電子技術(shù)設(shè)備中,市場對石英晶體振蕩器的小型化、低功耗等指標(biāo)要求也在不斷提高。

傳統(tǒng)的晶振電路采用的放大器是反相器并聯(lián)大電阻模型。反相器在電源電壓為P管和N管的總閾值之和、且P管和N管同時(shí)偏置在飽和區(qū)時(shí)的工作狀態(tài)最佳,只消耗較低的電流。一旦電壓超過這個值,電路工作狀態(tài)將變差,整體電路將消耗更多的電流;一旦電壓低于這個值,晶振電路將停止振蕩[1-2]。

本文致力于設(shè)計(jì)一種低功耗晶振電路,晶振內(nèi)部的反相器在電源電壓低于P管和N管的總閾值之和時(shí)也能正常工作,P管和N管同時(shí)偏置在飽和區(qū)。整體電路消耗的電流低于傳統(tǒng)晶振電路消耗的電流。

1 電路分析

1.1 傳統(tǒng)晶體振蕩電路的設(shè)計(jì)與分析

1.1.1 石英晶體的等效電路

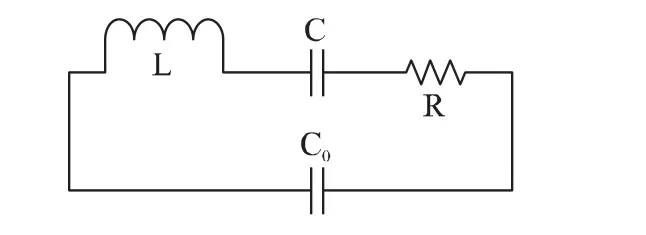

石英晶體的等效電路如圖1所示。

圖1 石英晶體的等效模型

當(dāng)?shù)刃щ娐分械腖、C、R支路產(chǎn)生串聯(lián)諧振時(shí),該支路呈阻性,等效電阻為R,諧振頻率為

當(dāng)f<fs時(shí),C0和C電抗較大,起主導(dǎo)作用。石英晶體呈容性。當(dāng)f>fs時(shí),L、C、R支路呈感性,將與C0產(chǎn)生并聯(lián)諧振,石英晶體呈純阻性,諧振頻率

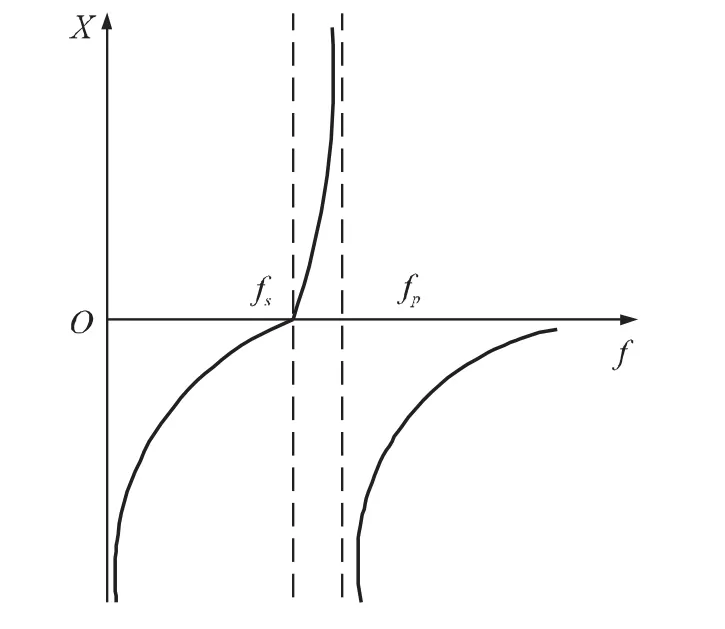

當(dāng)f>fp時(shí),電抗主要決定于C0。石英晶體電抗的頻率如圖2所示,只有在fs<f<fp的情況下,石英晶體才呈感性。

圖2 石英晶體的電抗頻率特性

1.1.2 傳統(tǒng)Pierce CMOS晶振電路

傳統(tǒng)的Pierce CMOS晶振電路如圖3所示,在反相器的輸入、輸出端并聯(lián)反饋電阻。反饋電阻將反相器鉗制在放大區(qū),此時(shí)的反相器等效為放大器,同時(shí)引進(jìn)直流偏置。將石英晶體作為高Q值諧振回路元件接入正反饋電路中,組成晶振電路。Pierce CMOS晶振電路采用石英晶體決定晶振電路的頻率。因?yàn)槭⒕w的高標(biāo)準(zhǔn)性和高品質(zhì),可以使石英晶振電路獲得極高的頻率穩(wěn)定性。

圖3 Pierce CMOS晶振電路

對于選定的頻率,晶振電路必須滿足“巴克豪森”準(zhǔn)則才能起振。“巴克豪森”準(zhǔn)則表示為

當(dāng)環(huán)路總相位移為360°的整數(shù)倍,環(huán)路增益大于或等于1為晶振電路的起振條件。圖3中的等效放大器提供180°相位移,石英晶體和兩個微調(diào)電容組成反饋電路,它們提供剩下的180°相位移,滿足條件(4)。由于等效放大器的作用,振幅開始增大,但振蕩幅值的增長過程不會無止境地延續(xù)下去,因?yàn)榉糯笃鞯木€性范圍有限,隨著振幅的增大,放大器逐漸由放大區(qū)進(jìn)入飽和區(qū)或截止區(qū),工作在非線性的甲乙類狀態(tài),其增益逐漸下降。當(dāng)放大器增益下降導(dǎo)致環(huán)路增益下降到1時(shí),振幅的增長過程停止,振蕩器達(dá)到平衡狀態(tài),即進(jìn)入等幅振蕩狀態(tài)。

對于Pierce CMOS晶振電路,反相器中P管和N管的跨導(dǎo)gm之和必須滿足在一定的范圍內(nèi),晶振電路才能起振。可以根據(jù)晶體等效模型參數(shù)設(shè)計(jì)P管和N管的寬長比,使gm值在相應(yīng)的起振范圍之內(nèi)[3]。

2 低功耗晶振電路設(shè)計(jì)

2.1 加串聯(lián)電容的晶振電路

如圖4所示,新型晶振電路在傳統(tǒng)Pierce CMOS晶振電路中添加電路1、電阻R2和串聯(lián)電容C0。

圖4 加串聯(lián)電容的晶振電路

傳統(tǒng)的反相器,P管的柵端與N管的柵端相連,兩者的柵端電壓相等。反相器在電源電壓等于P管和N管的閾值電壓之和、P管和N管同時(shí)偏置在飽和區(qū)時(shí)的工作狀態(tài)最佳,且消耗的電流較小。P管和N管的柵端加入串聯(lián)電容C0后,P管和N管的柵端電壓一直相等的條件則不存在,兩管的偏置相對獨(dú)立。N管的漏端和柵端之間連接大電阻,相當(dāng)于二極管連接,所以N管被一個N管的閾值電壓偏置。如果此時(shí)P管恰好被一個P管的閾值電壓偏置,則P管和N管可以同時(shí)偏置在飽和區(qū),同時(shí)電源電壓小于P管和N管的閾值電壓之和。

電路1為一個常見的基準(zhǔn)電路,相當(dāng)于電流鏡模塊,只需要較小的開啟電流。I1、I2分別為P1管和P2管的漏電流。從本質(zhì)而言,I1被“自舉”到I2,從而確定I1。因?yàn)槊總€二極管方式連接的器件都是由一個電流源驅(qū)動的,所以相對來說,I1和I2與VDD無關(guān)。所以VDD在2.7 V~5 V間變化時(shí),I1和I2變化范圍不大,在設(shè)計(jì)低功耗晶振電路時(shí),設(shè)計(jì)相應(yīng)的參數(shù),保證電路1部分消耗的電流最小,提供穩(wěn)定的偏壓偏置后續(xù)電路。

N2管的漏電流I2將P2管的源漏電壓鉗制為一個P管的閾值電壓。P2管的柵端電壓通過大電阻R2連接P3管的柵端,所以P3管也被一個P管的閾值電壓偏置。同時(shí)N3管由于R3的作用,被一個N管的閾值電壓鉗制在飽和區(qū)。在VDD的值小于P管、N管的閾值電壓之和時(shí),P3管和N3管都能鉗制在飽和區(qū),且消耗最低的電流。

2.2 低功耗晶振電路設(shè)計(jì)

低功耗晶振電路在前述電路模塊中加入緩沖模塊和濾波電容保證其穩(wěn)定性和高效性,設(shè)計(jì)電路如圖5所示。在鏡像電路模塊和晶振模塊之間用緩沖器模塊連接,P4和N4組成反相緩沖器,由鏡像電流開啟。C3電容有濾波的作用,防止晶振起振后P4管柵端電壓的快速變化對P3管的影響。R4和R5分別連接P3管和N3管的源端,這些電阻起到限制漏電流的作用,在一定程度降低晶振電路的功耗。P4的源端連接P3的源端,所以P3管的偏置電壓值也為一個P管的閾值電壓,同時(shí)R3偏置N3管,N3管的偏置電壓值等于N管的閾值電壓。所以P3管和N3管都被偏置在飽和區(qū)。設(shè)置合適的R4和R5,在減小漏電流的同時(shí)使P3管的源端和N3管源端之間的電壓小于P管和N管的閾值之和,使整體電路的功耗降低。

圖5 低功耗晶振電路

設(shè)置合理的P3管和N3管的寬長比,使其的gm值之和在起振范圍之內(nèi)。在仿真此低功耗晶振電路時(shí),需要提供一個外界的干擾作用才能起振。一般將高電源以上電的形式實(shí)現(xiàn),或者在組成晶振電路的電感模型中加入初始電流。

3 版圖

低功耗晶振電路的版圖如圖6所示,為了防止靜電對芯片造成傷害,在高電源、低電源、輸入、輸出四個端口分別加上相應(yīng)的ESD保護(hù)電路。

圖6 晶振電路版圖

4 仿真結(jié)果

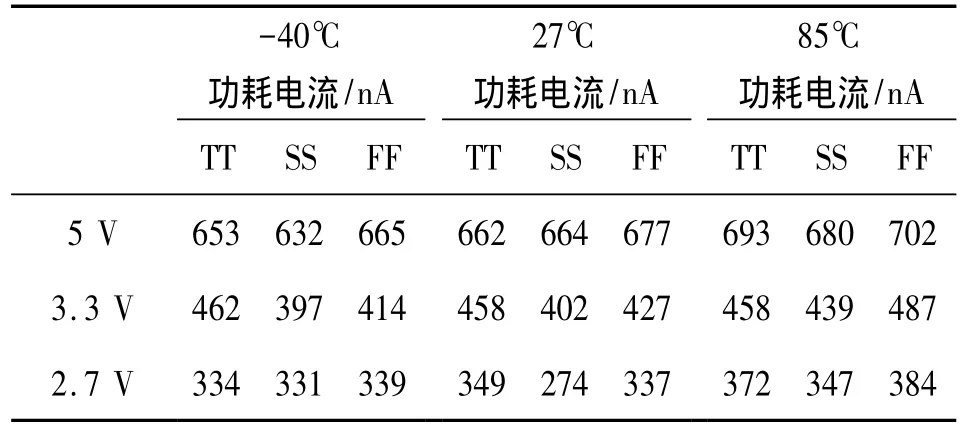

以晶振頻率為32.768 kHz的晶振電路為例,整體功耗如表1。在VDD在2.7 V~5 V之間,晶振電路能正常工作,而且消耗的功耗電流低于750 nA。

表1 晶振電路功耗電流

在高電源VDD為2.7 V、常溫、TT的情況下,低功耗晶振電路的仿真曲線如圖7所示。圖7中上欄曲線表示高電源VDD的電流幅度變化曲線,下欄曲線表示晶振電路輸出端口XTO的輸出波形曲線。

由圖7可知,晶振電路起振時(shí)間為1 s左右,高電源VDD的電流幅度最大值不超過1 μA。

圖7 晶振電路的仿真波形

5 結(jié)論

本文提出的低功耗晶振電路,在電源電壓在2.7 V~5 V之間都能夠起振,而且整體功耗電流小于750 nA。低功耗晶振電路可提高產(chǎn)品性能、降低使用成本、提高市場競爭力,所以低功耗晶振的電路提出和研究具有較高的實(shí)用價(jià)值。

[1]Werner Thommen.An Improved Low Power Crystal Oscillator[C]//Proc ESSCIRC’99,1999,146-149.

[2]Daniel Aebischer,Henri J Oguey,Vincent R von Kaenel.A 2.1 MHz Crystal Oscillator Time Base with a Current Consumption under 500 nA[J].IEEE J Solid-State Circuits,1997,32:999-1005.

[3]Andreas Rusznyak.Start-up Time of Cmos Oscillators[J].IEEE Transactions on Circuits and Systems,1987,cas-34(3):- .

[4]Vittoz E,F(xiàn)ellrath J.CMOS Analog Circuits Based on Weak Inversion Operation[J].IEEE J Solid-State Circuits,1977,sc-12:224-231.

[5]Vittoz E,Degrauwe M,Bitz S.High-Performance Crystal Oscillator Circuits:Theory and Applications[J].IEEE J Solid-State Circuits,1988,sc-23:774-783.

[6]Eric Vittoz.Low-Power Crystal and Mems Oscillators[M].Springer,2010.

[7]曾健平,王閬,何先良.石英晶體振蕩器的集成化設(shè)計(jì)[J].微電子學(xué)與計(jì)算機(jī),2009,26(2):30-32.

[8]趙聲衡.晶體振蕩器[M].科學(xué)出版社,2008.

[9]趙旭昊,安凌凌,孟令琴.0.18 μm 12 GHz CMOS八分頻電路設(shè)計(jì)[J].現(xiàn)代雷達(dá),2007,29(8):109-111.

[10]Jankovic M,Brannon A,Breitbarth J,et al.Design Method for Low-Power,Low Phase Noise Voltage-Controlled Oscillators[J].Microwave Integrated Circuit Conference,2007:199-202.

[11]Wan Wengang,Zheng Wen-qiang,Ye Lin.Development of Minitype Low-Power Consumption Quartz Crystal Oscillators[J].Piezoelectricity,Acoustic Waves,and Device Applications(SPAWDA).2009:121.

[12]ElBarkouky M,Wambacq P,Rolain Y.A Low-Power 6.3 GHz FBAR Overtone-Based Oscillator in 90 nm CMOS Technology[C]//Microelectronics and Electronics Conference,2007:61-64.