25 MHz高速抗輻照存儲器的驗證方法設計

鄧玉良,羅春華,李洛宇,劉云龍

(深圳市國微電子有限公司,廣東深圳518000)

隨著集成電路特征尺寸的減小和電路對高速、大帶寬和低電壓的需求增加,電流型電路逐步受到廣泛關注。由于電流型比較器的低電壓、高速及與數字CMOS集成電路工藝兼容等特點,目前已廣泛應用在存儲器、模數轉換器、濾波器和振蕩器等系統。

常見電流比較器有以下兩種:源跟隨型電流比較器[1],由于有一段死區使得輸入阻抗很大,難以工作在高速系統中;電阻負反饋型電流比較器[2],由于負反饋降低了輸入和輸出阻抗,使得后級放大器很難判斷,而且隨工藝、電壓、溫度(PVT)變化時性能差別很大。因此這兩種電流比較器難以在應用于PROM存儲器。

由于需研制的抗輻照PROM存儲器速度較快,因此在研制過程中采用了本文提出的電流型比較器。由于PROM存儲單元通過的電流小,因此要求該電流型比較器輸入阻抗較小;由于PROM存儲器中采用了多個電流型比較器,因此需要對這些電流型比較器之間進行較好的匹配;同時因為抗輻照PROM存儲器工作環境復雜,因此要求該比較器在工藝、電壓、溫度(PVT)變化時保持良好的一致性。綜上所述,經過巧妙設計,本文提出的電流型比較器達到了上述要求,使得抗輻照PROM存儲器能夠穩定工作在25 MHz頻率下,同時抗輻照測試結果表明,該比較器也有良好的抗輻照能力。

本文主要針對存儲器在高速及抗輻照方面進行設計,為該類型器件在航空航天系統中應用提供了保障,同時為高速抗輻照芯片設計提供參考。

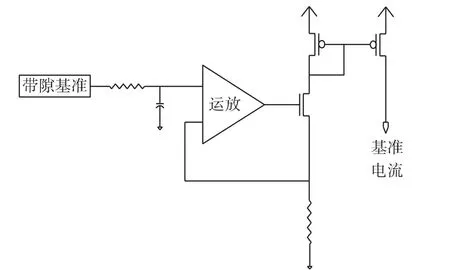

1 基準電流源電路結構

本文所采用電流源為圖1所示,為了實現高精度電流基準,將帶隙電壓經過反饋加載在電阻上生成基準電流[3-8]。由于本文所采用的電流同時作為偏置電流和閾值電流,需要仔細設計基準電流。

相對于存儲器常用的普通基準電流,本文中的基準電流更加穩定,隨電源溫度變化非常小,數字噪聲影響減小,系統更加穩定可靠。所采用的電阻溫度特性和電壓特性都比較好,但絕對值偏差較大;通過查找相應流片模式下SMIC 0.18 μm工藝的PCM參數,能夠得到很好的電阻阻值分布。經過仿真驗證,基準電流相對溫度變化小于100×10-6/℃,電源電壓引起基準電流變化小于100×10-6/V,能夠滿足工程應用。

圖1 基準電流結構

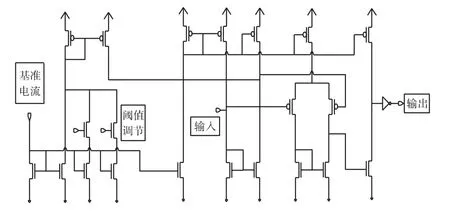

2 比較器電路結構

比較器主要由3部分組成,如圖2所示。關鍵電路在于比較器輸入端和參考端形成的電流鏡,其思路主要為實現低輸入阻抗及較高輸出阻抗[3-7]。由于比較器輸出端有較大負載,因此改為普通電流鏡,這樣能夠使偏置電流迅速地為比較器輸入端充電;同時保持MOS管匹配和增加L值,減小失配和噪聲帶來的影響,詳細分析參考第3部分。

圖2 比較器電路結構

第1部分為電流閾值調節,通過兩個配置信號調節加入到電流比較器參考端的上拉電流。第2部分為電流鏡,檢測參考電流和輸入電流差Δi,并通過電流鏡的輸出電阻ro轉換成電壓Δv,即v=Δro·(Iref-Iin)。第3部分為電壓放大,由一個兩級放大器組成,由于不存在反饋,不需要頻率補償,Vout=Δv·Av=ro·(Iref-Iin)·Av。調節適當的 MOS 管尺寸,使ro和Av保持足夠大,就能夠正確讀取很小的輸入電流;同時應該考慮比較器速度,使各節點的寄生電阻電容盡量小。比較器整體仿真閾值,最大閾值范圍 11 μA ~14 μA,其最小閾值范圍3 μA ~4 μA,能夠滿足應用。

3 整體電路工作原理

整體電路示意圖如圖3所示,除去上述電流基準及比較器外,還加入了清零信號及存儲單元。

圖3 整體電路原理

存儲單元 存儲單元的編程前特性與電容類似,等效電阻大于 1 MΩ,即等效輸入電流小于1 μA。存儲單元的編程后特性與電阻類似,存儲單元編程后的電阻范圍為50 kΩ~250 kΩ,即輸入電流大于 10 μA。

讀取功能 在本文中比較器的功能是如何區分上述的1 μA和10 μA,并且保證在溫度電源電壓變化的情況下能夠在規定時間正確讀取存儲數據。將比較器的閾值電流設定為5 μA左右(可調),因此比較器能夠將存儲數據正確讀取。

優化速度 比較器輸入端的電壓約為400 mV,每次讀取時都需要對其充放電,因此充放電的速度就會影響整體讀取速度。讀0時,由于通過比較器輸入端放電比較慢,所有在輸入端加入一個清零脈沖,每次讀取都產生一個清零,這樣讀取0數據就非常快;讀1時,由于此時有存儲單元的電流,及比較器輸入端的偏置電流,兩路電流同時對比較器輸入端的位線負載進行充電,因此讀1的時間也比較快。通過測試,在讀0和讀1情況下都能夠達到25 MHz。

4 單粒子效應仿真

優化抗輻照設計之前,采用100 MeV-cm2/mg單粒子能量進行單粒子效應仿真,遍歷比較器及參考電流源的各點,統計得到如表1的仿真數據。

表1 單粒子效應仿真各節恢復時間

優化抗輻照設計之前,采用100 MeV-cm2/mg單粒子能量進行單粒子效應仿真,改變敏感器件的特征尺寸,統計得到如圖4的仿真數據。

圖4 單粒子對不同尺寸MOS管仿真恢復時間

通過第3部分的整體電路讀取分析,可知比較器正常工作時一直處于讀取狀態,因此單粒子效應仿真只會產生瞬態翻轉。通過表1的仿真結果,可以得出整體電路中對單粒子效應敏感的節點;通過圖4的仿真結果,可以將敏感節點相連的器件進行尺寸調節,使單粒子效應影響降到最低。由于本文中的比較器較敏感,且電路采用的工藝尺寸較小,而采用的單粒子仿真能量太高,因此這樣的優化設計能夠將瞬態翻轉時間降為最小。

本節通過電路級單粒子效應仿真,給出比較器的單粒子效應,得出比較器相關結點受到單粒子作用時,不會出現鎖存錯誤的數據,實現了PROM存儲器的高可靠性。

5 加固設計及驗證

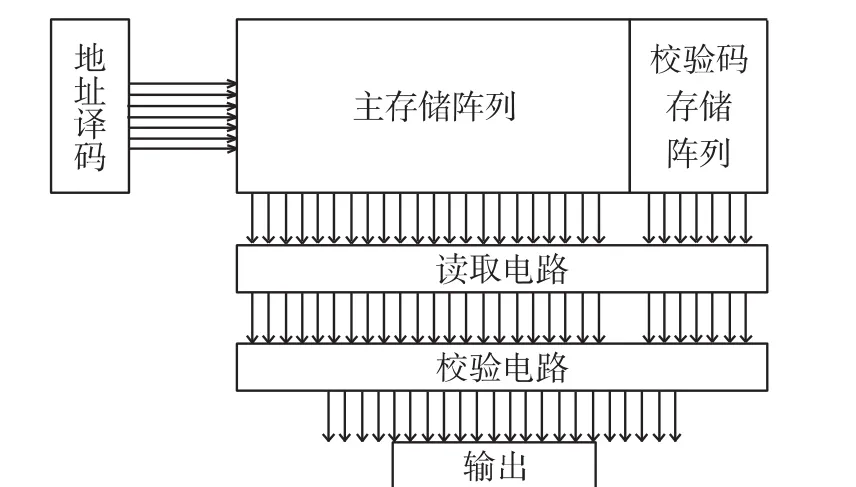

電路級加固選擇三模冗余方法,電路結構如圖5所示,并通過單粒子效應仿真驗證其已對單粒子效應免疫。

系統級加固如圖6所示,采用EDAC校驗碼,由32 bit數據data及7 bit校驗碼code,能夠達到糾一檢二的目的。

圖5 三模冗余

圖6 EDAC校驗碼

6 單粒子輻照試驗

單粒子翻轉測試系統主要由FPGA芯片、PROM芯片及FLASH芯片組成,通過高速的FPGA作為主要控制器,芯片的工作頻率為25 MHz,測試流程如圖7所示,其流程為:

圖7 試驗流程圖

(1)在實驗前,分別在抗輻照PROM和FLASH中寫入相同的數據;

(2)在試驗過程中,FPGA分別讀取PROM和FLASH中的數據,并進行比較,如果數據相同則繼續讀取下一位地址,數據不同時,則記錄一次翻轉,并通過串口將錯誤的地址及數據發送到上位機。

(3)試驗完成后,保存上位機數據,并通過軟件計算翻轉次數。

單粒子輻照試驗采用90 MeV-cm2/mg的能量,單粒子輻照總注量達到107離子數/cm2,通過上述試驗流程,未檢測到單粒子翻轉情況。

7 結論

本文以PROM存儲器為背景,介紹了比較器在系統中的作用,并提出所采用的比較器,詳細分析該比較器的優勢及原理。通過電路設計及仿真,可以優化電路的抗輻照性能。最后通過三模冗余和系統加固的設計思路,對電路進行加固設計,并通過單粒子模擬試驗證明加固的可靠性。

本文中采用的電路已經通過流片,并封裝成測試樣片,經過全部地址的測試,PROM存儲器工作頻率大于25 MHz。單粒子輻照試驗已經完成,滿足芯片的設計要求。

[1]Traff H.Novel Approach to High Speed CMOS Current Comparators[J].Electronics Letters,1992,28(3):310-312.

[2]陳盧.一種新型的高性能CMOS電流比較器電路[J].半導體學報,2001,22(3):362-365.

[3][美]Phillip E Allen,Douglas R Holberg.CMOS模擬電路設計[M].2版.馮軍,李智群,譯.電子工業出版社,2005.

[4]舒文麗,吳云峰,孫長勝,等.基于NAND Flash的海量存儲器的設計[J].電子器件,2012,35(1):107-110.

[5][美]Jacob Baker Harry R,Li David W,Boyce E.CMOS電路設計、布局與仿真[M].陳中建,譯.機械工業出版社,2006.

[6][美]畢查德.拉扎維.模擬CMOS集成電路設計[M].陳貴燦,程軍,張瑞智,等譯.西安:西安交通大學出版社,2003.

[7][美]Paul R Gray,Paul J Hurst,Stephen H Lewis,et al.模擬集成電路的分析與設計[M].張曉林,譯.高等教育出版社,2005.

[8]郭雅琳,程滔.靜態隨機存儲器低泄漏設計技術[J].電子器件,2012,35(6):764-766.