基于DSP+FPGA的影像白板控制器設計

李斌飛 安亮軍

(1.西藏職業技術學院,西藏 拉薩 850000;2.北京明航技術研究所,北京 100023)

目前市場上的影像白板產品,存在的最嚴重的問題是觸摸延遲,使用者操作白板有明顯滯后現象。造成操作延遲的主要有三個因素:攝像頭輸出延遲、數據傳輸延遲、算法延遲。 另外一個問題就是定位精度大部分區域比較精確,部分區域定位誤差偏大。造成這個問題的主要有原因有:定位精度與攝像頭分辨率、攝像頭有效焦距、程序算法密切相關。針對上述問題設計了一款新型的影像白板控制器。

1 控制器設計思路

鑒于以上調研結果,本設計著重考慮以下兩方面因素:

(1)攝像頭,通過調研基本證明白板的書寫流暢度、定位精確度、書寫平滑度都與攝像頭有著密不可分的關系。所以本系統攝像頭擬采用高性能攝像頭,鑒于目前沒有試驗依據做支撐,暫時采用普通攝像頭進行試驗,根據試驗結論隨時更換高性能攝像頭。

(2)數據預處理、傳輸,本設計充分考慮到目前市場大多影像白板都存在書寫滯后現象,所以針對數據傳輸方面設計時重點考慮以下幾個因素:

①數據量大:由于數據來源都是攝像頭數據,特點是輸出數據量大(640*480*2*60byte),如此大的數據量直接由CPU直接讀取處理顯然是不可取的。需要有一個協處理器對數據進行預處理。

②輸出速度高:普通攝像頭輸出速度為60幀/秒,輸出主時鐘48MHz如此高數據輸出,一般CPU根本無法與之對接,必須要有200MHz以上主頻CPU與之對接才能保證其數據傳輸的正確性。

③實時顯示:由于開發過程中要考慮角度校正以及數據傳輸正確與否,所以系統設計中還要有液晶顯示實現視頻數據的同步顯示。

④可靠性:如果傳輸過程中由于器件性能原因導致數據丟失或錯誤,會給后續實現坐標算法帶來嚴重問題。所以所有數據傳輸中應盡量減少傳輸路徑、避免數據流在PCB中大量搬移。

⑤PCB面積限制:由于本控制器要鑲嵌到影像白板內部,所以對整個系統尺寸有嚴格要求,系統不能過于龐大。

⑥系統成本考慮:任何產品的盈利都是以產品成本為基礎的,所以本設計也要充分考慮日后的成本因素。在保證產品性能的基礎上最大化的降低產品成本。

2 實現方案

考慮到前期調研幾個因素,本系統既要保證高速數據傳輸(60幀/秒)的可靠性,又要保證數據傳輸的實時性,還需要有視頻信號同步顯示。如果采用一般單線程(不包含數據緩存設計)數據流方式勢必會造成幀數據丟失現象(第一幀數據處理時,同時第二幀數據已經同步輸出)。所以協處理器采用ALTERA公司的高速FPGA芯片+雙SRAM + LCD的結構模式。FPGA通過內部鎖相環將主頻率倍頻至300MHz。第一幀數據在DSP中DMA傳輸、運算處理的同時FPGA同步控制預處理、緩存第二幀數據,利用FPGA并發運行的特點在FPGA內部設計三個功能模塊,實現同步高速數據采集、存儲、傳輸、實時顯示。各模塊說明如下:

數據采集與預處理模塊:本模塊是FPGA與攝像頭的接口,它通過接收攝像頭幀同步、行同步、輸出時鐘、總線接口采集攝像頭數據,舍掉前200行與后200行數據,并且去掉YUV中的色差分量,只保留640*200的一部分視頻數據的灰度信息。并同時將數據存入SRAM。

液晶顯示模塊:液晶顯示模塊采用320*240 TFT彩色LCD實現視頻同步顯示。液晶驅動程序全部由FPGA內部邏輯實現,由控制單元統一控制其運行。

控制單元:是FPGA運行的核心控制部分,承擔數據暫存、同步顯示、數據傳輸的所有控制。

3 控制原理

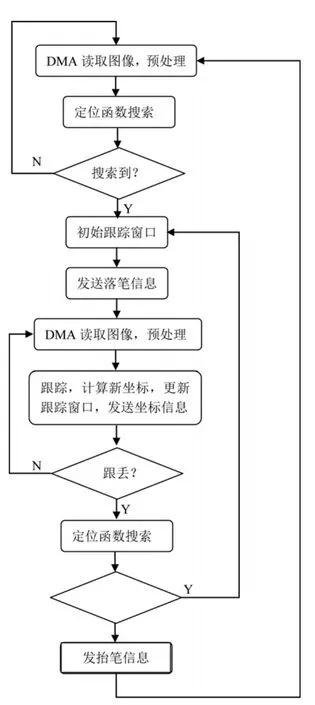

系統啟動后首先控制后續DSP進入啟動運行狀態,當DSP完成對攝像頭的參數配置后隨即啟動數據采集預處理、液晶顯示兩個模塊。首先控制數據采集模塊進行采集處理第一幀數據,并將數據寫入SRAMA,當一幀數據采集完成后,通過內部總線切換,將數據采集處理模塊將第二幀數據寫入SRAMB,同時將SRAMA數據總線切換到LCD顯示模塊進行同步顯示,顯示完成后,再次將數據總線切換至DSP,并通過中斷信號通知DSP進行DMA數據傳輸,將數據傳輸至DSP內存進行處理(圖中紅色箭頭數據流方向)。SRAMA顯示、DMA數據傳輸、SRAMB寫入完成后,控制器控制兩個SRAM再次功能切換,SRAMA寫入數據,SRAMB顯示傳輸數據(圖中藍色箭頭數據流方向),如此往復實現數據的乒乓操作。實現上述大數據量實時采集、預處理、高速緩存、高速傳輸、同步顯示功能。程序算法流程如圖1所示。

圖1 程序算法流程圖

4 系統實現

由于所有操作都在FPGA內部邏輯實現,所以也最大程度的保證了數據可靠性的同時,也進一步滿足了PCB尺寸限制的要求。考慮到本系統開發需要幾項新技術領域(CMOS攝像頭、FPGA、DSP),所以前期設計采用開發板+手工DIY的方式實現,不但大大縮短PCB設計周期,也加快開發人員熟悉開發平臺的速度。成本方面采用FPGA + 雙SRAM + DSP方式,可以根據實驗結果采用CPLD替代FPGA,小容量SRAM替代大容量SRAM,單片機(ARM)或者低性能DSP替代高性能DSP方式在不改變系統結構、低成本的前提下保證產品性能。

5 結論

目前已經完成前期數據預處理、乒乓存儲、LCD實時顯示、DMA數據傳輸等前期基本實驗,正在進行數據算法驗證進程中。基本實驗數據如下:

(1)攝像頭幀頻:60幀/秒,輸出時間:16.67ms。

(2)LCD顯示耗時(320*200):11.4ms(成熟產品中此時間可以讓步給DSP進行數據處理)。

(3)FPGA與DSP握手(中斷):1.9us(60幀情況下握手只需要1.9 * 60 =0.114ms)。

(4)DMA數據搬運耗時(10行數據):1.05ms。

(5)DSP算法耗時:未知。

(6)坐標上傳耗時:未知。

按照目前試驗結果來考慮,預期的數據預處理、乒乓存儲、LCD實時顯示、DMA數據傳輸都已經實現,由于批量產品中是不包含LCD模塊,由于DMA傳輸時間與CPU運行算法時間是同步進行,所以從第二幀數據開始預留給DSP的全部算法時間為:16.67 ms-1.9us-(105us *傳輸行數),初步試驗10行數據已可以滿足要求。所以本系統設計可以滿足預期設計要求。

[1]李山.交互式電子白板的應用及前景[J].中國教育技術裝備,2004(03).

[2]顧曉祥,劉獻忠.交互式電子白板基于內容的分形視頻壓縮[J].計算機應用研究,2010.