基于FPGA的音頻AGC設計與實現﹡

周江平, 高 俊, 屈曉旭

0 引言

語音通信中,基帶傳輸距離、麥克風等的不同都會導致進入射頻前端的音頻信號忽大忽小。為了使得激勵器能夠接收到幅度平穩的音頻信號,需要在射頻輸出之前給音頻信號做AGC處理。一般情況下,為了減小運算量,會在采樣率較低時進行AGC處理。AGC處理除了使得輸出的音頻幅度相對平穩外,還具有一定的噪音抑制能力。音頻AGC與普通AGC有所不同,音頻AGC必須跟蹤音頻信號的變化,一方面要減小不期望因素的干擾,另一方面還要較準確地反映音頻信號的幅度正常變化,因此參考幅度理論上是應該不斷變化的[1]。

隨著電子技術,計算機技術和通信技術的迅猛發展,數字信號處理技術已廣泛地深入到人們生活等各個領域。運用數字化處理技術,在現場可編程門陣列(FPGA)器件上實現音頻AGC算法,可以使得AGC控制更加精確,實現更加靈活,運行更加穩定。

1 自動增益控制基本原理

一般來說,AGC系統由可變增益放大器和反饋回路組成。可變增益放大器根據反饋回路的幅度以及閾值按照一定的算法調整增益值。一般情況下,當輸入可變增益放大器的信號幅度增大時,反饋回路控制其增益按一定關系減小;減小時,其增益則按一定關系增大[2]。這樣可以保證AGC放大后得到的輸出信號的幅度基本恒定。數字AGC的反饋部分由數字處理實現,與模擬AGC相比,降低調試難度而且增強了穩定性、收斂性和精確性[3]。

根據數字AGC中增益值調整的算法,可以將數字AGC分為固定步長AGC、可變步長AGC兩類。固定步長AGC算法簡單,實現容易,物理意義明確,但是調節時間隨著輸入變化的增大而增大,容易出現不穩定的情況;可變步長 AGC算法增益調整靈活,收斂速度較快,調節時間不會隨著輸入變化量的大小而改變,但是一般需要除法,對數運算等計算,實現時資源消耗量大。隨著微電子技術日益發展,FPGA可提供的資源量大大增加,大多采用可變步長算法。

2 音頻AGC的算法設計

1)輸出動態范圍的確定。根據實際情況,若AGC的期望值取為定值,那么輸出的信號的幅度值將無限地趨近期望值,但是會一直變化調整,這就會導致輸出端的幅度不穩定。因此,可以以期望值為中心,設計一個穩定的范圍。一旦經AGC輸出的信號處于該范圍中,認為已達到穩定的狀態,增益值將不再改變,這樣可以使輸出信號的幅度得到穩定。如果設計的這種穩定范圍足夠小,那么不會對人的聽覺效果產生影響[4]。該區間的上界稱為期望值上限,該區間的下界稱為期望值下限。研究數據表明,幅度在0.1 dB范圍內變化人爾無法察覺。設定該范圍為期望值加減0.1 dB。為了保護電路,期望值一般設為輸出信號滿偏值減0.25 dB。

2)增益調整速度的確定。在正常的語音信號中,信號幅度的大小是不停變化的。為了體現出語音信號這種幅度的正常變化,不能將所有的信號幅度都快速拉高到期望值區間,應該保持增益不變或者只變化很小的范圍。那樣才能分辨出人說話時的語調,不會產生“失真”[5]。而如果由于其它因素導致語音信號的平均幅度比較小,就需要將增益值增大,使得語音信號整體幅度增大,這樣不會對聲音信號造成失真。而相對來說,聲音信號的幅度正常變化比非正常變化要快得多。所以,音頻AGC的增益值需要跟隨這種慢的變化而忽略快變化。由于可變步長AGC算法增益調整時間可以控制,故采用可變步長算法。當增益調整時間相對語音信號正常變化時間很長時,那么增益基本不會改變,根據語音信號的特點,設定增益調整時間為4 s。如果輸出信號很大,增益需要快速減小,否則可能燒毀器件。當檢測到輸出信號大于期望值上限時,增益調整時間設為0.5 ms[6]。

AGC增益值調整算法計算公式如下:

3)輸入信號動態范圍的確定。輸入動態范圍太大,會導致大量噪聲被放大,輸出信號質量差,而輸入動態范圍太小會使得小信號被忽略,產生失真[7]。考慮實際情況,定義比輸入信號的最大值小36 dB的信號為噪聲。如果輸入一直是噪聲,應該將增益置為 0,不傳輸噪聲。而在人說話的間隙,輸入的信號也完全是噪聲,此時不能將增益值置為0,否則根據上述需要緩慢增大增益的要求,在聲音信號增大時不能有效地放大。根據噪聲信號持續的時間,可以判斷該噪聲是否為聲音信號的間隙,如果時間比較短,則認為是聲音信號的間隙。時間長短的判決門限的選取需適當,太長會使得聲音信號結束之后還會有很長一段的噪聲輸出,太短則使得誤判較嚴重,不能高質量地傳輸語音信號。時間判決門限設定為5 s比較合適。在音頻信號最小值與噪聲門限之間,留有6 dB的范圍,在此區間,噪聲對信號的幅度影響很大,因此固定增益值,即不放大噪聲,也不屏蔽信號。

4)增益大小的限制。為了避免增益過大,信號突變燒毀器件,將增益限制在一個范圍內,如果計算得到的增益大于這個范圍的最大值,增益取最大值,反之,增益取最小值。最大增益定為30 dB,最小增益定為-3 dB。

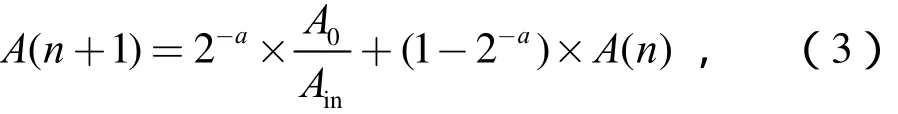

綜上所述,音頻AGC算法的流程如圖1所示。

圖1 AGC增益控制算法流程

3 音頻AGC的算法的仿真

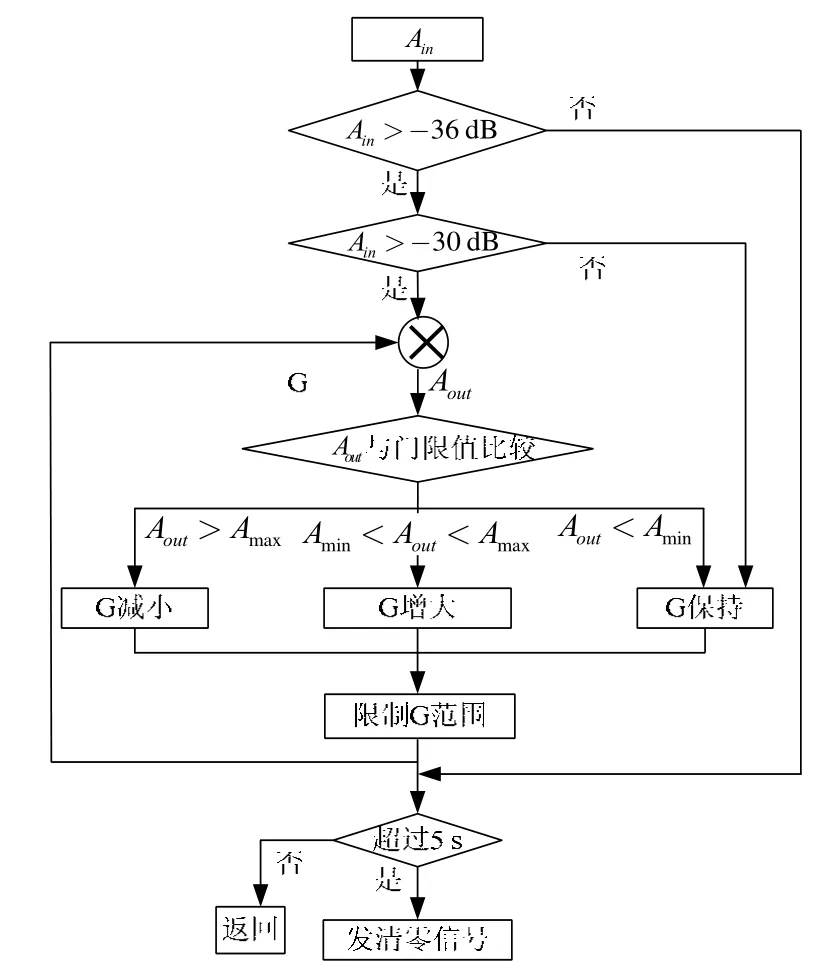

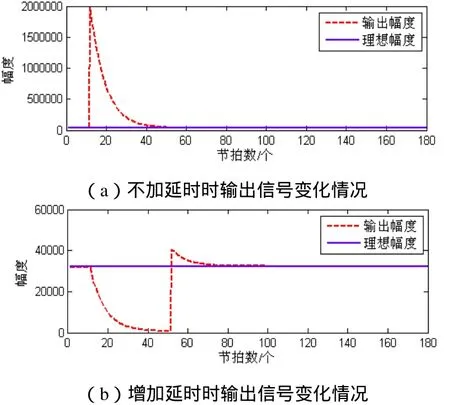

信號輸出幅度變化規律的matlab仿真分析。根據上述增益調整算法,如果直接按照y(n) = x (n) × G (n)求輸出信號,當信號突然由很小變得很大時,會出現過沖現象,為了避免這種現象,給信號增加一個延時,即按照 y (n ) = x (n- 32)× G(n)計算輸出,可以很好地解決過沖的問題,雖然會對信號由小變大時產生一些不利的影響,但是在可以接受的范圍內。仿真結果如圖2和圖3所示。

圖2 輸入信號增大輸出幅度變化

圖3 輸入信號減小輸出幅度變化

圖2 為輸入信號由小突然變大時輸出信號幅度變化情況;圖3為輸入信號由大突然變小時輸出信號幅度變化情況。由圖 2(a)可知,輸出信號大于輸出信號幅度上限值時,增益調整的節拍約為60個節拍。同時可知信號由小突然變大,增益有一個從大到小衰減的過程,如果不延時,大信號與大增益相乘,必然會導致輸出信號很大;信號延時是為了在增益減小到一定程度之后再和大信號相乘,這樣輸出不會過大。對比圖 2(b)可知,經過延時之后,輸出的最大幅度減小了很多,維持在理想幅度上方的時間也短了很多,但是有一段時間處于理想幅度下方,可以忍受信號變小的失真,而不能忍受信號過大導致燒毀器件。由圖 3(a)可知,輸出信號比理想幅度下限小時,調整時間約為600 000個節拍。由圖 3(b)可知,信號如果信號由大變小的時候,由于延時的存在,會使得輸出信號先變大,后變小,同樣存在一段時間內輸出較大的問題,但是由于信號增益變大時較緩慢,如果延時較小,在增益增大不多時就與減小后的信號相乘,那么雖然存在輸出較大,但是與理想幅度相當接近,不會燒毀器件。總的來說,信號的延時需要取適當的值,一般延時32個節拍。

4 音頻AGC的算法的FPGA實現

實驗平臺簡介,本實驗平臺基于 alter公司的stratix_ii GX芯片,音頻采樣A/D采用A/D7655,處理完成之后射頻輸出采用A/D9957進行D/A轉換。

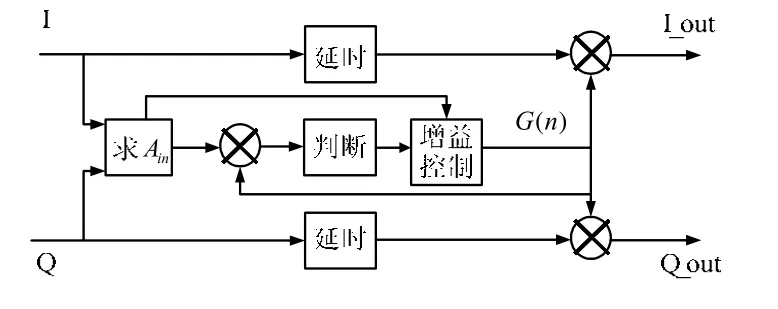

FPGA內部信號處理流程[8]如圖4所示。

圖4 FPGA信號處理流程

音頻信號通過A/D7655采樣進來,進行數字濾波,得到I/Q兩路數字信號。根據用I/Q信號計算出當前信號的幅度值 Ain[9]。反饋的幅度值 A (n ) = Ain(n) × G (n),然后綜合 Ain及A來對增益進行調整。雖然輸出信號小于輸出上限時,調整時間有4 s,但是,當信號幅度變化時,增益的初期調整還是很快,對增益的改變較大,這與要求忽略信號的快變化矛盾,故文中的 Ain信號不用實時的信號,而是將輸入信號按512個采樣點進行分組,每組中的最大值作為 Ain信號,那么實際上就忽略了信號在512個點內的幅度的變化。

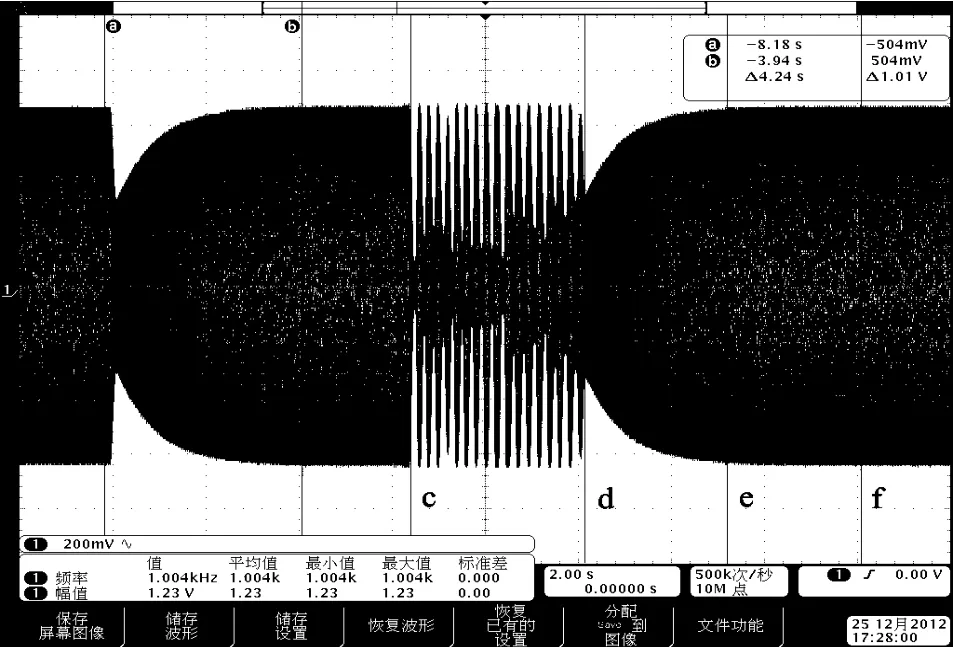

調節輸入信號的幅度,示波器上顯示的輸出信號的變化如圖5所示。

圖5 輸出信號隨輸入信號變化

圖5 中a、b兩個光標是用示波器測量時得到的,c、d、e、f是為了方便敘述后期添加上去的。a、b兩個光標之間是信號突然減小后保持不變時輸出信號變化情況;c、d兩個光標之間是輸入信號快速變化時輸出情況;e,f兩個光標之間是輸入信號突然增大時輸出信號變化情況。由圖5可知,輸入信號減小后,經過 4 s左右可以將輸出信號調整到期望值;輸入信號快速變化時,輸出會跟隨輸入的變化而變化;輸入信號突然增大時,輸出信號不會有明顯的變化。AGC功能基本實現。

5 結語

文中根據實際的語音信號的特點,在傳統AGC算法[10]基礎上,提出了一種適應語音通信的新型的靈活的AGC算法,并對該算法進行了仿真,在仿真結果基礎上,對該算法在實際應用中需要注意的問題進行了詳盡的分析并提出解決方案,最后用VHDL語言在基于 FPGA的硬件平臺上實現該算法[11]。實驗結果表明該算法具有良好的性能,可以以較小的失真為代價,使得輸出的信號幅度平穩性得到極大的提升。該算法已成功運用于某語音通信的發射機中。

[1] 李夕紅,祝忠明,謝興紅.音頻信號采集與AGC算法的DSP實現[J].電子產品世界,2007(04):101-102.

[2] 劉艷.基于FPGA的大動態范圍數字AGC的實現[J].電子設計工程,2009,17(08):42-43.

[3] 諶波,周劼,王世練.約束時間常數大動態數字 AGC的設計[J].通信技術,2011,44(12):144-145.

[4] 淦新富,郭立.基于主元統計的音頻隱寫分析[J].信息安全與通信保密,2007(02):63-64.

[5] 劉吉錄.解析智能型音頻處理器[J].西部廣播電視,2002(02):34-39.

[6] 丁丹,孫華燕.固定調節時間AGC方法的研究及FPGA實現[J].裝備指揮技術學院學報,2009,20(06):87-90.

[7] 徐靖林,李永紅,吳威.WLAN接收AGC調整算法的設計與實現[J].通信技術,2009,42(09):9-11.

[8] 董智紅,崔嵬,吳嗣亮.全數字式前饋AGC設計與FPGA實現[J].北京理工大學學報,2008,28(12):1093-1095.

[9] 李道虎,賈新成.音頻AGC的設計與實現[J].河南機電高等專科學校學報,2009,17(04):16-18.

[10] 黃懷信.一種短波數傳 AGC電路[J].通信技術,1980(08):57-61.

[11] 鐘宏,劉地軍.FPGA與嵌入式處理器通信設計與實現[J].信息安全與通信保密,2011(08):38-39.