應用于GPS導航基帶芯片的SPI IP核的設計和驗證

曹磊 李曉江 馬成炎

(1.中國科學院微電子研究所,北京 100029;2.杭州中科微電子有限公司,杭州 310053;3.嘉興聯星微電子有限公司,嘉興 314000;)

0 引言

隨著SOC的規模不斷擴大,集成的IP模塊不斷增多,設計一款可復用的IP核對于減少設計復雜度、縮短SOC開發周期、提高流片成功率都是重要的一環。SPI(Serial Peripheral Interface)串行通信總線具有配置靈活,結構簡單等優點,被廣泛應用于各位處理器和嵌入式系統當中。因此,對于SPI IP核的設計已經成為業界的設計熱點之一,但現有設計功能還不夠完善。文獻[1]設計了SPI Master模塊,不具有SPI Slave功能;文獻[2]設計了一款基于FPGA的SPI總線,但是不支持四線工作模式,并且對設計本身的結構和特性敘述不多;文獻[3]的設計實現了多功能化的SPI IP核,但是不支持DMA功能,所設計的SPI Master也沒作流水考慮,數據傳輸率受到限制。本文總結上述設計中存在的問題,提出了一種基于APB總線的高速可復用的SPI IP核實現方法,使所設計的SPI接口具有更高的實際可操作性,并且已經在流片回來的芯片上得到了驗證。

1 SPI協議及時序概述

SPI是由Motorola公司首先在其MC68HCXX系列處理器上定義的一種高速的、全雙工的、同步的通信總線,通常只占用四根芯片管腳,分別為MOSI:串行數據輸出線,當SPI模塊為主模塊時,它輸出數據;當SPI模塊為從模塊時,它接收數據;MISO:串行數據輸入線,當SPI模塊為主模塊時,它接收數據;當SPI模塊為從模塊時,它輸出數據;SCK:同步串行時鐘,由SPI主模塊產生;nCS:從機片選線,低電平有效,由主模塊產生。協議規定了SPI的主、從兩種工作模式,工作在主模式的SPI模塊負責產生串行時鐘SCK和對從模塊的片選信號。

圖1 SPI外設接口的四種數據傳輸時序

SPI模塊為了和外設進行數據交換,根據外設的工作要求,其輸出串行同步時鐘SCK的極性CPOL和相位CPHA可以進行配置,因此SPI有四種傳輸時序,其共同特點是每位數據的發送/接收需要一個SCK周期,每次傳輸整數倍個8位數據。當CPOL=0時,串行時鐘的空閑狀態為低電平;當CPOL=1時,串行同步時鐘的空閑狀態位高電平。而時鐘相位CPHA則決定了數據采樣的數據沿,當CPHA=1時,在串行同步時鐘的第二個跳變沿數據被采樣;當CPHA=0時,在串行同步時鐘的第一個跳變沿數據被采樣。SPI模塊的四種

接口時序如圖1所示。

2 SPI IP核的設計

2.1 SPI IP核系統結構及主要功能

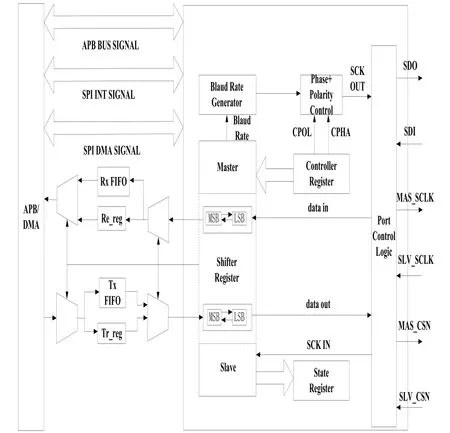

該IP核應用于國家導航基帶項目,基于APB總線進行設計。CPU或者DMA模塊可通過APB總線完成對該SPI模塊的寄存器配置、數據讀寫及中斷處理等操作。所設計的SPI電路主要包括:SPI控制寄存器SPCR、數據發送模塊TRANSMITTER、數據接收模塊RECEIVER、發送/接收同步FIFO、狀態寄存器SPSR。其總體結構圖如圖2所示。

圖2 SPI IP核系統結構

如圖2所示,所設計的SPI IP核實現了傳統SPI協議的四線結構。同時滿足SPI的四種接口時序,通過控制寄存器的CPOL和CPHA位來控制。增加了兩個8位深度、32位寬度的同步可選FIFO,用以提高傳輸速率。每次發送/接收的比特數可在8bits、16bits、32bits選擇,并且首尾比特位的發送/接收順序也可選。考慮到部分應用中可能需要三線結構的SPI核進行半雙工工作,本設計可只使用SDI數據線作三線工作方式。

2.2 主要模塊的設計

本次設計主要采用自頂向下的設計方法,首先完成設計說明文檔,劃分好各子模塊和系統架構,再進行Verilog代碼的編寫,主要實現的功能和設計中部分問題的解決方法如下。

2.2.1 存儲器模塊

所設計的SPI核主要包括一個32位的控制寄存器,實現Master/Slave功能的切換、中斷模式/DMA模式的切換等功能的控制;一個32位的狀態寄存器,記錄發送/接收中斷、同步FIFO空滿標志等狀態;兩個8X32的同步FIFO,可選擇是否使用。

2.2.2 時鐘分頻模塊

當SPI被用作Master時,將會根據控制寄存器SPI_DIV位所設置的分頻數值來對APB總線時鐘進行分頻,用以產生所需要的同步串行時鐘SCK。本設計可完成對APB總線時鐘進行最高4096分頻,默認分頻值是二分頻,所采用的分頻公式為:fpclk= fSCK*2SPI_DIV+1。

2.2.3 SPI Master模塊

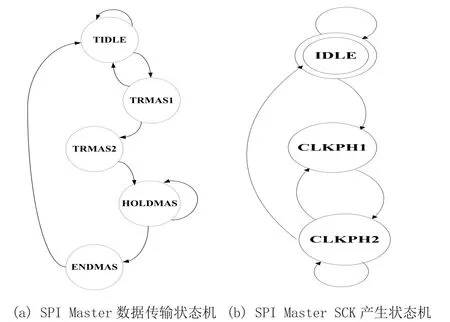

通過控制寄存器MSTR位的配置,可將SPI IP設定在Master工作模式。在此工作模式下,SPI會自主產生nCS片選信號和SCK時鐘信號,同時完成SPI四種時鐘時序的產生邏輯。相比較傳統的SPI Master,本次設計不僅僅再局限于每次8比特的傳輸量,增加了16比特、32比特可選配置。并且,相比較于文獻[4]每二次的傳輸都要間隔幾個總線時鐘用來取數據,會影響傳輸速率。對此,考慮到SCK一般都比APB總線時鐘周期大,可以在每組數據傳輸到最后一個比特時,輪詢發送FIFO,查看是否為空,持續半個SCK周期。若發送FIFO非空,則立即將下一組待發送數據提前準備好,結束輪詢。這樣可以實現傳輸的連貫性,減小本身設計造成的傳輸延遲,增加傳輸速率。所設計的SPI Master模塊的狀態機如圖3所示。

圖3 SPI Master模塊有限狀態機

SPI在發送數據時,所發送的數據要和模塊產生的串行時鐘SCK保持同步,這就要求了在每次SCK后半周期的跳變沿時,發送數據才能變成下一比特。這也使得兩個狀態機在邏輯上出現交叉控制,相互協同工作,同時保證在SCK一個時鐘周期的第一個時鐘沿采樣接收數據,第二個時鐘沿改變發送數據。

TIDLE:當每次傳輸結束或者進行復位后,狀態機處于這一狀態。在該狀態下,若控制寄存器配置成Master模式并且出現傳輸請求,則跳轉到TRMAS1狀態。

TRMAS1:該狀態只保持一個APB總線周期,用于向FIFO或者發送寄存器產生讀指令,然后直接跳轉到TRMAS2狀態。

TRMAS2:該狀態也只保持一個APB總線周期,用以將待發送的一組數據寄存到傳輸移位寄存器中,在HOLDMAS狀態下作移位發送。

HOLDMAS:保持該狀態,直到發送最后一個比特位并且沒有待發送的數據,期間要不斷輪詢SCK產生狀態機和FIFO空滿標志位。

ENDMAS:保持一個APB總線時鐘,用以產生傳輸結束中斷或者DMA請求信號。

CLKPH1:根據所配置的時鐘分頻數值,對應于一個同步串行時鐘SCK周期的前半周期。

CLKPH2:根據所配置的時鐘分頻數值,對應于一個同步串行時鐘SCK周期的后半周期,在傳輸到最后一比特且沒有下一組待發數據時,跳回到IDLE狀態。

2.2.4 SPI Slave模塊

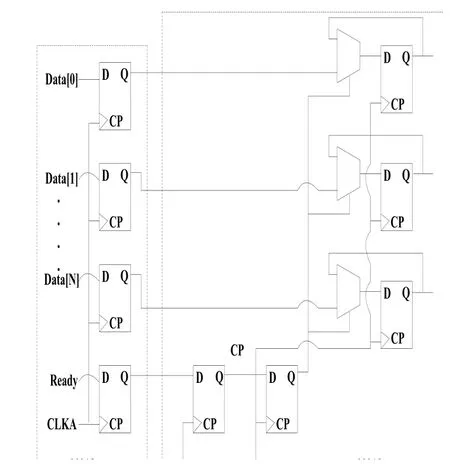

相比較于Master模式,當SPI作為Slave使用時,不需要自己產生同步串行時鐘SCK,由外部輸入SCK時鐘。從空閑狀態到傳輸狀態的觸發條件,也是來自于主設備的nCS片選信號。由此,可以看到Slave的傳輸受到Master的控制,當Master沒有同步串行時鐘輸入時,Slave需要重新返回到空閑狀態,并產生相應的狀態標志位,其狀態機主要參考Master模式設計。另外,因為SCK時鐘是由Master產生輸入到Slave,Slave本身還有來自APB的總線時鐘,這樣當在SCK時鐘域下,完成接收數據的串行轉并行和發送數據的并行轉串行后,需要將保存好的接收數據傳輸到APB時鐘域下,和從APB時鐘域讀取下一組待發數據,這樣就需要在Slave內部作異步時鐘處理操作,用以避免出現亞穩態現象。所采取的方法如圖4所示。

圖4 SPI Slave異步時鐘處理設計

在SCK時鐘域和APB時鐘域之間,每次交換的都是多比特數據,不能采用傳統的單比特同步方法。在本次設計中,使用的是類似于握手協議的處理方法[5],當一次傳輸完成,SCK時鐘域內會產生單比特的標志信號送到APB時鐘域下,經過兩級時鐘采樣再作為控制信號,再將SCK時鐘域下接收的數據轉移到APB時鐘域下,同時將APB時鐘域下準備好的下組待發數據轉移到SCK時鐘域下。這樣就可以滿足異步信號的建立和保持時間沖突問題,避免亞穩態的產生。

3 仿真驗證和綜合結果

本設計,首先用Synopsys公司的VCS仿真軟件,用Verilog HDL語言編寫頂層的Testbench,并在該頂層內編寫測試變量,進行功能仿真。然后,利用Synopsys公司的Design Compile軟件進行綜合,得到網表和延時文件再回到VCS軟件中進行時序仿真。最后,再采用Altera公司EP3SL150F1152 FPGA芯片搭建的驗證平臺上,配合導航芯片ATGB03的其他模塊,完成實測。在驗證無誤的情況下,已經成功流片并且流片回歸測試運行正常,完全符合設計要求。

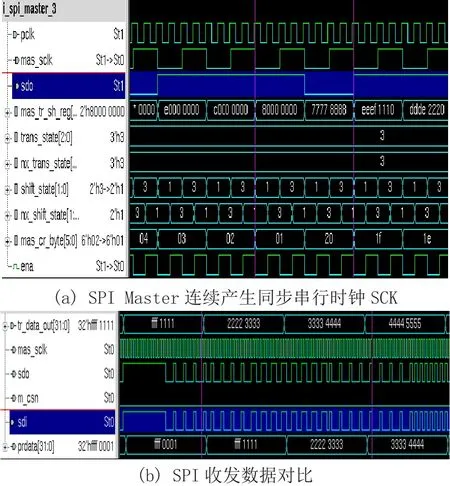

3.1 軟件仿真驗證

該部分的測試代碼設計思路是,在建立的頂層Testbench模塊內[6][7],實例化兩個SPI模塊SPI_M和SPI_S,分別設置成主模塊和從模塊,完成數據的收發測試。圖5所示為VCS軟件上局部時序仿真圖。分別對應著SPI Master模式下,相鄰發送數據可以產生連續的同步串行時鐘SCK;以及從SPI Master中發送的數據進過SPI Slave模塊接收存儲后,能正確的通過APB總線進行讀取。

圖5 SPI IP核仿真結果

從圖5(a)中可以看到,每次最高可以完成32比特的傳輸,并且當mas_cr_byte=0x01時,傳輸到最后一個比特,會自動開始下一組數據的發送,不需要再延遲幾個APB時鐘周期。內部設計的兩個狀態機繼續保持在傳輸狀態,大大提高了傳輸效率。在圖5(b)中,SPI Master中的數據tr_data_out,在進過并轉串處理,從sdi端傳輸到SPI Slave模塊。SPI Slave模塊對串行數據完成采樣存儲到接收FIFO后,從APB總線讀取到的接收數據prdata和所發送的數據tr_data_out一致。

3.2 綜合結果

使用Synopsys公司的Design Compile軟件,對所寫的SPI IP進行綜合,所得到的report_area如 圖6所 示。在SMIC 0.13工藝下,模塊的總面積為37566.1,約合7513邏輯門。在將APB總線時鐘設置在60MHz情況下,SPI IP運行在20MHz仍能完成數據的傳輸,達到了設計目的。

圖6 SPI IP在SMIC 0.13工藝下的綜合結果

4 結束語

本文設計一種應用于GPS導航芯片的可復用SPI IP核,它具有功能完善、速度快、可重用性高等特點,并通過了仿真驗證、邏輯綜合和FPGA平臺測試,證明了其設計的可靠性和實用性,目前已經成功應用到已經量產的ATGB03 GPS導航芯片上,具有實際的商業價值。

[1] 李大江,崔建明. 一種基于FPGA的可配置SPI Master接口設計實現[J].電子技術應用. 2010.10(36):60-62.

[2] 汪永琳,丁一. 一種3線半雙工SPI接口設計[J]. 半導體技術. 2010.5(35):482-484.

[3] 郭林,劉文杰,李躍輝. 基于FPGA的可復用SPI總線實現[J] .2012.4(155):34-37.

[4] Jianlong Zhang, Chunyu Wu, Wenjing Zhang The design and realization of a comprehensive SPI interface controller [J]. IEEE 2011.2:4529-4532.

[5] 謝修祥,王廣生 異步多時鐘系統的同步設計技術[J]. 電子工程師. 2005.5(31):36-38.

[6] Bergeron Janick. Writing testbenches: functional verification of HDL models [M] .[S.L]:Kluwer Academic Publishers.2003.

[7] 高谷剛,羅春. 可復用SPI模塊IP核的設計與驗證[J].單片機與嵌入式系統應用. 2004(11):5-8.