電子產品整機高加速壽命試驗(HALT)技術應用

羅曉武

國家電子計算機外部設備質量監督檢驗中心,浙江杭州 310012

1 HALT 技術介紹

HALT 的工作原理是按照一定的規范程序對產品逐漸的施加應力,直到產品應力超過了其承受極限從而暴露出相應的故障。HALT 主要是運用故障物理學來作為一種激發出產品故障的模式,它是將產品在超過了其承受的應力極限時失效作為主要的研究對象,從而找出它的缺陷來對產品進行相應的整改,提高產品的質量。另外在進行HALT 實驗時,還可以還可以對產品進行測試,從而提高產品的測試性

2 HALT 的原理特點

2.1 HALT 技術原理

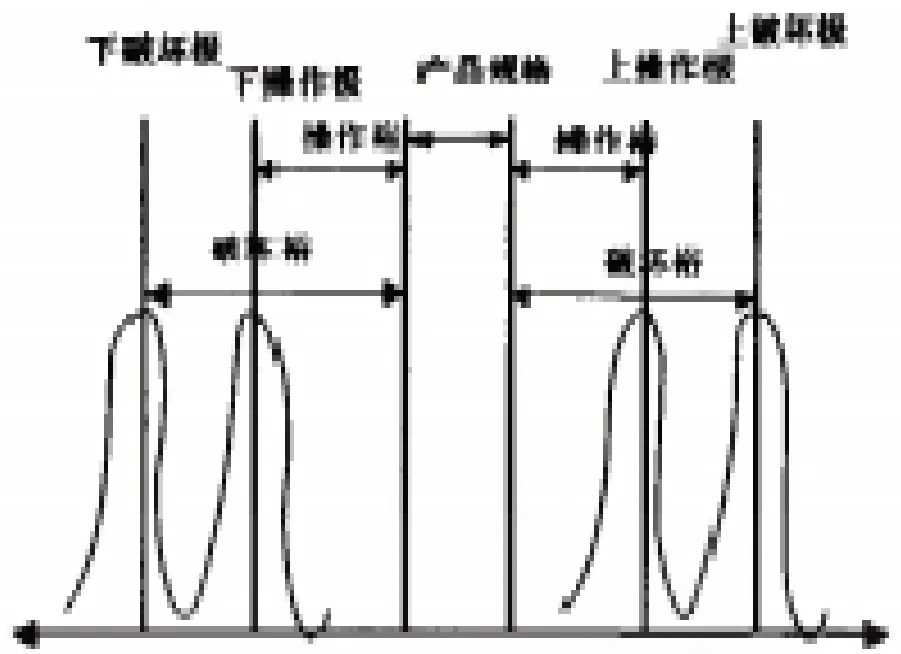

HALT 技術主要原理是通過步進(或叫階梯)增加應力的方式來找出或者說確定所設計產品的“工作極限”和“破壞極限”,這里所說的應力包括環境應力(如高低溫、振動、溫度循環以及溫度和振動綜合)和工作應力(如電源通斷、電壓拉偏、非正常負荷以及電壓和頻率邊際測試等)。

如上圖所示,產品的工作極限指的是在HALT 加速試驗中,施加的環境應力遠遠超過了該產品能承受的最大應力,從而使產品發生了故障,不能進行正常的工作,但是一旦將實驗停止環境應力恢復到標準值以后,產品又能進行正常工作的情況。而產品還有破壞極限,顧名思義,就是在環境應力大大超過豈能承受的最大范圍時,產品遭到了破壞,停止工作,就算應力恢復到正常值一樣不能工作,受到了徹底的破壞。

在HALT 中對產品施加環境應力時還可以通過溫度來進行,它的工作原理主要是運用高熱應力和熱疲勞輪流施加在產品上,使產品的物理性質受到破壞。特別是在電子產品中,因為電子產品種類繁多,其制造的材料也都大不相同,所在產品在進行HALT 時承受了高低溫從不同方向襲來的熱應力,其內部結構發生了變化,從而暴露出產品的缺陷。

2.2 HALT 技術特點

HALT 是以逐漸遞增的形式來對產品施加環境應力以及工作應力的,并在在進行試驗時要不斷對施加的的應力進行提高,從而使產品發生故障蠻好從故障中找出產品的缺陷。而HALT中對產品施加應力后產品出現的失效情況是通過超過產品設計時的最大環境應力承受度來激發出來的,并且這些是小的情況都是產品在實際的使用過程之中可能會出現的問題,如果不然,那么HALT 試驗就沒有多大的意義。

3 HALT 以及測試性驗證

HALT 不僅試驗時間(或周期)短,而且暴露的故障也很全面,并且在進行HALT 試驗過程中產品可能會出現的失效故障在實際使用過程中也會可能會出現的類似情況,這是因為HALT 的工作原理就是將產品的故障暴露在人們的眼前,并且對這些故障進行相關的解決與改善。因而,HALT 和測試性驗證是密不可分的。HALT 現今適合于各種不同層級的帶有PCB控制板的電子產品中,一方面來說HALT 試驗可以將產品的缺點有效地暴露,同時還能對產品內部的的BIT 系統(內部自檢)的故障有效地暴露,從而從根本上對產品的可靠性以及相關的測試性進行提高。那么這樣一來,在產品還處于設計階段時,HALT 就可以將BIT 設計中所存在的一些問題及時的發現,從而實現對設計工藝以及施工工藝的改進。

3.1 HALT 試驗的同時必須對相關功能進行測試

當產品進行HALT 試驗時,就需要設定一個相對完善、健全的測試系統來作為整個試驗的技術支持。HALT 試驗與普通的鑒定試驗有著極大的不同,所以當其進行實驗的過程中就必須進行相應的性能測試以及功能測試,,并且對實件的狀態進行實時的檢測,這個過程是一個循序漸進的過程,所以只有當試驗室有效地進行實時的監控,才能對故障發生時的盈利水平及時準確的獲取。

進行實時的功能檢測一方面可以知道產品發生故障時的應力水平,就可以對發生故障時具體的產品狀態進行及時的掌握,其次再通過科學的分析,得到相關的改進方案。另一方面來講,進行實時的功能檢測還可以在試驗的時間上一定程度的所見。如果試驗結束以后才進行相關的檢測,就很有可能出現整個HALT 試驗結束了而試驗樣品還沒有發生故障,或是試驗還沒有結束,試驗樣品就因已經發生故障而停止結束的情況。

前一種情況會造成HALT 欠試驗,最終無法得到完整的HALT 試驗數據結果的情況;后一種情況更直接會造成HALT試驗的失敗。

3.2 HALT 和測試性驗證的合理性

HALT 和測試性驗證都有著一個共同的目標,就是激發出產品的故障。但兩者之間的區別在于測試性是在測試中才能體現出來的性質,而HALT 自始至終都在進行功能測試或是性能測試。

在進行HALT 之后,應該重視其產品本身故障的同時,還應該重視測試性驗證和整改產品測試性設計中的薄弱環節。

4 對檢測率進行驗證

4.1 確定相關的檢測率試驗方案

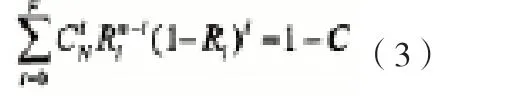

在進行HALT 試驗時,假設某一個隨機變量為Sn 并且服從相應的分布參數n(正整數)以及P(成功概率)的二項分布,那么對于任何一個正整數K(注:k 的取值范圍{0,1,2~~+∞}),可以用下式表示:

式(1)中:n 為所依據的樣本實際數量;

Sn 表示的是第n 次獨立試驗時已經成功的次數。

因為在對β 進行使用得過程中,其實就是將實際的FDR降低到最低過程中可能接受的數值P1 而最終使試驗通過的概率,但是承載方風險α 則是指的產品本身的FDR 已經達到了設計目標但是卻沒有被接受的概率,所以理應滿足下面的式子:

經過不等式計算后可能得出的答案可能無窮多,為了使得試驗的費用盡量的減少,所以一般情況下采用n 求最小解。

4.2 對檢測率相關的區間估計以及點估計

上面式子中只是給出了相應的測試性驗證的實際測驗方法,并沒有對測試性相關參數的實際數值進行說明。

檢測率為FDR=ND/Nr,分子是正確檢測到的故障,分母是故障總數。

基于二項分布的檢測區間估計:C 為置信度,F 為檢測失敗數,N 為故障總數。

單側置信下限估計:

當處于一定置信度(C)下時對于兩側的置信區間進行估值估計:

上面例子中的n 是能夠被確定的,并且是可以通過不等式進行計算所最終取得的最小數值。

但是,我們知道HALT 方法并不能夠進行提前的預知,因此,當實際發生的故障數目無法被確定的時候。就可以通過等比例法對其進行一定程度的壓縮,將HALT 試驗中實際發生的故障數轉化成測試性驗證試驗方案中要求的故障數。

若是故障數目沒有要求的多,這是不能按等比列來擴大故障數的,因為故障數太少就會帶來很大的波動性。

5 結論

在對電子產品進行可靠性驗證相關測試過程中,對于硬件本身的故障所引發的問題,應用HALT 進行試驗,無疑是最直接、最高效的試驗方法之一。

隨著科技的發展以及人們對HALT 技術的不斷探索研究,HALT 技術將會更加成熟、更加廣泛地應用于電子產品的研發、設計乃至定型試驗過程中,HALT 試驗最終將極大地提高電子產品整體的可靠性水平。

[1]王道震,邵家駿,王曉峰.基于HALT的測試性驗證方法研究[J].電子產品可靠性與環境試驗,2010,28(1).

[2]史曉雯,徐劍峰,徐丹.HALT試驗技術綜述[J].環境技術,2011,34(3).

[3]褚衛華,陳循,陶俊勇,等.高加速壽命試驗(HALT)與高加速應力篩選(HASS)[J].強度與環境,2002,29(4).

[4]朱建華.HALT 測試綜述[J].電子測試,2008(7).

[5]王世濤.HALT與HASS技術原理及其應用[J].四川兵工學報,2009,30(12).