基于NiosII的視頻采集及網絡傳輸系統的實現

袁 興,王林林,王桂海,陳新華

(山東科技大學信息科學與工程學院,山東青島266590)

0 引言

在工業生產和日常生活中對視頻采集、傳輸系統的應用越來越廣泛,且對系統實時性和傳輸圖像質量的要求也越來越高。為滿足系統要求,提出采用NiosII處理器結合SOPC技術來實現網絡傳輸。由于NiosII承擔著視頻采集、網絡傳輸等多個任務,為提高傳輸的實時性等硬性要求,采用雙處理器架構,分別用于視頻采集和網絡傳輸。NiosII之間通過資源共享的方式進行信息交互,實現兩核之間的協同通信,提高系統效率。軟件方面采用Linux系統作為開發平臺,通過移植RTP/RTCP流媒體協議實現視頻流的網絡傳輸,該系統具有高度集成、可重配置、性價比突出等優點。

1 視頻采集及網絡傳輸系統的整體架構

基于SOPC實現的系統構架如圖1所示。在該系統中,處理器各自擁有獨立的Avalon總線。兩處理器私有、獨立訪問的模塊 (如SSRAM與UART),需連接到各自的Avalon總線上。在該SOPC系統中,雙核NiosII共同享有的模塊(如IMG_SDRAM與FLASH),應與兩條Avalon總線相連。在為系統各模塊分配基地址時,與同一條總線相連的各模塊對應的基地址不能重疊,否者會引起訪問沖突。若模塊不在同一條總線上相連,其地址可以與其另一條總線上的任何模塊重疊,而二者共有的模塊,則必須設為獨有地址[1]。

圖1 雙NiosII構架的SOPC系統結構框架

2 系統視頻采集和網絡傳輸

2.1 視頻捕捉和本地顯示

視頻捕捉和本地顯示模塊由攝像頭、VGA控制器、數據轉化構成,其組成框圖如圖2所示。I2C_Config模塊通過I2C協議配置解碼芯片ADV7180識別PAL視頻數據,硬件模塊ITU-R656將解碼的數字信號轉換成YCrCb信號并得到像素時鐘、場同步信號、消隱信號、VGA時序信號等信息。

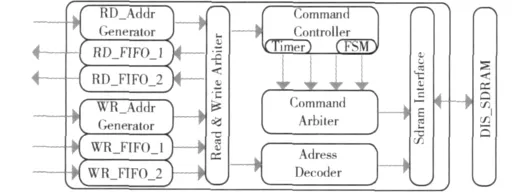

視頻輸入信號為隔行掃描,為正確的VGA輸出顯示需要處理逐行掃描數據,即將隔行的有效視頻數據轉換成逐行的視頻數據。解碼后視頻數據量大,為保證時序滿足并能正確顯示,需要一個存儲空間作為緩存 (DIS_SDRAM)。為將解碼得到的視頻數據存入緩存,使用4_Port SDRAM控制器與DIS_SDRAM通信。4_Port_SDRAM有兩個Read Port和兩個Write Port,如圖3所示,分別用于奇場與偶場數據的寫入和讀出。VGA顯示的是一幀視頻中的偶場數據,通過VGA_controller產生Read信號作用于RD_FIFO_1,從DIS_SDRAM緩存中得到偶場視頻數據進行顯示,而RD_FIFO_2讀出的奇數場數據用于遠程網絡傳輸的數據源。

圖2 視頻捕捉和本地顯示結構框架

圖3 4_Port SDRAM Controller框架

2.2 圖像采集與DMA傳輸

由于系統需要實時處理大量的視頻數據,而且方便網絡發送,需要將視頻數據進行存儲。為提高系統的執行效率,加快數據的存儲與訪問速度,系統采用DMA的傳輸方式[3],將圖像數據直接存入IMG_SDRAM中。該模式不過分依賴CPU,可以大大節省系統資源,是內存與外設之間進行批量數據傳輸的最佳選擇。

解碼芯片得到的數據經過ITU_R656Decoder模塊處理后得到YUV422格式的數據流,并且一行像素的有效行起始(SAV)和行結束 (EAV)標志包含在數據流中,YUV422格式的一行像素的時序圖如圖4所示。

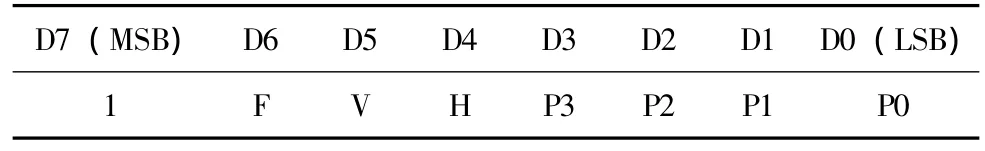

為將視頻正確的采集并存入IMG_SDRAM中,依據YUV數據流的定時基準信號 (SAV、EAV)可以得出一幀圖像的開始與結束。SAV(Start of Active Video)與EAV(End of Active Video)分別由4個字節組成,格式為FF 00 00 XY。前3字節是固定前綴,用于定時基準。XY包含了場標識、場消隱、行消隱等信息:其數據格式如表1所示。

圖4 YUV422一行像素時序圖

表1 定時基準信號XY比特分配表

其中F、V、H信號不同值的組合代表了視頻不同場序及有效視頻的開始與結束;P0、P1、P2、P3為保護位,它們的值取決于F、V、H的狀態,可以依據上述信息判斷一幀圖像的始末并及時存儲在IMG_SDRAM中。

由于SOPC系統中沒有相應的IP核完成該系統的DMA任務,為此依據Avalon-MM總線協議[4]規范,自行設計W/R_to_Sdram的IP核[5]。該模塊既有主端口信號,也有從端口信號,如圖5所示。IP核的從端口接收Image_cpu發送的地址信息,告知IP核將視頻數據寫入到IMG_SDRAM中的哪個地址段中,同時Image_cpu可通過該端口獲得存儲過程的狀態 (如Start、Done),主端口發出讀信號作用與4_Port_sdram_controller的RD_FIFO_2,得到的奇場視頻數據直接寫入到IMG_SDRAM中。在保證不失系統性能的前提下,為節省存儲空間的開銷,該模塊只將奇數場中的亮度信號Y[7:0]寫入到SDRAM中,這樣不僅減少數據量便于存儲也有利于數據在網絡中傳輸,節省帶寬。

圖5 W/R_to_Sdram IP核讀/寫數據框架

2.3 雙核之間的內存映射與數據搬移

該FPGA開發板上只有兩片SDRAM(16M*2)DIS_SDRAM和IMG_SDRAM。DIS_SDRAM用于視頻捕捉與本地顯示模塊,另一片IMG_SDRAM用于視頻圖像的存儲和Linux系統的內存。通過劃分區域的方法將 IMG_SDRAM分為兩個相對獨立的內存空間,分別配置給W/R_to_Sdram存儲視頻和 Net_cpu運行 Linux,實現內存共享。

在SOPC系統中,共享存儲IMG_SDRAM分配的地址為0x4000000~0x4ffffff共16M bytes。為將該內存進行劃分,通過將SOPC系統生成的custom_fpga.h頭文件中的IMG_SDRAM基地址修改成0x4600000,即將IMG_SDRAM的低6M bytes劃分給W/R_to_sdram使用,高10M bytes分配給Net_cpu。Linux啟動時就會從地址0x4600000開始執行,而不是SDRAM的基地址。

網絡發送時,需要將亮度信號從DIS_SDRAM存儲空間中轉移到IMG_SDRAM中,數據流向如圖6所示。W/R_to_Sdram采用DMA方式將亮度信號經過SDRAM控制器寫入到IMG_SDRAM。這時,Linux系統需要訪問共享內存IMG_SDRAM中的另一塊區域Image_data_memory,將該存儲區域的視頻數據讀取并進行網絡發送。Linux通過內存管理機制MMU,調用mmap()函數將IMG_SDRAM的物理地址映射到虛擬地址空間,這樣對內存的操作不需要調用Read/Write函數,可直接通過地址指針獲取,提高訪問速度。

內存地址及數據信息全部保存在Linux系統中的/dev/mem設備文件里,調用mmap()函數映射該設備文件實現共享內存的訪問。Mmap()調用形式如下:(int*)mmap(void*addr,size_t len,int prot,int flags,int fd,off_t offset);其中len是映射到地址空間的字節數,prot參數指定共享內存的權限,fd參數為映射到進程空間的文件描述符。offset參數一般設置為0,表示從文件頭開始映射。addr參數指定文件應被映射到進程空間的起始地址,一般指定為空指針,該任務交給內核完成。函數返回值為內存映射到進程空間的地址,可直接操作該虛擬地址訪問物理內存。在該系統中,mmap()函數使用方法如下:先得到文件描述符fd,即fd=open(“dev/mem”,O_RDWR);之后得到映射后的虛擬地址adr_map,即:

adr_map=(int*)mmap(null,map_length,prot_read|prot_write,map_shared,fd,IMG_SDRAM_BASE);

2.4 雙核間通信機制

系統中需要特定機制協調雙核之間的通信,防止對共享內存同時進行操作,導致系統崩潰。通常處理器之間的信息交互有以下幾種解決方案:

圖6 雙核間內存共享與數據搬移框架

表2 多核處理器間通信解決方案

基于上述特點,參考方案2和方案4,采用乒乓查詢的方式進行雙核間通信。雙核之間分別設置一個標志位,存在于SDRAM特定地址中,通過查詢該特定地址的值,完成雙核之間的信息交互。

2.5 Linux系統移植與網絡傳輸

在搭建SOPC系統時,得到的custom_fpga.h文件包含了系統所有硬件的配置信息。Linux系統在進行內核配置、裁剪時依據配置信息選擇UART、DM9000網卡等驅動,內核依照這些選項及custom_fpga.h進行編譯,得到定制的Linux系統。

實時傳輸協議RTP[6]為數據提供了具有實時特征的端對端傳送服務,能夠在單播或者多播的網絡環境中實現流媒體的實時傳輸。在Linux平臺上進行網絡編程,需要RTP相關的庫作支持。Jrtplib[7]是C++實現的開源RTP庫,使用socket機制實現網絡通訊,方便在多種系統上移植。所以Linux系統需要移植Jrtplib庫支持RTP協議。

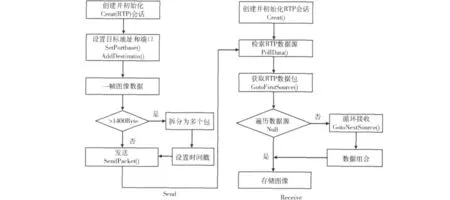

對于發送端,首先生成RTPSession類的實例聲明此次RTP會話,并調用Creat()函數完成初始化。SetOwnTimestampUnit()函數設置恰當的時間戳,保證數據發送和接收保持同步。數據發送時,先調用SetPortbase()和AddDestination()設置目標地址和端口,之后調用Sendpacket()函數向遠程端發送數據。對于遠程接收端,調用Jrtplib庫中的PollData()函數接收RTP數據報。通過相關函數讀出數據報的時間戳和同步源信息,將同一時間戳的數據恢復成一幀圖像。函數GotoFirstSource()和GotoNext-Source()遍歷發送過來的數據源,調用該函數實現實時接收和存儲顯示。

RTP發送與接收數據流程如圖7所示。對于發送端,一數據包發送的最大字節默認為1400 byte。而一幀圖像遠遠超過1400byte,需采用拆分發送,并將同一幀的拆分包的時間戳設為同一值,這樣接收端就將相同時間戳的數據重新組成一幀圖像。

圖7 RTP發送與接收數據流程

3 實驗結果分析

運行設計的系統并設置遠程端的IP地址和端口號,攝像頭的視頻數據經過解碼,拆包并依據RTP協議發送到該目的地址,接收端等待接收服務器發送的數據并顯示圖像。

為保證系統內存映射和數據搬移的正確性,通過測試程序打印出內存地址段中的數據與NiosII IDE在Debug模式下的Memory監視窗口的數值進行對比,驗證了映射數據的一致性。系統成功抓取一幀視頻數據,通過RTP協議發送到指定的目的地址,接收端遍歷接收到的數據源,重新組合成一幀圖像進行顯示,接收到的圖像效果如圖8所示。

圖8 遠程接收端接收到的圖像

4 結束語

網絡視頻傳輸系統在工業生產、日常生活等方面的應用日益廣泛,高性能的系統體現在嵌入式服務器的搭建。本文提出的基于FPGA的雙NiosII的SOPC系統方案具有運行穩定可靠,實時性強、可重配置性強等特點。系統通過內存映射可直接訪問物理內存而不需要調用write/read函數,加快了訪問內存數據的速度,為圖像的網絡發送提供了可能。系統采用DMA方式將視頻數據直接存入到SDRAM中而不經過CPU,提高了系統處理效率。整個傳輸系統共享同一塊SDRAM作為視頻存儲及Linux系統內存,降低了硬件電路的開銷和復雜性,縮減了系統成本。

[1]ZHANG Ling,XIA bo,HE Wei.Design and implementation of dual NiosII architecture in the network video surveillance system[J].Information And Electronic Engineering,2007,5(4):275-279(in Chinese).[張玲,夏博,何偉,等.網絡視頻監控系統中雙NiosII架構的設計與實現 [J].信息與電子工程,2007,5(4):275-279.]

[2]SUN Yanjing,LIShiyin,DONG Yang.Embedded networked video acquisition and compressed system based on RTP [J].Computer Engineering and Design,2006,27(16):2939-2942(in Chinese).[孫彥景,李世銀,董楊.基于RTP的嵌入式網絡化視頻采集壓縮系統 [J].計算機工程與設計,2006,27(16):2939-2942.]

[3]TAO Baoquan,FU Yongqing,LIANG Pan.Design of video capture and transmission system based on SOPC [J].Applied Science and Technology,2010,37(4):31-34(in Chinese).[陶寶泉,付永慶,梁盼.基于SOPC的視頻采集及傳輸系統的設計[J].應用科技,2010,37(4):31-34.]

[4]Altera.Avalon interface specifications[EB/OL].[2012-04-01].http://www.altera.com.

[5]GAO Feng,WANGYusong.Design and implementation of user-defined Avalon device on NiosII[J].China Measurement Technology,2007,33(4):105-108(in Chinese).[高楓,王玉松.基于NiosII自定制Avalon設備的設計與實現 [J].中國測試技術,2007,33(4):105-108.]

[6]WANG Lihu,LIU Chunsheng.Application of MPEG-4 video streaming transmission based on RTP/RTCP [J].Industrial Control Computer,2006,2006,19(3):31-32(in Chinese).[汪理虎,劉春生.RTP/RTCP協議下的MPEG-4視頻流傳輸系統應用研究[J].工業控制計算機,2006,19(3):31-32.]

[7]LIU Jianjun,RUAN Xuebin.Realization of JRTPLIB-based video monitor system [J].Computer and Digital Engineering,2011,39(4):186-187(in Chinese).[劉建軍,阮學斌.基于JRTPLIB下的視頻監控系統的實現 [J].計算機與數字工程,2011,39(4):186-187.]

[8]ZHANG Zhengbing,DENG Huiping,XIA Zhenhua.A video capture and transmission system based on NiosII[J].Video Engineering,2007,31(6):28-29(in Chinese).[張正炳,鄧慧萍,夏振華.基于NiosII的視頻采集與傳輸系統 [J].電視技術,2007,31(6):28-29.]

[9]WANG Xuguo,YU Shuanglin.Development of the video capture and process system based on ARM [J].Information Technology,2011(9):121-124(in Chinese).[王緒國,余雙林.基于ARM的視頻采集與處理系統的開發 [J].信息技術,2011(9):121-124.]

[10]XIAO Wencai,FAN Feng.The FPGA design of real-time vi-deo acquisition system [J].Chian Digital Cable Tv,2006(21):2104-2108(in Chinese).[肖文才,樊豐.視頻實時采集系統的 FPGA設計 [J].中國有線電視,2006(21):2104-2108.]

[11]GUO Yongcai,SU Yuwei,GAO Chao.Design and implementation of real time infrared image collection system based on FPGA [J].Chinese Journal of Scientific Instrument,2011,32(3):514-518(in Chinese).[郭永彩,蘇渝維,高潮.基于FPGA的紅外圖像實時采集系統設計與實現 [J].儀器儀表學報,2011,32(3):514-518.]

[12]Altera.NIOSsoftware development handbook[EB/OL].[2012-04-01].http://www.altera.com/literature/hb/nios2/n2sw_nii5v2.pdf.

[13]LI Lanying.Design principle and application of the SOPCbased on embedded NiosII[M].Beijing:Beijing University of Aeronautics and Astronautics Press,2006(in Chinese).[李蘭英.NiosII嵌入式軟核SOPC設計原理及應用[M].北京:北京航空航天大學出版社,2006.]

[14]WANG Jinming.Verilog HDL programming tutorials[M].Beijing:Posts and Telecom Press,2004(in Chinese).[王金明.Verilog HDL程序設計教程 [M].北京:人民郵電出版社,2004.]

[15]SUN Qiong.Embedded Linux of detailed application development[M].Beijing:Posts and Telecom Press,2006:304-327(in Chinese).[孫瓊.嵌入式Linux應用程序開發詳解[M].北京:人民郵電出版社,2006:304-327.]