基于RS485的數據通信協議的設計與實現

鄢 濤,杜小丹,劉永紅,胡 慶

(1.模式識別與智能信息處理四川省高校重點實驗室 四川 成都 610106;

2.成都大學 信息科學與技術學院,四川 成都 610106;3.成都大學 電子信息工程學院,四川 成都 610106)

RS485作為一種串行通信標準,采用差分收發方式,實現通信系統的物理層連接,具有通信距離遠,傳輸速度快,抗噪聲干擾性好等優點[1-4],已被廣泛應用于各種領域。文中所介紹的通信系統能夠接收高低速串行數據,針對高低速數據的不同速率和接收模式的要求,本文以RS485標準為物理層基礎,在現場可編程門陣列(FPGA)平臺上設計并實現了高低速串行數據的可靠接收。

1 協議描述

用特殊的標志字來表示數據幀的起始位置,以便接收有效的數據信息,從而實現同步。標志字選用16進制數“FDB18540”,這種標志字經過大量測試表明它的獨立性很好,不會和數據內容重復,可以有效避免假同步現象。高速數據接收時,在同步高速時鐘的上升沿時,檢測高速數據的標志字,當檢測到標志字時,就意味著有效數據的到來,系統開始接收高速數據。

1.1 高速數據通信協議

1.2 低速數據通信協議

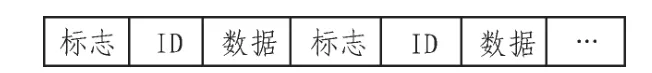

本通信系統的高速接口包括時鐘和數據兩個接口,高速數據接收采用同步RS485通信協議,高速時鐘速率為3.6864 MHz,與數據發送時鐘同源,可以利用同步時鐘實現數據接收同步。高速數據具有特定的幀格式,每幀容量為2 kB,幀格式[5-6]如圖1所示。

圖1 高速數據幀格式Fig.1 Frame format of high-speed data

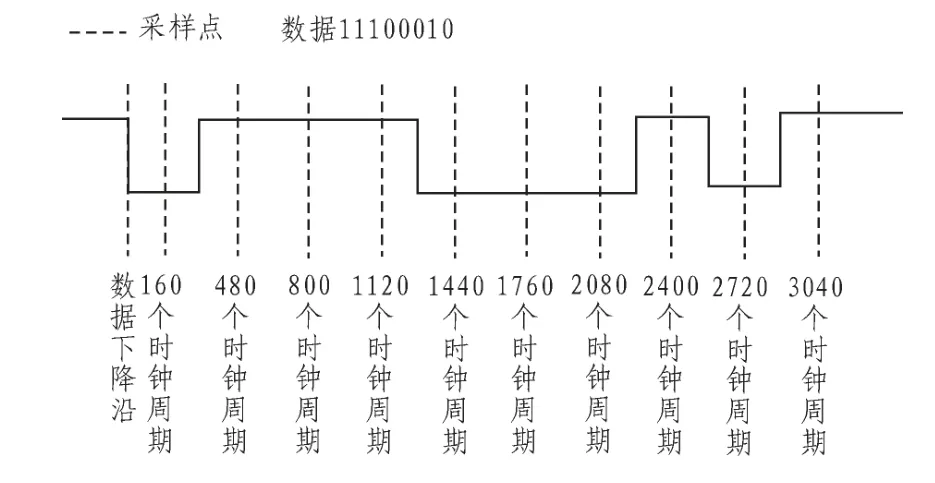

低速數據沒有同步時鐘控制,采用異步RS485通信協議,以字節作為通信協議的基本單元,每字節1個起始位,8個數據位,1個截止位,波特率115.2 kbps。低速數據接收時,利用FPGA的外部時鐘源作為檢測時鐘,時鐘頻率為36.864 MHz,每傳輸1bit數據占用320個時鐘周期。當檢測到數據的下降沿時,就開始對檢測時鐘計數,實現低速數據的位同步,當記到160個時鐘時,對輸入數據進行檢測,當檢測到輸入的信號為低電平時,以后每隔320個時鐘周期,進行一位數據的接收,共接收8位,再隔320個時鐘周期后,檢測截止位是否為高電平,如果為高電平,則接收的8位數據為有效數據,再進行下一字節數據接收。否則,丟棄數據,時鐘計數歸零,重新檢測數據。可以看出,對低速數據接收的采樣點是每位數據的中間位置。信號在連續長“1”之間的短“0”很容易受到碼間干擾影響變短,但本文在中間位置進行檢測,只要短“0”的長度在原始信號長度的一半以上就可以得到正確數據。數據接收同步示意圖如圖2所示,可以看出這一字節的起始位為0,截止位為1,通過檢測時鐘對數據采樣,數據被正確接收。這種通過檢測數據跳變沿作為數據起始的同步方法可以減少RS485通過雙絞線長距離傳輸時的碼間干擾。

圖2 數據接收同步示意圖Fig.2 Schematic diagram of data receiving synchronously

在數據進入FPGA后,再對低速數據進行打包,每包容量為512B,在包頭和包尾分別加入標志字,再通過USB接口傳送到計算機,通過對低速數據打包,可以有效地區分同時接收的高低速數據,防止數據出現不連續情況。

2 硬件設計

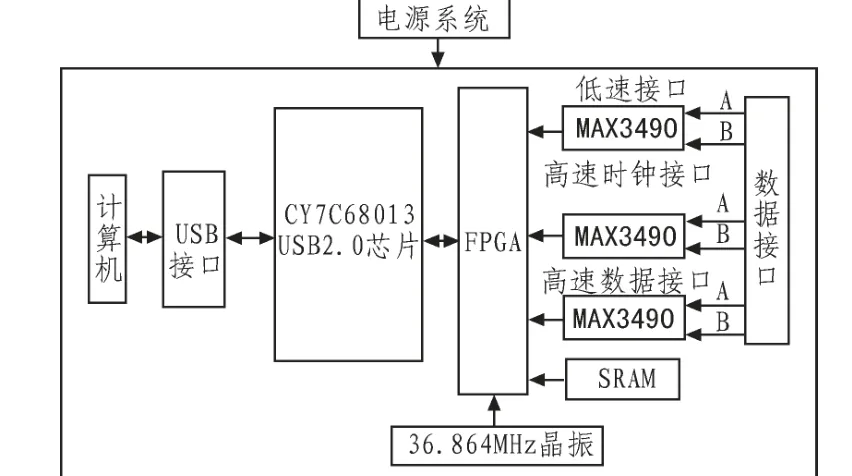

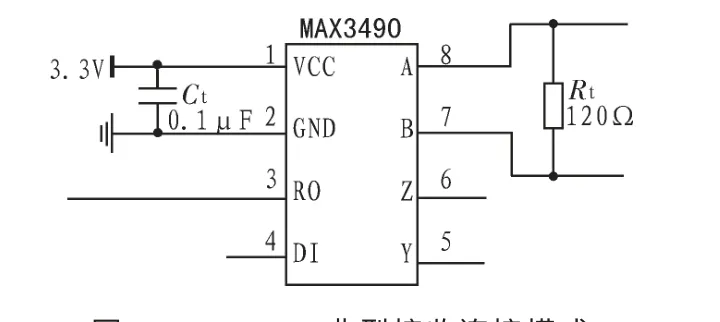

硬件原理框圖如圖3所示。模式,輸入電壓范圍為-7~+12 V,輸出電壓高電平為最小為供電電壓減去0.4 V,低電平最大為0.4 V。它的典型接收連接模式如圖4所示。

圖3 硬件原理框圖Fig.3 Functional block diagram of the hardware

圖4 MAX3490典型接收連接模式Fig.4 Typical receiving connection mode of MAX3490

FPGA選用XILINX公司的Spartan3系列的XC3S200芯片,它采用多電壓供電,其中內核電壓為1.2 V,I/O口驅動電壓為3.3 V,其他的輔助電壓為2.5 V。該芯片含有4320的邏輯資源、141個可用的I/O口。外部晶振源頻率為36.864 MHz,作為低速數據的檢測時鐘,利用FPGA內部的倍頻模塊對它進行倍頻后作為高速數據接收的外部時鐘。

FPGA外部外加了一個容量為1 MB的SRAM作為外部緩存,它的作用主要是作為高速數據的實時緩存,彌補利用硬件邏輯無法提供大容量空間進行高速數據的緩沖存儲的缺點,可以保證高速數據在傳輸過程中不會在FPGA接收環節丟數。SRAM芯片選用CY7C1059DV33,它的深度為1M,寬度為8 Bit,容量為1 M×8 Bit,3個控制端控制SRAM的讀寫操作,支持異步通信。

FPGA利用CY7C68013芯片通過USB接口與計算機進行通信。CY7C68013屬于Cypress公司的FX2系列產品,是Cypress公司生產的第一款USB2.0芯片。 CY7C68013是一個帶增強型MCS51內核和USB接口的單片機,完全遵從USB2.O協議,可提供高達480Mbps的傳輸率;內部集成PLL(鎖相環),最高可使5l內核工作在48 MHz;對外提供兩個串口,可以方便地與外部通信;片內擁有8KB的RAM,可完全滿足系統每次傳輸數據的需要,無需再外接RAM。

3 邏輯設計

RS485標準是基于差分傳輸的[7],它使用一對雙絞線作為傳輸介質,通過兩根線之間的差分電壓來表示相應的邏輯狀態。數據信號進入FPGA之前,必須經過接口芯片進行電壓轉換[8]。根據設計要求,高低速接口最高的輸出碼率為3.686 4 MHz,由于本通信系統只是接收數據,所以工作在單工模式。因此,RS485接口芯片選用MAX3490,它采用3.3 V單電源供電,波特率最高可達10Mbps,可以支持全雙工工作

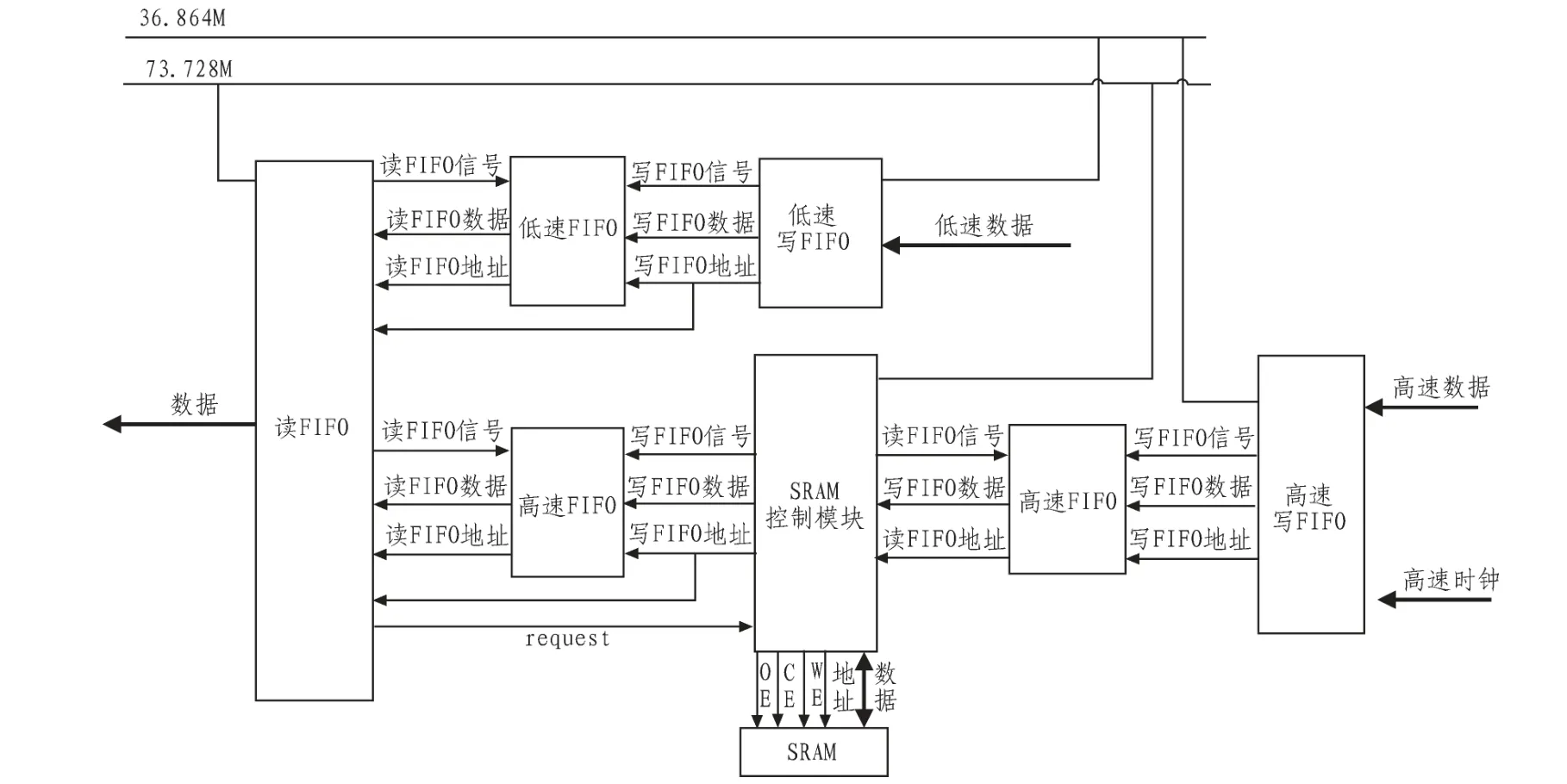

RS485接收芯片將收到的差分信號解為串行信號,FPGA內的程序對串行信號進行檢測處理,接收數據。FPGA內部分別為高低速數據開辟了2k的FIFO作為緩存,為解決高速數據傳輸過程中可能由于FPGA內部緩存不夠而導致丟數的問題,在FPGA外部加入1MB容量的SRAM作為外部緩存。低速數據接收采用一級緩存結構,高速數據接收采用采集三極緩存結構。圖5為系統邏輯框圖。

圖5 接收高低速數據邏輯結構Fig.5 Data logical construction in receiving with high or low speed

FPGA內部模塊主要包括高速寫FIFO模塊[9]、低速寫FIFO模塊、SRAM控制模塊,讀FIFO模塊。高速寫FIFO模塊和低速寫FIFO模塊負責將接收到的數據暫時存入內部FIFO中;SRAM控制模塊的功能主要是控制SRAM的讀出、寫入,將一級緩存FIFO中的數據寫入SRAM,將SRAM中的數據讀出寫入三級緩存FIFO中。讀FIFO模塊主要是根據計算機下發的命令,選擇讀取高速FIFO和低速FIFO中的數據,并將數據送至數據總線。在設計FIFO過程中,讀FIFO的時鐘信號必須大于寫FIFO的時鐘信號,否則,將會導致FIFO溢出,接收數據丟失。本設計中讀FIFO時鐘頻率是寫FIFO時鐘頻率的二倍,讀FIFO的速度遠大于寫FIFO速度。

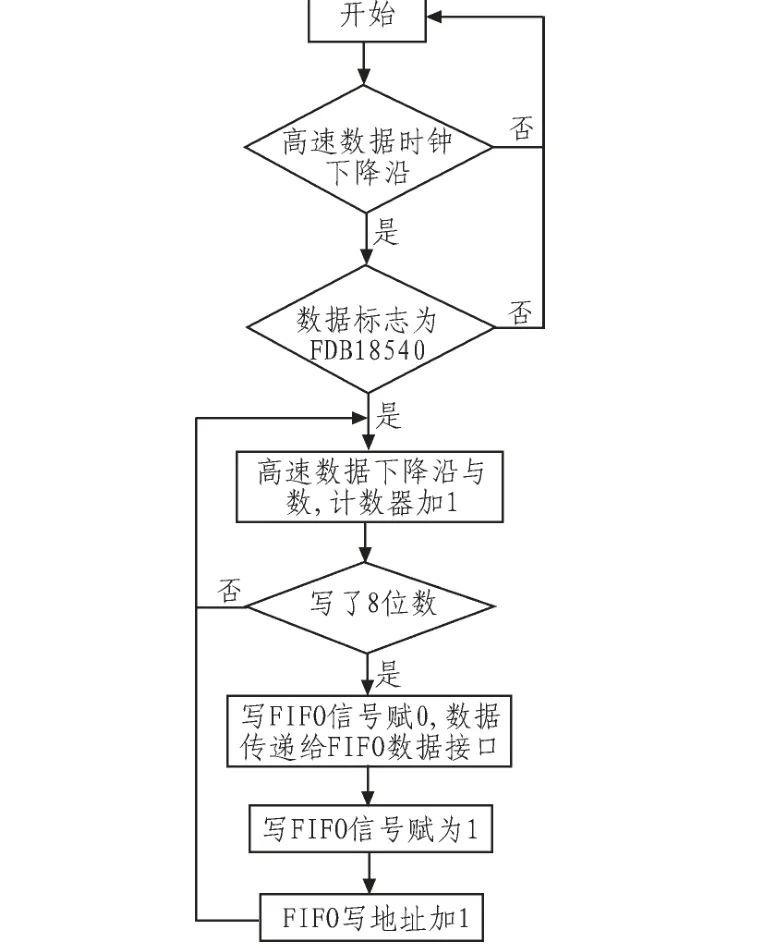

傳輸協議是基于XILINX公司的XILINX7.1開發環境利用超高速集成電路硬件描述語言(VHDL)設計。圖6為高速寫FIFO模塊,圖7為低速寫FIFO模塊流程圖。

圖6 低速寫FIFO模塊流程圖Fig.6 Flow chart of writing module FIFO with low speed

圖7 高速寫FIFO模塊流程圖Fig.7 Flow chart of writing module FIFO with high speed

讀FIFO模塊共有3種讀取模式:單獨讀低速FIFO,單獨讀高速FIFO,同時讀高速FIFO和低速FIFO。讀FIFO模塊是通過FPGA內部集成FIFO半滿信號觸發單片機進行讀數的,單片機檢測到FIFO半滿信號后,單片機才開始從FIFO中讀取數據,執行每次讀操作,連續從FIFO中讀取512bit數據,FIFO半滿信號是讀FIFO模塊通過比較FIFO讀寫地址的差值而對其賦值的,它的有效值為0。當寫地址與讀地址之差大于515時,FIFO半滿信號賦值為0,否則為1。利用FIFO半滿信號控制讀數過程,可以有效防止空讀和誤讀現象。

SRAM控制模塊包括寫SRAM和讀SRAM兩部分,寫SRAM是由一級緩存FIFO的半滿信號觸發的,當半滿信號有效時,開始寫SRAM。讀SRAM是通過讀FIFO模塊傳遞過來的request信號來控制的,當request信號有效時,讀取SRAM中的數據,然后將它寫入到三級FIFO,讀FIFO模塊從三級FIFO模塊中讀取數據。

4 結 論

基于現場可編程門器件(FPGA)FPGA設計的RS485數據通信協議,可以實現高速數據和低速數據接收,以及二者的同時接收。 采用專門的RS485接收芯片,在信號進入了FPGA前,進行電壓轉換。利用FPGA內部資源構建FIFO為數據接收提供緩存,并為了保證高速數據可靠接收,外部加入SRAM加大高速數據接收緩存。經過實際測試,本設計穩定可靠,能夠實現采用RS485標準的數據通信。

[1]JIA Hui-juan.Research on the Technology of RS485 over Ethernet,The International Conference on E-Product,EService and E-Entertainment (ICEEE2010)[C].Henan,China,2010:1-3.

[2]耿立中,王鵬,馬騁,等.RS485高速數據傳輸協議的設計與實現[J].清華大學學報,2008,48(8):1311-1314.GENG Li-zhong,WANG Peng,MA Pin,et al.The design and implementation of transport protocol of high-speed data[J].Journal of Tsinghua University,2008,48(8):1311-1314.

[3]NI Hai-yan,HU Chao,MA Chang-wang.Research on a 485-serial network architecture in intelligent uptown management[C]//Proc 2006 IEEE Conf on Mechatronics and Automation.Luoyang:IEEE Press,2006:400-405.

[4]B&B Electronics Mfg.Co.Inc.THE RS-485 APPLICATION“CHEAT SHEET”[EB/OL].(2012-01-01)[2012-9-03].http://www.bb-elec.com/getattachment/7045d510-a095-4064-a739-518eea017363/RS-485-Quick-Guide-Just-the-Essentials-on-a-Single.aspx

[5]李成鋼,申萍,聶曉波.基于FPGA的HDLC與RS485通信網關的設計[J].機車電傳動,2011,1(1):20-23.LI Cheng-gang,SHEN Ping,NIE Xiao-bo.The design of communication gateway between HDLC and RS485 based on FPGA[J].Electric Transmission in the Locomotive,2011,1(1):20-23.

[6]陳金華.基于HDLC協議的RS485通信設備的研制[J].測控技術,2010,29(6):98-101.CHEN Jin-hua.Research on RS485 communications equipment based on HDLC protocol[J].Measure and Control Technology,2010,29(6):98-101.

[7]QIN Shi-hong.Design of the Multi-computer communication system based on RS485[C]//2011 International Conference on Electric Information and Control Engineering(ICEICE),2011:1318-1320.

[8]GU Yong-hong,WEI Huang,YANG Qiao-li.Design and Implementation of a Multi-Channel HDLC Protocol Controller Based on FPGA[C]//2010 International Conference on Electrical Engineering and Automatic Control(ICEEAC2010),2010:266-269.

[9]BIN Huang.Design of a multi-channel high speed FIFO applied to HDLC processor based on PCI bus[C]//IEEE 2002 International Conference on Communications,Circuits and Systems and West Sino Expositions,2002:1476-1480.