非接觸式測速系統的FPGA開發

李 玲,李洋濤

(1.同濟大學鐵道與城市軌道交通研究院,上海201804;2.河南建筑職業技術學院,鄭州450007)

1 引言

DE2開發板是Altera公司針對大學教學及研究機構推出的FPGA多媒體開發平臺,為用戶提供了豐富的外設及多媒體特性,并具有靈活可靠的外圍接口設計。Terasic公司提供的針對DE2平臺的CCD攝像頭模塊以及彩色LCD模塊,可通過接口接入DE2開發板。

利用DE2開發板上的硬件資源,通過數字圖像的采集、壓縮、預處理、有用信息提取、圖像匹配和輸出結果等一系列信息處理,研制開發了一套非接觸式測速系統,包括系統構成、方案實現以及如何在FPGA中實現相關運算等等,并運用Quartus II軟件對Verilog代碼進行編譯和調試,實現了代碼的優化和處理。

2 系統構成及設計

系統設計是在Altera公司的現場可編程門陣列(FPGA)開發環境Quartus II中完成的。Quartus II軟件提供完整的多平臺設計環境,能夠直接滿足特定設計需要,為可編程芯片系統(SOPC)提供全面的設計環境。

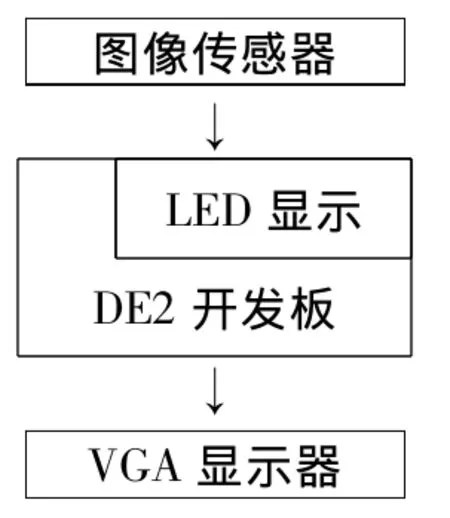

系統構成如圖1所示,圖像傳感器將采集到的數據通過接口傳送到DE2開發板,DE2實現數字圖像的壓縮、保存、識別及相關運算,最后通過VGA模塊顯示圖像效果并用DE2數碼管顯示計算結果。

圖1 系統的構成示意圖

下面對部分模塊做詳細介紹,并附錄Verilog程序代碼。

2.1 攝像頭采集模塊

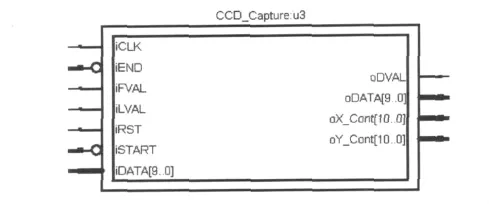

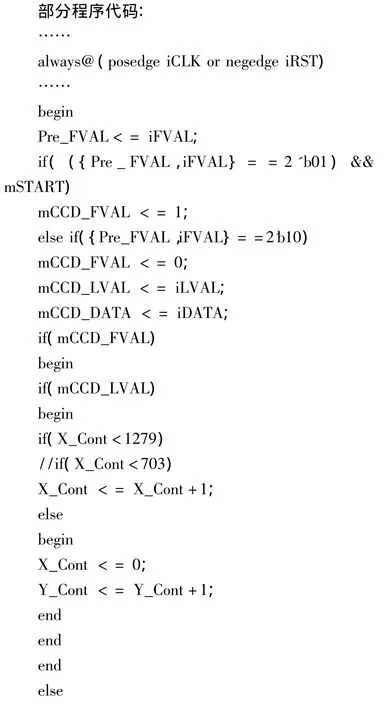

攝像頭通過DE2上的GPIO接口與開發板相連接,采用片上I2C總線的控制方式,設計I2C總線CCD控制模塊,通過片上時鐘控制,循環發送控制信號,將攝像頭采樣大小設置為1280×1024,曝光時間則通過DE2上的撥碼開關手動調節,顯示模式設置為鏡像模式,保證攝像頭拍攝的內容與顯示的內容同一方向,為后續處理提供了方便。模塊的RTL圖如圖2所示。

圖2 采集模塊的RTL圖

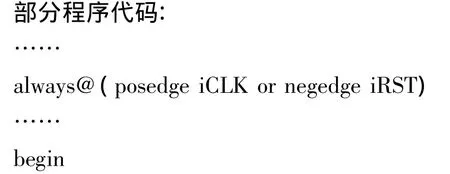

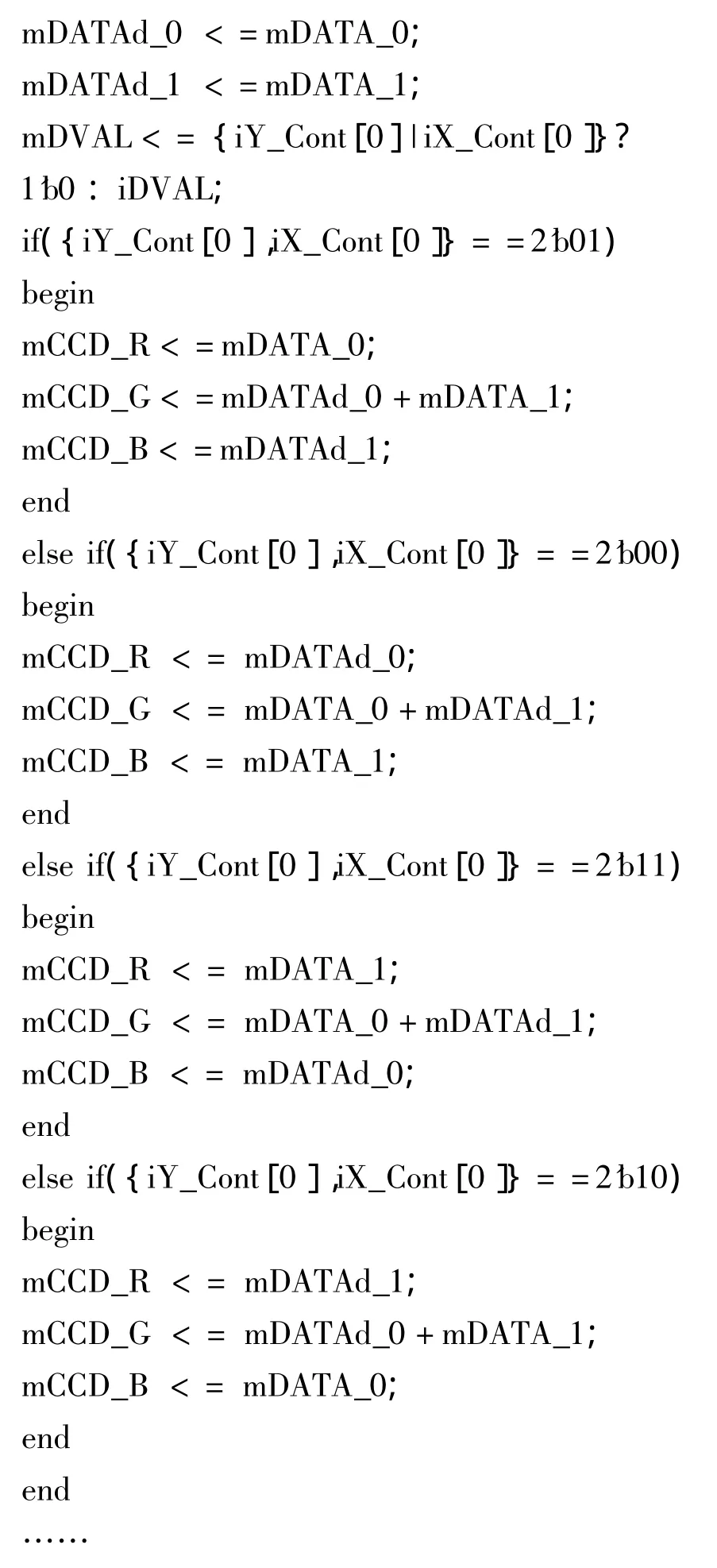

2.2 圖像數據壓縮模塊

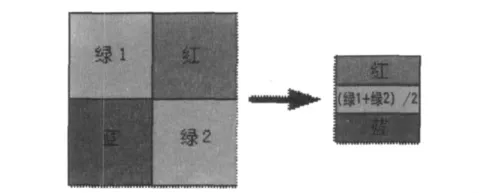

攝像頭采用的是 Bayer型 CFA(Color Filter Array,顏色濾波陣列),實際顯示一個圖像點的顏色需要四個10bit數據來表示,一幀圖像的數據為1280×1024×10bit,數據量極大。為了后續處理和顯示需要,必須對數據進行壓縮,并轉換為RGB格式,以滿足傳輸帶寬和后續處理的需要。采用插值算法,將每四個采樣象素合并為一個RGB象素點,象素值的變化如圖3所示。

圖3 象素值的變化圖

這樣經過該模塊壓縮處理后,RGB分量各使用10bit表示,圖像的分辨率變為原來的一半,即640×512,而數據量則減少到原先的四分之一。

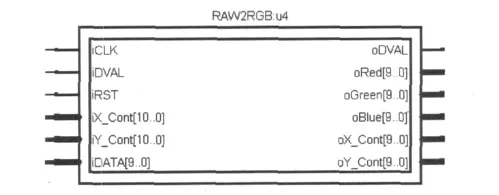

因該模塊的輸出數據,既需要量化后進行相關處理,又需要在VGA上顯示,所以需要將數據分為兩路輸出到M4KRam和SDRam端口。Cyclone II的高扇出特性,保證了扇出數據的時延和電平強度都可以直接滿足下一級處理的需要。最后設計的壓縮模塊RTL功能圖如圖4所示。

圖4 壓縮模塊的RTL功能圖

2.3 片上M4K存儲模塊

要實現相關處理需要的多次讀寫前后兩幀數據,需要使用寄存器來存放圖像的每一幀數據。由于DE2開發板上Cyclone II EP2C35的邏輯單元個數為35000個,如采用Verilog編程實現寄存器數組,如果要存放256×256×4bit的背景圖像數據,所消耗的內存邏輯單元個數過多,無法滿足需求。故必須利用片上嵌入的存儲空間來存放所需要的背景數據。

由于DE2平臺上的EP2C35僅內嵌了M4K RAM單元,所以需要通過配置級連多個M4K存儲單元,來實現背景圖像數據和檢測區間數據的存儲。EP2C35提供了104個M4K存儲單元,考慮檢測精度和算法耗時,需要配置一個256×256×4bit=256Kbit的背景寄存器來存放每一幀中背景區間的圖像。

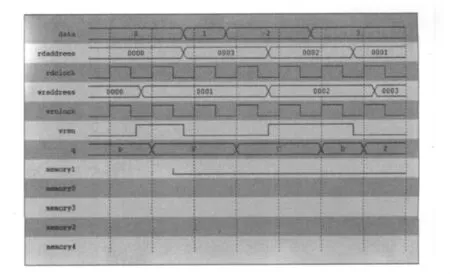

系統生成的波形圖如圖5所示。

圖5 系統生成的波形圖

完成了對256K背景寄存器的設計,只需要在設計文件中引入該.v文件,并相應在程序中使用接口,Quartus II會自動調用其內部的寄存器預設文件對程序中使用的片上內存單元進行配置。

3 實驗結果

在測試中采用的背景大小為15cm×15cm,距離檢測面40cm,測速的最大值可達到24.80cm/s。實際測量時可以設定參數來調整測量范圍,只要前后兩幀的搜索區域在速度范圍內,就可以找到最大相關,測量的速度可以成倍提高。

4 結束語

總之,針對Altera公司的DE2開發板及其第三方Terasic公司提供的針對DE2平臺的CCD攝像頭模塊,開發研究了基于FPGA的非接觸式測速系統,運用Quartus II軟件對Verilog代碼進行編譯和調試,通過試驗驗證了相關算法在FPGA上實現的可能。并部分實現了代碼的優化和處理,給出了算法實現的具體方式,達到了速度測量的目的。Verilog編程的靈活性,使得整個測速系統可以根據實際應用調整搜索區域,具有很寬的測速范圍。

[1]謝維達,王春輝,邵德榮.基于FPGA的二維相關測速方法研究[J].測控技術,2004,23(1):66 -68.

[2]張志剛.FPGA與SOPC設計教程-DE2實踐[M].西安:西安電子科技大學出版社,2007.

[3]王誠,吳繼華,范麗珍.Altera FPGA/CPLD設計(基礎篇)[M].北京:人民郵電出版社,2005.

[4]李洪偉.基于 Quartus II的 FPGA/CPLD設計[M].北京:電子工業出版社,2006.