面向ASIC 實現(xiàn)的CPA 研究平臺及其應(yīng)用

王晨旭,張凱峰,喻明艷,王進祥

1.哈爾濱工業(yè)大學(xué) 微電子中心,哈爾濱150001

2.哈爾濱工業(yè)大學(xué)(威海)微電子中心,山東 威海264209

1 引言

差分功耗分析(DPA)攻擊是一種利用密碼設(shè)備的功率消耗信息來獲取密碼設(shè)備中私密信息的攻擊方法[1]。自1999 年P(guān)aul Kocher 首次提出以來,該方法以其攻擊效率高、代價小等優(yōu)勢,給國防、安全、金融、個人信息保護等多個信息領(lǐng)域的信息安全構(gòu)成了巨大威脅,因而受到了科學(xué)界的廣泛關(guān)注。

功耗分析攻擊之所以能夠成功的破譯智能卡、密碼芯片等多種設(shè)備的密鑰,是因為在密碼設(shè)備中,設(shè)備的瞬時功率消耗與設(shè)備所處理的數(shù)據(jù)和正在執(zhí)行的操作存在相關(guān)性。為了能夠抵御功耗分析,即打破這種相關(guān)性,研究人員已經(jīng)提出了多種防御措施,例如基于環(huán)形振蕩器的抗DPA 防御措施[2]、基于掩碼技術(shù)的抗DPA 攻擊方法[3-4]、基于時鐘隨機化的防御措施[5]等。過去,對抗功耗分析攻擊效果的評估多采用對實際芯片進行功耗曲線(Power Trace)測量,然后進行攻擊。該方法雖然更有說服力,但存在兩個缺陷:一是不能在設(shè)計周期評估防御措施的效果,當芯片實測效果不理想時需要重新設(shè)計芯片,增加了設(shè)計成本,致使產(chǎn)品上市時間滯后;二是實際測量難度較大,并且由于測量噪聲的存在,需要更多的功耗曲線,這就造成了測量時間的增加,因而不適用于對抗功耗分析理論的研究。為了能夠準確快速地研究抗功耗分析攻擊的新方法,并評估各種防御措施的實際效果,一些研究人員開發(fā)了評估平臺。文獻[6]基于軟硬件協(xié)同設(shè)計和仿真的思想,開發(fā)了一款以FPGA 為載體的抗DPA 攻擊評估平臺,加速了早期設(shè)計階段的DPA 評估,但其應(yīng)用背景主要面向基于單片機軟件實現(xiàn)的密碼芯片抗攻耗分析攻擊評估。在國內(nèi),軍械工程學(xué)院的研究人員在文獻[7]中,基于LabVIEW 開發(fā)了一個針對真實硬件系統(tǒng)的評測平臺。該平臺的不足之處也是只能用于單片機軟件實現(xiàn)密碼算法的DPA 攻擊實驗或評估,而不能用于專用集成電路(Application Specific Integrated Circuit,ASIC)的DPA 防御措施的預(yù)估。清華大學(xué)的研究人員則在文獻[8]中,面向密碼芯片的ASIC 實現(xiàn),提出一種基于電路級模擬器Star-Sim 的功耗分析研究平臺。該平臺用Star-Sim 模擬出功耗曲線,然后用均值差的DPA 攻擊方式,進而評估ASIC 芯片的抗攻耗分析能力。Star-Sim 是一款晶體管級仿真器,功耗模擬結(jié)果比較精確,但是該平臺只能在設(shè)計周期的后期才能評估芯片的抗功耗分析能力,而且晶體管級仿真器的仿真速度極慢,導(dǎo)致功耗曲線的獲取效率較低,給評估工作帶來不便。相形之下,如果能夠獲取密碼芯片門級功耗曲線,則可以在設(shè)計周期的早期進行功耗分析攻擊和評估。雖然其結(jié)果不及Star-Sim 精確,但是功耗分析攻擊能否成功的關(guān)鍵不在于功耗的絕對值(即功耗準確性),而是在于單條功耗曲線不同點之間和不同功耗曲線相同點之間的相對數(shù)值。因此這種基于門級網(wǎng)表的功耗獲取方法依然有一定的實際意義,而且極快的門級功耗模擬速度必將給評估工作帶來方便。本文基于PrimeTime PX 模擬輸出的門級功耗曲線,使用MATLAB 建立CPA 攻擊平臺,通過MATLAB 建立功耗模型并計算相關(guān)系數(shù)后,再進行相應(yīng)的數(shù)據(jù)分析處理以實現(xiàn)攻擊。

2 CPA 研究平臺的設(shè)計思想

功耗分析攻擊是一種通過分析密碼設(shè)備的電流信息來獲得密鑰的方法。這種方法之所以能夠奏效,是因為密碼設(shè)備在使用不同明文進行加密的過程中,元件的翻轉(zhuǎn)次數(shù)會有所不同,這就造成了設(shè)備消耗的功耗會有微小的不同,瞬時功耗依賴于設(shè)備所處理的數(shù)據(jù)和設(shè)備所執(zhí)行的操作。

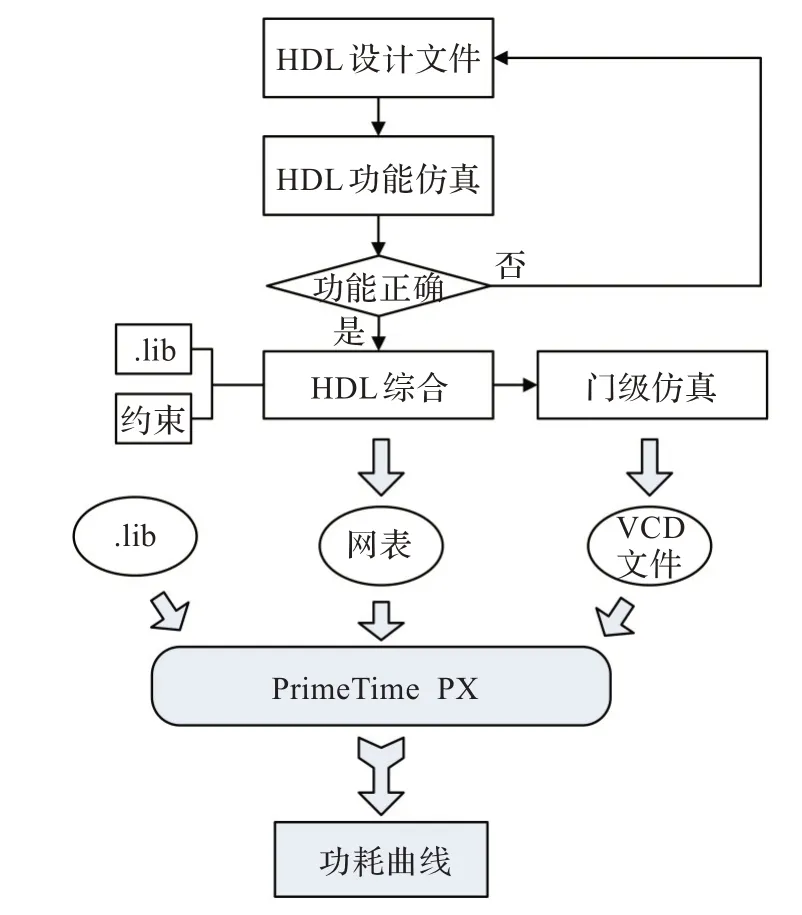

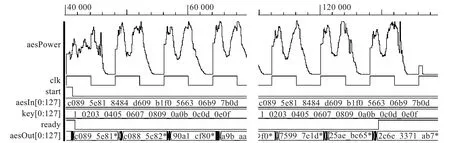

PrimeTime PX 是Synopsys公司的功耗模擬軟件,它提供了較為精確的動態(tài)和靜態(tài)功耗分析能力,可以對門級電路的功耗進行模擬,進而得出密碼芯片的功耗曲線,因此可以將其用于密碼芯片的算法級DPA 防御能力的評估。密碼算法芯片的功耗模擬過程如圖1 所示,流程如下:(1)對編寫的加密算法HDL 設(shè)計文件進行功能模擬;(2)將模擬無誤的設(shè)計文件進行邏輯綜合;(3)綜合后模擬,并記錄所用的明文和加密后的密文信息;(4)將綜合后產(chǎn)生的網(wǎng)表文件、相應(yīng)的波形文件和庫文件經(jīng)PrimeTime PX 模擬功耗,生成功耗曲線文件。重復(fù)(3)、(4)過程,完成多組功耗曲線的測量。圖2 給出了使用PrimeTime PX 模擬出的AES 算法功耗曲線直觀效果圖。

圖1 PrimeTime PX 功耗模擬流程圖

在使用PrimeTime PX 快速準確地得出功耗曲線之后,為了能夠達到攻擊的目的,通過MATLAB 建立功耗模型并計算相關(guān)系數(shù)后,再進行相應(yīng)的數(shù)據(jù)分析處理,如圖3所示。

使用MATLAB進行CPA攻擊,按照以下5個步驟進行[4]:

(1)選擇所執(zhí)行算法的某個中間值。這個中間值必須是一個函數(shù)f(d,k),其中d 是已知的非常量數(shù)據(jù),一般為加密算法的明文或密文,k 是密鑰的一小部分。

(2)使用PrimeTime PX 模擬密碼設(shè)備加密或解密D個不同數(shù)據(jù)分組時的功耗,產(chǎn)生一個D×T 的功耗曲線矩陣T 。

(3)對每一假設(shè)的k 值計算對應(yīng)的中間值,對所有D次加密和所有K 個密鑰假設(shè),可以得到一個D×K 的中間值矩陣V,V 中的每一個元素vij=f(di,kj)。

圖2 PrimeTime PX 模擬出的AES 功耗曲線圖

圖3 CPA 攻擊研究平臺的實現(xiàn)方式

(4)根據(jù)元件輸出翻轉(zhuǎn)次數(shù)的變化,利用漢明距離模型,將矩陣vij映射為D×K的功耗值矩陣H。

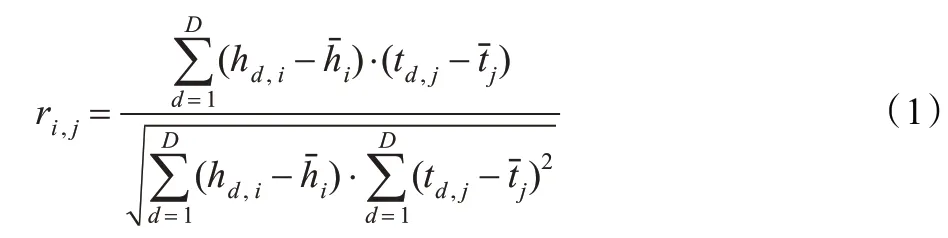

(5)對假設(shè)功耗值和模擬出的能量值進行相關(guān)系數(shù)分析。相關(guān)系數(shù)是表征向量之間線性關(guān)系緊密程度的量,其計算公式如公式(1)。計算H矩陣的每一列hi和矩陣T的每一列tj的相關(guān)系數(shù)ri,j,得到一個K×T的矩陣R。

最大的相關(guān)系數(shù)表征了實際功耗和功耗模型的最相關(guān),這樣,矩陣R中的最大值的索引即為所選擇的中間值進行處理的位置和設(shè)備所使用的密鑰。

3 平臺應(yīng)用研究與實驗結(jié)果分析

3.1 普通AES 實現(xiàn)方式的CPA 攻擊

高級加密標準(Advanced Encryption Standard,AES)作為傳統(tǒng)對稱加密算法DES 加密標準的替代者,由美國國家標準與技術(shù)研究所(NIST)于2001 年12 月發(fā)布。AES 的最后一輪運算過程如圖4 所示,明文經(jīng)前9 輪的運算,得到128 位的中間結(jié)果,該結(jié)果經(jīng)由SubBytes、ShiftRows、AddRoundKey 運算過程后得到最終的密文結(jié)果cipher。

圖4 AES 最后輪抽象框圖

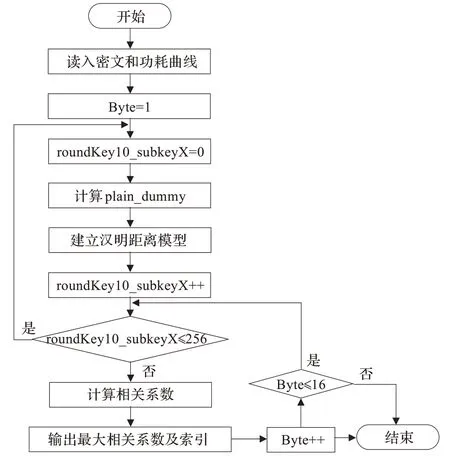

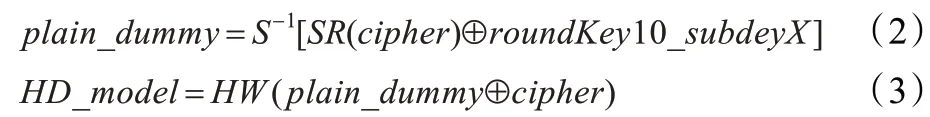

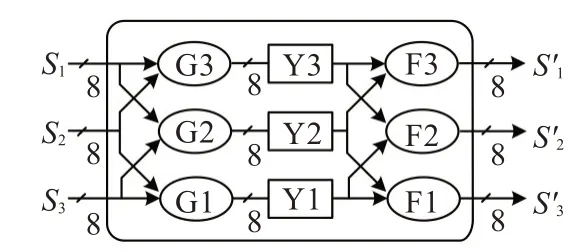

選用密文攻擊的方式,對AES 算法最后輪的輪密鑰roundKey10 的每個字節(jié)逐個實施攻擊,通過已知的密文按式(2)計算出plain_dummy,S-1 代表SubByte 的逆運算,SR表示ShiftRows 運算;利用漢明距離模型,按式(3)刻畫假設(shè)功耗,并與PrimeTime PX 產(chǎn)生的功耗數(shù)據(jù)進行相關(guān)系數(shù)的計算,完成攻擊。圖5 為MATLAB 程序攻擊AES 的流程圖。

圖5 MATLAB 攻擊AES 的流程圖

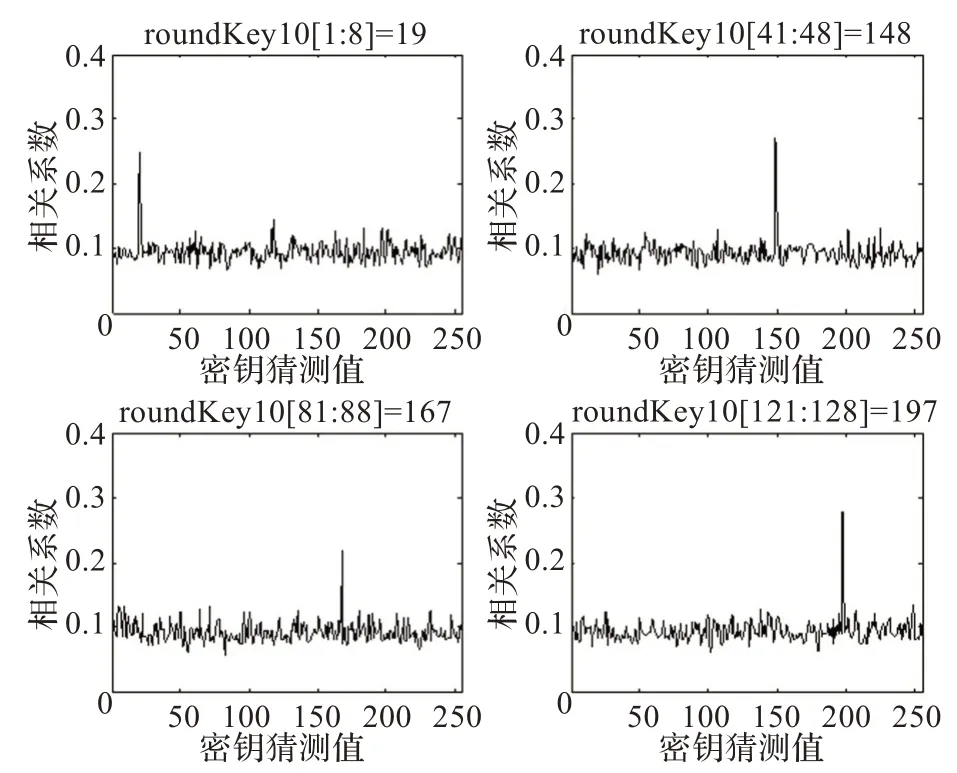

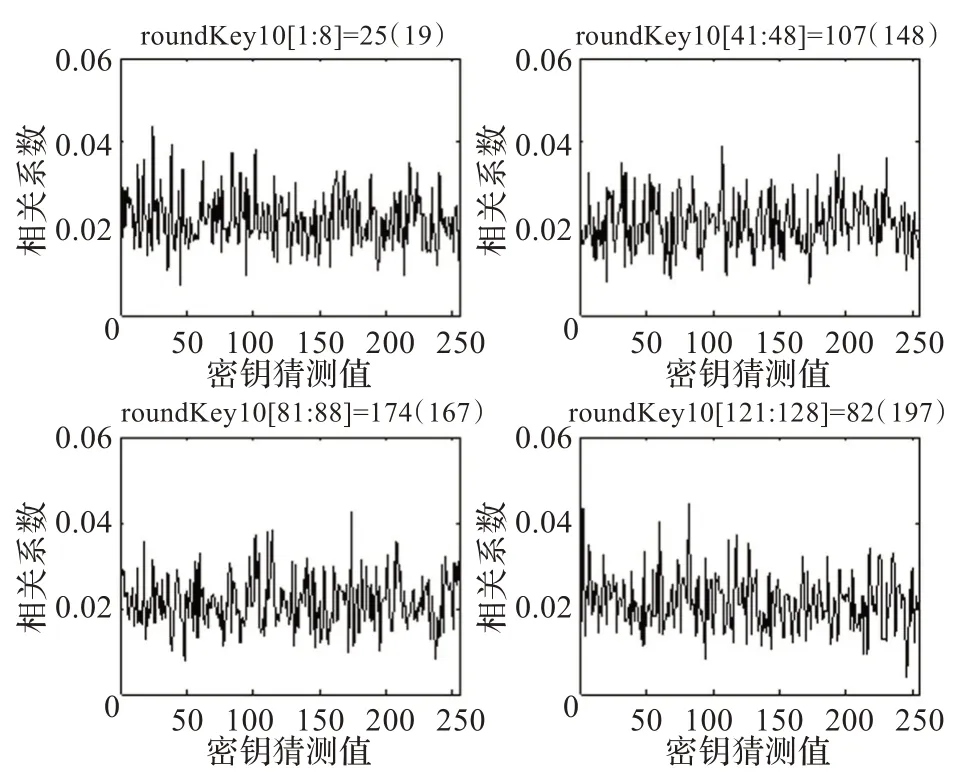

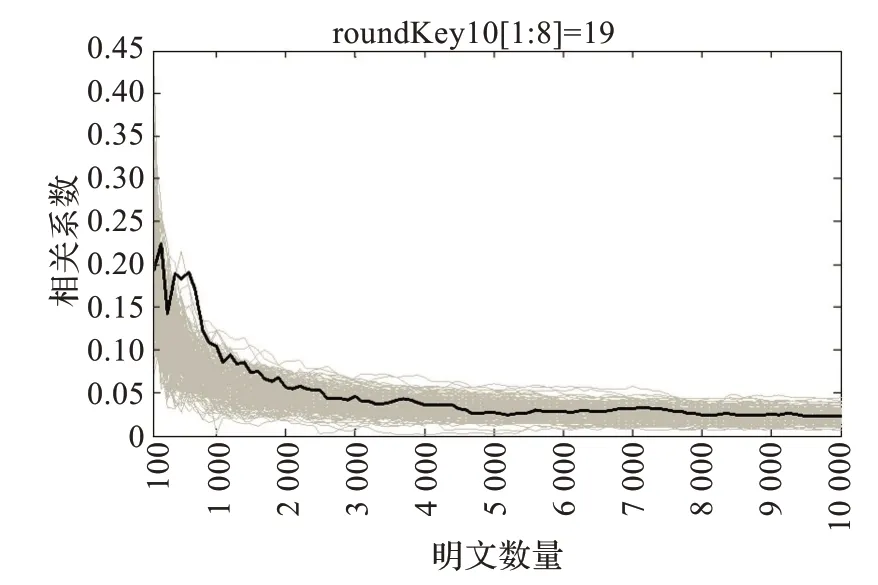

攻擊過程中采用700 條功耗曲線,針對第10 輪的輪密鑰roundKey10 中的每8 位,找出0 到255 每個密鑰猜測值的最大相關(guān)系數(shù),如圖6 所示。限于篇幅,圖6 中只包含4個子圖,每個子圖表示對roundKey10 其中8 位的攻擊結(jié)果,橫軸為密鑰猜測值(0~255),縱軸為相關(guān)系數(shù)。以第3個子圖為例,相關(guān)系數(shù)在猜測值為167 時出現(xiàn)最高尖峰,故roundKey10 的第81 到88 位推測應(yīng)為10100111。圖7 給出了功耗曲線數(shù)量對roundKey10[81:88]相關(guān)系數(shù)的影響,其中處于上方的曲線為真實密鑰時的情況。可以看出,隨著樣本數(shù)量的增加,正確密鑰猜測值與錯誤密鑰猜測值相關(guān)系數(shù)的區(qū)別不斷加大。

3.2 Threshold 防御措施CPA 攻擊結(jié)果

圖6 相關(guān)系數(shù)與密鑰猜測值之間的關(guān)系

圖7 相關(guān)系數(shù)與樣本數(shù)量的關(guān)系

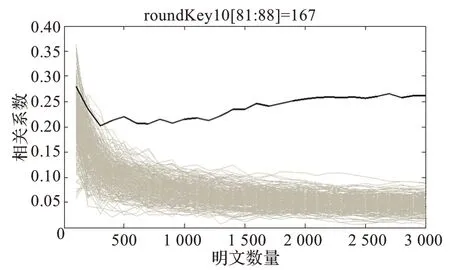

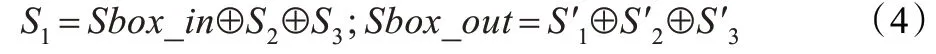

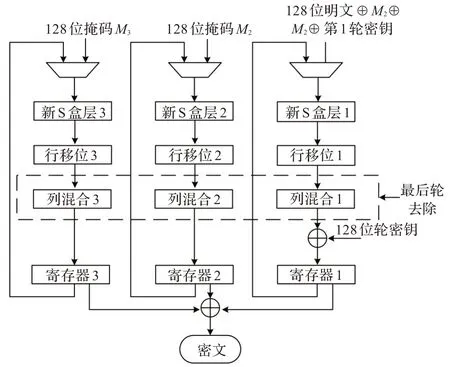

Threshold 技術(shù)是一種秘密分享(Secret Sharing)思想,它的基本思想是將原先的單數(shù)據(jù)通路拆分成N條數(shù)據(jù)通路(為了達到面積和復(fù)雜度的折衷,N一般取3),任何一條數(shù)據(jù)通路只攜帶1/N 的有用信息,這就給功耗分析攻擊增加了難度[9]。目前已有采用這種技術(shù)的有效ASIC 芯片報道,文獻[10]采用了串行化實現(xiàn)方式成功將Threshold 思想應(yīng)用于PRESENT 密碼算法,并取得了滿意的結(jié)果。為了評估Threshold 思想在AES 中的應(yīng)用效果,基于Nikova 提出的Threshold 的思想重新設(shè)計了AES 算法。像其他掩碼技術(shù)一樣,Threshold 實現(xiàn)的難點在于非線性S 盒的實現(xiàn)。圖8 是本文完成的基于Threshold 思想的AES 的S 盒實現(xiàn)方式(N=3),假設(shè)AES 算法原始S 盒輸入輸出分別為Sbox_in 和Sbox_out,Threshold 型S 盒滿足等式(4)。由于Threshold 型S 盒包含了3 個平行的數(shù)據(jù)通路,與之相對應(yīng),AES 的其他運算和存儲單元也需要3 條平行通路,如圖9所示。

圖8 Threshold 型S 盒 結(jié)構(gòu)

對完成的Threshold 型AES 設(shè)計采用與3.1 節(jié)中相同的明文產(chǎn)生的功耗曲線進行密鑰破解。攻擊過程中采用10 000條功耗曲線,攻擊結(jié)果如圖10 所示。限于篇幅,圖10 中只包含4 個子圖,每個子圖表示對roundKey10 其中8 位的攻擊結(jié)果。橫軸為密鑰猜測值(0~255),縱軸為相關(guān)系數(shù)。子圖的標題中包含了本段子密鑰攻擊密鑰值和實際密鑰值。以第3 個子圖為例,本段子密鑰的攻擊值為174,而實際的密鑰值為167,說明10 000 條明文并沒有成功攻擊本段子密鑰。從圖中還可以看出,相關(guān)系數(shù)的值都非常小,正確的密鑰值并沒有明顯的尖峰存在,所有的密鑰都未被破解。

圖9 Threshold 型AES 算法明文數(shù)據(jù)通路

圖10 Threshold 型相關(guān)系數(shù)與密鑰猜測值之間的關(guān)系

圖11給出了功耗曲線數(shù)量不同時,對第一個字節(jié)的各個猜測密鑰相關(guān)系數(shù)的變化(其中黑色為真實密鑰),可以看出當功耗曲線的數(shù)量達到10 000 條時真實密鑰未能從其余密鑰猜測中分離開來,密鑰破解仍然沒有成功。由此可以看出,基于Threshold 的AES 算法實現(xiàn)可以很好地抵御所使用的一階針對觸發(fā)器的差分功耗分析攻擊。

4 結(jié)束語

圖11 Threshold 型AES 實現(xiàn)的相關(guān)系數(shù)與樣本數(shù)量的關(guān)系

搭建功耗分析攻擊平臺是研究抗攻耗分析攻擊理論首當其沖的問題,本文針對現(xiàn)有的功耗分析攻擊平臺的一些不足,設(shè)計出一種面向ASIC 設(shè)計實現(xiàn)的CPA 研究平臺。該平臺可以摒棄示波器等設(shè)備的昂貴價格和測試帶來的不便,能夠在芯片設(shè)計周期早期快速模擬出芯片的功耗信息并實施CPA 攻擊,這為開拓及評估抗功耗分析的新方法提供了便利,也為抗攻耗分析攻擊理論研究提供了重要支持。作為應(yīng)用,利用本文平臺分別對AES 算法和帶有Threshold 防御措施的AES 算法進行了功耗分析攻擊實驗,展示了該平臺的有效性和便捷性。下一步,準備對AES 的上述兩種實現(xiàn)方式進行版圖后的功耗分析攻擊實驗,以進一步印證該輔助平臺的有效性。

[1] Kochet P,Jaffe J,Jun B.Differential power analysis[C]//Advances in Cryptology(CRYPTO’99).Berlin:Springer-Verlag,1999,1666:388-397.

[2] Liu P C,Chang H C,Lee C Y.A low overhead DPA countermeasure circuit based on ring oscillators[J].IEEE Transactions on Circuits and Systems-II,2010,57(7):547-550.

[3] Akkar M,Giraud C.An implementation of DES and AES,secure against some attacks[C]//Proceedings of Cryptographic Hardware and Embedded Systems,Paris,F(xiàn)rance,May 14-16.Berlin:Springer-Verlag,2001,2162:309-318.

[4] Rivain M,Prouff E.Provably secure higher-order masking of AES[C]//Proceedings of Cryptographic Hardware and Embedded Systems,Santa Barbara,USA,August 17-20.Berlin:Springer-Verlag,2010,6225:413-427.

[5] Mangard S,Oswald E,Popp T.Power analysis attacks:revealing the secrets of smart cards[M].Berlin:Springer-Verlag,2007:173-175.

[6] Krieg A,Bachmann B,Grinschgl J,et al.Accelerating early design phase differential power analysis using power emulation techniques[C]//Proceedings of the IEEE International Symposium on Hardware-Oriented Security and Trust,San Francisco,California,USA,June 5-6,2011:81-86.

[7] 褚杰,趙強,丁國良.基于虛擬儀器的差分功耗分析攻擊平臺[J].電子測量與儀器學(xué)報,2008,22(5):123-126.

[8] 劉鳴,陳弘毅,白國強.功耗分析研究平臺及其應(yīng)用[J].微電子學(xué)與計算機,2005,22(7):134-138.

[9] Nikova S,Rijmen V,Schl?ffer M,Secure hardware implementations of non-linear functions in the presence of glitches[C]//Proceedings of International Conference on Information Security and Cryptology,Seoul,Korea,December 3-5.Berlin:Springer-Verlag,2008,5461:218-234.

[10] Poschmann A,Moradi A,Khoo K.Side-channel resistant crypto for less than 2300 GE[J].Journal of Cryptology,2011,24(2):322-345.