基于ARM和FPGA的智能變電站全場景試驗裝置硬件平臺設計

吳 杰,黃 琦,井 實,王 彪,張 華

(1.電力系統廣域測量與控制四川省重點實驗室,四川成都 611731;2.電子科技大學能源科學與工程學院,四川成都 611731;3.四川電力科學研究院,四川 成都 610072)

0 引言

根據國家電網公司規(guī)劃,近些年國內將新建大量智能變電站。相對于傳統變電站,智能變電站放棄了原有以電纜為媒介傳輸電氣信號的方式,轉而采用光纖數字化方式傳輸運行信息。于是,電子式互感器、合并器、交換機等數字化設備大量出現在智能變電站中,這給變電站信息的接入、分配帶來靈活性,提高了變電站內部信息交換能力和處理數據的能力,為實現變電站智能化創(chuàng)造了先決條件,同時這也使變電站繼電保護試驗趨于復雜化,由此加大了二次側調試的難度[1]。

變電站二次設備現場試驗的目的是對變電站繼電保護設備、測量控制設備、安全自動裝置等設備的功能和技術指標進行驗證。按照傳統試驗,繼電保護測試儀將電壓、電流量按照IEC 61850協議打包后傳送給保護裝置,缺乏測試的整體性,即,測試環(huán)節(jié)不包括合并單元。因此,研究適用于智能變電站條件下的新調試方法及檢測裝置迫在眉睫。

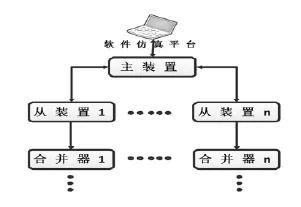

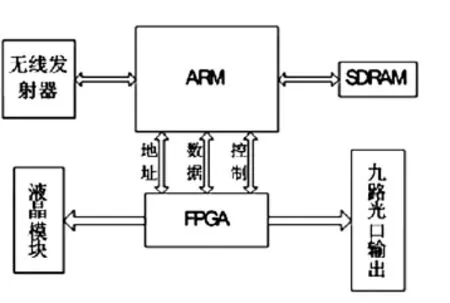

針對繼電保護試驗新方法,根據IEC 60044-8、IEC 61850 -9 -1/2[2,3]標準對合并單元的規(guī)定,在此基礎上提出一種基于ARM高級RISC微處理器(advanced RISC machines,ARM)和FPGA現場可編程門陣列(field-programmable gate array,FPGA)協同工作的智能變電站全場景實驗裝置硬件平臺[4,5]。如圖1所示,該系統含有1套主裝置和多套從裝置,以及能夠仿真變電站各種故障的軟件平臺,可真實地模擬一次側采集器到二次側合并單元的過程,完成變電站全站的一次繼電保護試驗過程,以檢驗主控室內合并單元、繼電保護設備、測控設備等的配置、性能指標以及信息的組織與分配的正確性。

圖1 全場景試驗平臺

1 全場景試驗硬件平臺設計

1.1 硬件平臺方案

硬件系統框圖如圖2所示,分為主系統和從系統兩部分。該系統可以完成無線同步對時和無線同步發(fā)送仿真數據的功能。

無線同步對時部分的設計是考慮到兩個原因。其一降低現場調試環(huán)境的復雜程度,系統同步對時和發(fā)送數據均采用無線方式,從而減少了多條網線和GPS天線的連接;其二為了模擬智能變電站全場景實驗,一次需要多個從裝置給多個合并單元同時輸入仿真數據量。

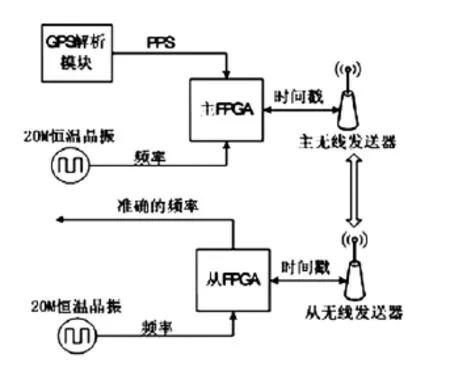

系統的主硬件平臺包括GPS解析模塊、時間同步模塊。GPS解析模塊完成接收GPS信號、解析時間、為時間同步模塊提供標準時間的任務。于是,利用恒溫晶振的短期運行穩(wěn)定和GPS的長期運行穩(wěn)定的特點,使二者共同為主硬件平臺提供時間基準,有效地防止時鐘模塊產生積累誤差和隨機誤差的產生;時間同步模塊實現與從硬件平臺時間同步的功能,在整個系統中,起著標準時鐘源的作用。

從硬件平臺包括數據接收模塊、數據發(fā)送模塊、時間同步模塊。數據接收模塊處理、存儲通過無線網絡接收到的軟件平臺仿真數據;數據發(fā)送模塊提取數據接收模塊中的數據,編碼以后通過電光轉換模塊發(fā)送給合并單元和液晶顯示模塊;時間同步模塊以無線網絡為傳輸介質,采用能到達μs級的IEEE 1588協議與主時間同步模塊進行同步對時。

由于ARM具有強大的數據處理能力,FPGA擁有豐富的I/O資源和快速的并行處理能力[7],硬件平臺采用二者協同工作的方案。ARM處理器主要負責接收軟件平臺的仿真數據以及對數據通道分配處理;FPGA處理器主要負責IEEE 1588同步對時,以及按照特定協議將來自ARM處理器的數據重新編碼后發(fā)送給合并單元。

圖2 硬件平臺功能圖

1.2 無線通信

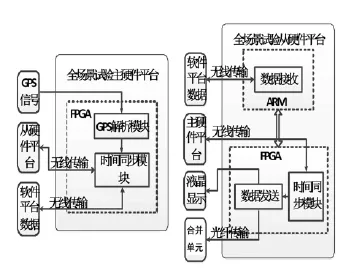

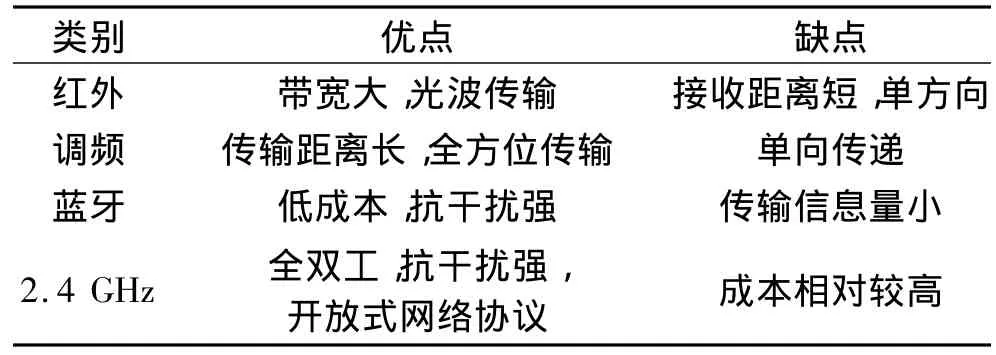

硬件系統是通過無線的方式進行數據的接受和IEEE 1588同步對時,所以在設計其他模塊之前,選擇一種合適的無線傳輸技術至關重要,常見的無線傳輸技術有紅外、調頻、藍牙、2.4 GHz等。為了選取合適的傳輸介質,將上述幾種無線傳輸技術的優(yōu)缺點歸納到表1中。

表1 常見無線傳輸技術優(yōu)缺點

根據IEEE 1588協議標準[8],傳輸介質需要支持雙向信號傳輸,才能實現同步對時功能;而且從硬件平臺也要和軟件仿真平臺通信,需要支持全雙工的傳輸介質,因此,選擇2.4 GHz WLAN無線網絡作為數據收發(fā)和IEEE 1588對時的傳輸介質,它有支持全雙工、開放式協議的優(yōu)點[9,10]。無線發(fā)射終端采用支持802.11 b/g/n無線標準的網橋,具有體積小、發(fā)射功率大、功耗低、組網方便、能顯示網中任意子網絡的接收功率的特點,為平臺快速組件傳輸網絡提供了方便。

數據接收模塊需要配置以太網接口,以完成嵌入式操作系統與網橋之間的以太網通信。由于AT91RM9200處理器內部集成有 MAC(medium/media access control,介質訪問控制)層,因此外部只需配置一塊完全集成的和符合成本效益的快速以太網PHY(physical layer,物理層)芯片即可;同樣FPGA處理器也需要配置以太網口和PHY層來完成到無線網橋的通信過程。

1.3 數據收發(fā)模塊

數據接收模塊通過無線網絡接收軟件仿真平臺仿真數據,處理以后存入雙口RAM中。當收到軟件平臺的發(fā)送數據指令以后,數據發(fā)送模塊通過控制總線請求數據接收模塊讀取雙口RAM中的數據,然后處理讀取的數據并發(fā)送給液晶顯示屏和合并單元。數據接發(fā)模塊設計框圖如圖3所示。

圖3 數據接發(fā)模塊框圖

ARM處理器接收軟件平臺通過無線網絡發(fā)送來的數據,經過CRC校驗、分配9路輸出數據通道后,經數據總線存入2片8 MB的雙口RAM中。數據發(fā)送模塊和數據接收模塊通過雙口RAM進行數據交互,每次從一塊雙口RAM中提取半個周波的數據到數據接收模塊進行編碼,將其按照特定協議轉換成合并單元能夠識別的9路電信號,然后以時鐘同步模塊提供的準確時間為基準,將電信號傳輸給電光轉換模塊。

電光轉換模塊具有傳輸帶寬高、抗干擾性能強、信號穩(wěn)定、無誤碼率的要求,以保證合并單元接收到正確的光信號。

1.4 時鐘同步模塊

為了實現同步對時,時鐘同步模塊由主同步模塊和從同步模塊構成。作為整個硬件平臺的時鐘標準,主時鐘同步模塊需要高精度的GPS作為時間標準,以確保自身時鐘的準確性,然后在與從時鐘模塊完成IEEE 1588同步對時,同時主時鐘內部還裝有一個高精度的恒溫晶振,彌補GPS失效時不能給從時鐘模塊提供精準時間的缺陷;各從同步模塊依次同主時鐘模塊進行IEEE 1588對時,等全部同步對時完成以后,完成主時鐘模塊、從時鐘模塊、GPS三者同步的目的。于是各從硬件平臺同步給合并單元發(fā)送仿真數據,保證了合并單元要求的接收數據時間延遲。具體框圖見圖4。

圖4 時鐘同步模塊

GPS解析模塊具有體積較小、誤差小、功耗小、易集成到裝置中、支持紐扣電池供電等優(yōu)點。當收到GPS解析模塊解析出來的時間信息和產生的PPS(pulse per second,秒脈沖)信號,主時鐘模塊利用PLL(phase locked loop,鎖相環(huán))將20 MHz頻率倍頻到50 MHz后,將產生PPS信號與GPS產生的PPS比對,然后修正自身的時鐘;從同步模塊是由20 MHz的恒溫晶振、FPGA處理器以及PHY層等構成。按照IEEE 1588的標準,從同步模塊與主同步模塊對時,直到同步到主時鐘上然后給數據發(fā)送模塊提供時間依據,確保各個合并單元收到的數據延遲都在指標內。

2 系統測試與驗證

2.1 實驗平臺

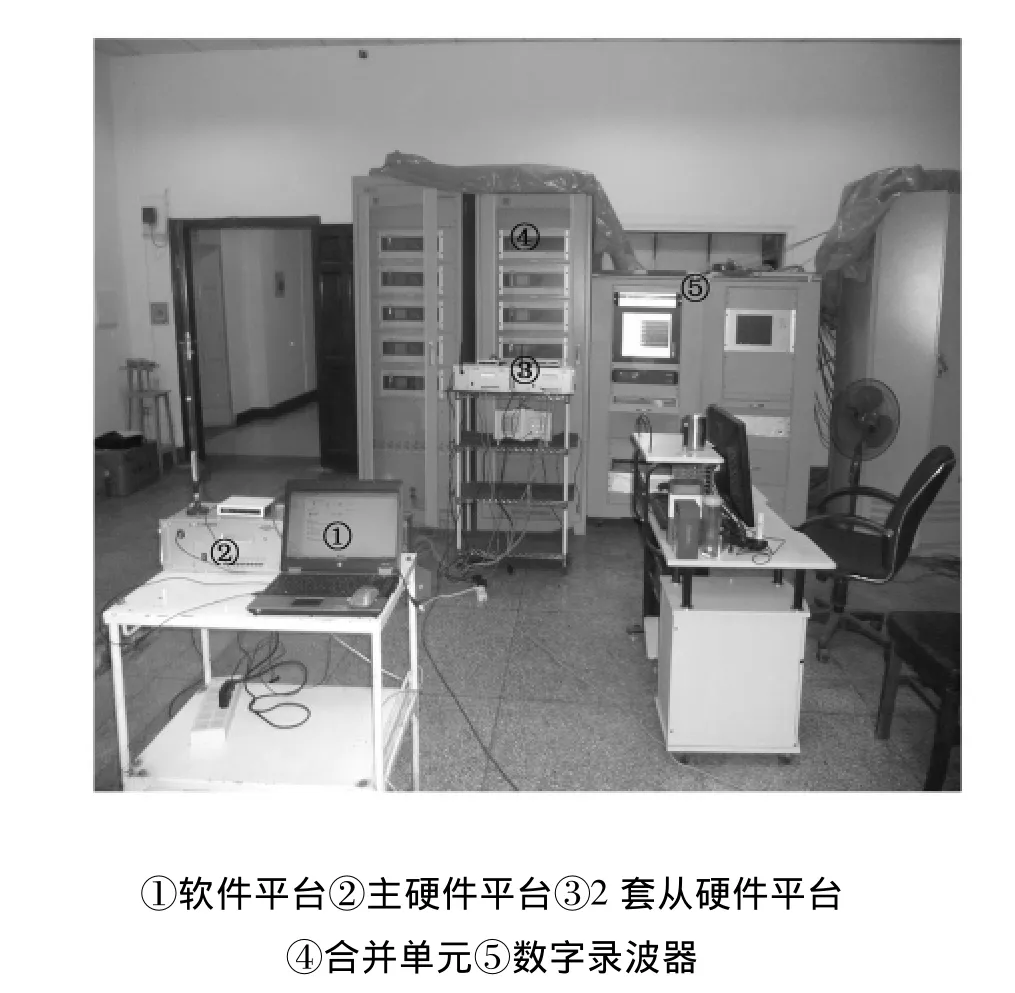

為簡單、快捷、有效地驗證硬件平臺功能,選取一套主裝置和兩套從裝置,在實驗室模擬智能變電站實際情況,分別給綿陽線和赤化線的兩個合并單元發(fā)送仿真平臺的模擬互感器的數據量。實驗環(huán)境如圖5所示,驗證硬件平臺能否將軟件平臺的仿真數據準確無誤地發(fā)送給合并單元的功能,同時檢驗兩個從硬件平臺的同步效果。

首先,通過無線網絡,軟件平臺將事先仿真的赤化線上CA相間短路數據發(fā)送給兩臺從硬件平臺,然后主平臺依次同兩個從硬件平臺完成IEEE 1588同步對時,最后在得到仿真軟件下發(fā)的仿真實驗開始指令后,兩個硬件平臺通過光纖將存儲的數據發(fā)送給各自的合并單元。當接收到合并單元發(fā)送來帶有故障信息的報文時,數字錄波器記錄下合并單元輸出的一次側電流、電壓以及相角值。通過分析仿真軟件的波形文件和數字錄波器上錄制的波形文件,可以檢驗該套硬件平臺方案的可行性。

圖5 模擬現場實驗

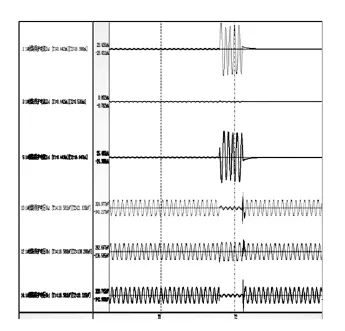

圖6 軟件平臺仿真CA相間接地短路波形

2.2 數據接發(fā)模塊

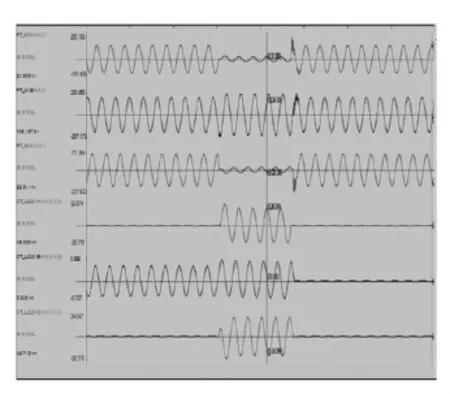

通過比對仿真軟件的波形和數字錄波器上錄制的波形,可以定性和定量地驗證硬件平臺數據接收模塊和數據發(fā)送模塊的正確性。圖6是軟件平臺仿真出來的CA兩相接地短路波形;圖7為數字錄波器錄制的合并單元輸出的波形。

由圖6可以看出,CA相間短路故障在0.6 s時刻發(fā)生,持續(xù)0.1 s(5個周波)后,在0.7 s時刻結束。

圖7 錄波器顯示CA相間接地波形

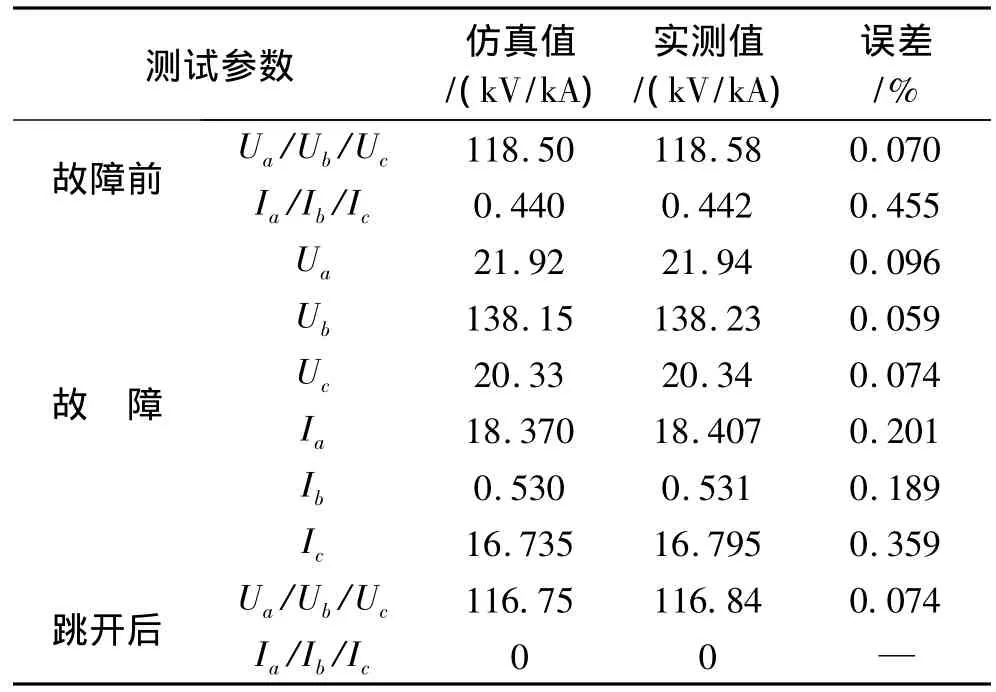

由圖7可以看出,數字錄波器顯示的波形也是在0.6 s時刻發(fā)生CA相間故障,持續(xù)5個周波以后,在0.7 s時刻結束故障,恢復穩(wěn)定態(tài),正確地重現CA相間短路故障的波形,且故障前、故障中、故障后的波形和圖4基本一致,定性驗證硬件平臺數據發(fā)送和數據接收模塊的正確性。為定量說明,將仿真平臺的仿真數據和數字錄波器上讀取的實驗數據列入表2中。

由表2可得,在整個仿真過程中,軟件平臺仿真數值和數字錄波器得到的數值誤差均在1%以內,滿足實驗要求,定性地驗證硬件平臺傳輸數據的能力。

表2 錄波器與仿真平臺的電壓/電流數值

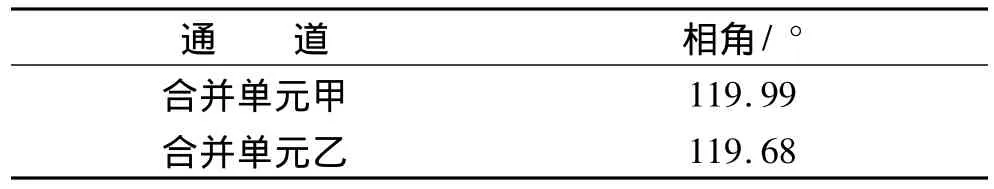

2.3 時鐘同步效果

通過數字錄波器比較兩條線路B相保護電流的相角,可以估算出兩套從硬件平臺之間的時間同步誤差。數字錄波器默認將A相電流通道作為其余通道的基準,故設為 0.00°。

表3 錄波器顯示的相角量

分析表3數據,兩條線路的B相保護電流相角為0.31°。按照一個周期20 ms計算,將相角差轉換成時間差得17 μs,而合并單元是按照250 μs的周期接收數據,所以平臺實現的同步對時指標遠遠滿足要求。

3 結語

提出了一種基于FPGA和ARM處理器協同工作的智能變電站全場景實驗硬件平臺方案。經實驗驗證,該套硬件平臺能準確接收和發(fā)送數據,無線同步對時效果達到20 μs以內,為智能變電站二次側繼電保護試驗新方法提供了一種可操作的硬件平臺。

[1]Q/GDW 383-2009,智能變電站技術導則[S].2009:4-7.

[2]IEC 61850,Communication Networks and Systems in Substations[S].

[3]IEC 60044 - 8,Instrument Transformers Part:Electronic Current Transformers[S].

[4]張明珠,鄒欣潔.基于FPGA&ARM9合并單元的研制[J].電力系統保護與控制,2010(9):84-87.

[5]Jingmeng Liu,Wheihai Chen,Tianmiao Wang,et al.Hardware Circuit Design of NC System Based on ARM and FPGA[C].The IEEE International Conference on Industrial Informatics(INDIN 2008)DCC,Daejeon,Korea,2008.

[6]朱超,黃燦,梅軍,等.基于FPGA與ARM的智能合并單元設計[J].電網技術,2010,6(8):84 -87.

[7]盧祥弘,陳儒軍,何展翔.基于FPGA的恒溫晶振頻率校準系統的設計[J].電子技術應用,2010(7):104-107.

[8]IEEE Std 1588 -2008,IEEE Standard for a precision Clock Synchronization Protocol for Networked Measurement and Control Systems[S].

[9]T.Cooklev,J.C.Eidson and A.Pakdaman.An Implementation of IEEE 1588 over IEEE 802.11b for Synchronization of Wireless Local Area Network Nodes[J].IEEE Transactions on Instrumentation and Measurement,2007,23(2):1632-1639.

[10]Aneeq Mahmood and Feorg Gaderer.Timestamping for IEEE 1588 based Clock Synchronization in Wireless LAN[J].International IEEE Symposium on Precision Clock Synchronization for Measurement,Control and Communication Brescia,2009,21(1):12-16.