一種FPGA驗(yàn)證與測(cè)試方法介紹

張凱虹,陳 誠(chéng),萬(wàn)書(shū)芹

(中國(guó)電子科技集團(tuán)公司第58研究所,江蘇 無(wú)錫 214035)

1 引言

FPGA是電子設(shè)計(jì)領(lǐng)域中最具活力和發(fā)展前途的一項(xiàng)技術(shù)。隨著它的廣泛應(yīng)用,其可靠性變得越來(lái)越突出,電子元器件可靠性試驗(yàn)和篩選越來(lái)越重要。測(cè)試已成為制約FPGA實(shí)際應(yīng)用的一個(gè)關(guān)鍵因素[1]。

基于ATE的FPGA測(cè)試的關(guān)鍵是如何生成對(duì)FPGA進(jìn)行配置的測(cè)試向量,特別是不依賴于產(chǎn)品設(shè)計(jì)的條件下。本文基于PC、ATE與自制轉(zhuǎn)換軟件,對(duì)FPGA驗(yàn)證與測(cè)試開(kāi)發(fā)技術(shù)進(jìn)行研究。通過(guò)對(duì)FPGA的實(shí)際測(cè)試,達(dá)到了很好的效果,證明了實(shí)用性。

2 生成對(duì)FPGA進(jìn)行配置的測(cè)試向量

一般實(shí)現(xiàn)FPGA配置的方式有兩種,一種是將配置文件存放在FPGA外的PROM或EPROM中,系統(tǒng)加電后配置文件自動(dòng)加載到SRAM中;另一種是將測(cè)試系統(tǒng)用作一個(gè)處理器,通過(guò)數(shù)字通道將配置數(shù)據(jù)加載到SRAM中[2]。本文采用第二種方法實(shí)現(xiàn)FPGA的在線配置。

2.1 配置模式

FPGA根據(jù)配置模式管腳(M0、M1、M2)的不同輸入,產(chǎn)生8種配置模式[3]。由于測(cè)試FPGA的過(guò)程中需要多次“配置-測(cè)試”過(guò)程,其中配置占用時(shí)間相對(duì)比較長(zhǎng)。從并模式的數(shù)據(jù)寬度為8位,與其他配置模式相比速度快8倍,所以選用從并作為測(cè)試配置模式。此模式為系統(tǒng)加載FPGA配置程序提供了最簡(jiǎn)單的接口。數(shù)據(jù)D0~D7和時(shí)鐘CCLK可同時(shí)從外部提供。

2.2 配置數(shù)據(jù)格式

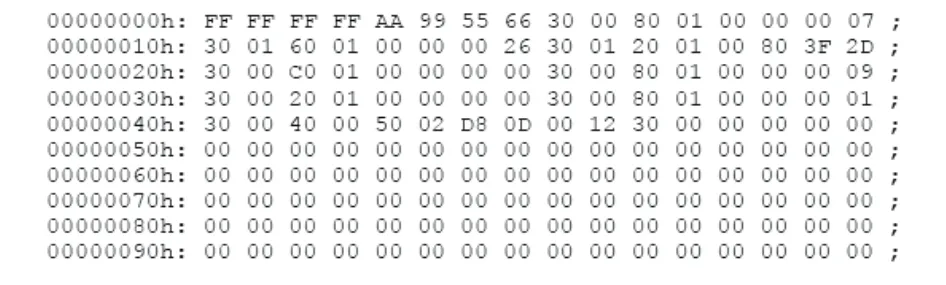

配置比特流是由ISE調(diào)用BitGen程序把布局布線后的約束文件轉(zhuǎn)換為二進(jìn)制文件,由于FPGA可能的配置文件有五種[4],其中bin的二進(jìn)制文件不僅可用于定制的配置方案還可存儲(chǔ)于第三方PROM,符合本測(cè)試方案要求。圖1是bin二進(jìn)制文件。該類(lèi)文件不含文件頭信息。0Xaa995566是同步字,0X30008001是器件ID,之后數(shù)據(jù)為配置幀。

圖1 FPGA.bin配置文件

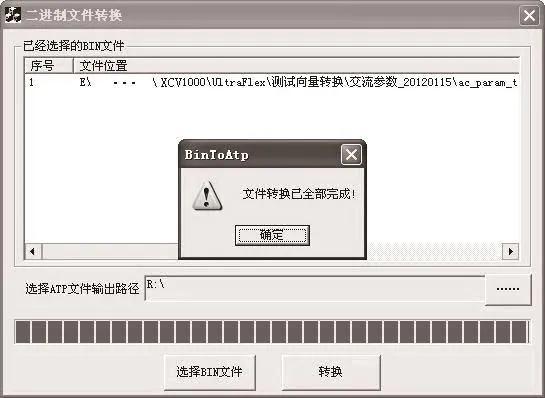

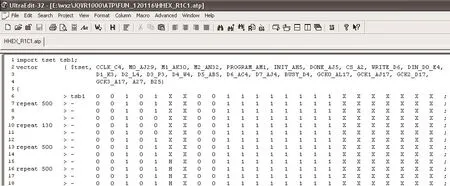

2.3 配置數(shù)據(jù)轉(zhuǎn)換

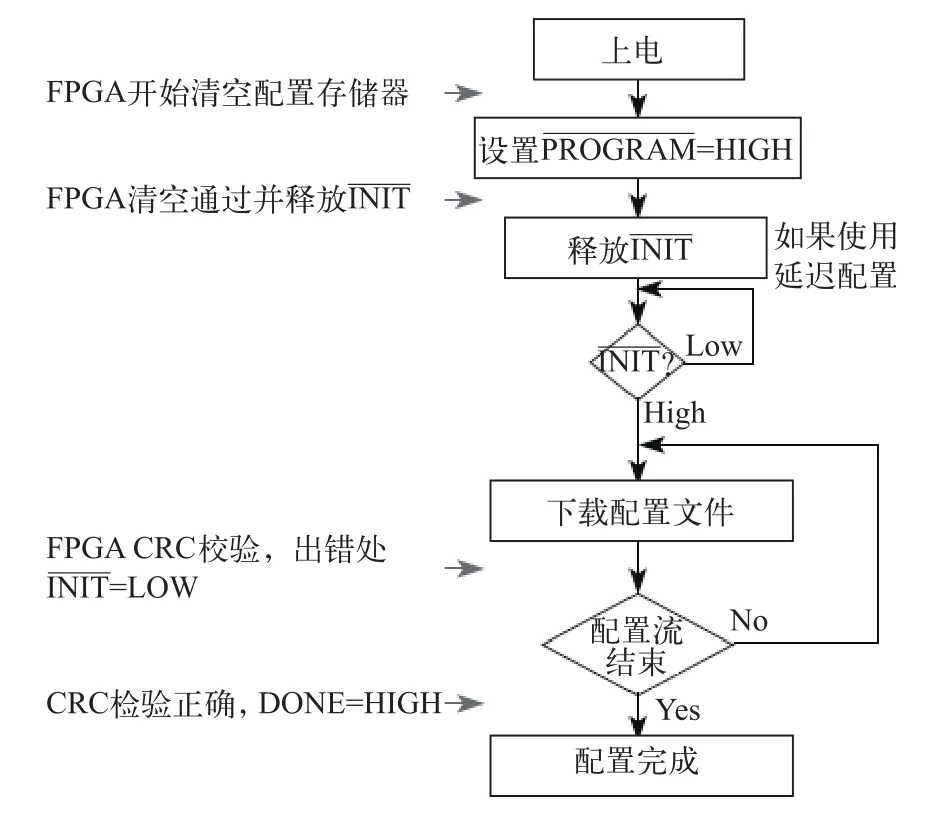

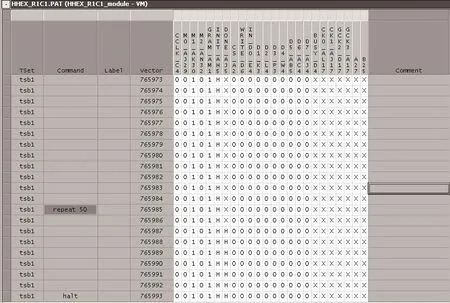

為實(shí)現(xiàn)bin文件到機(jī)器可識(shí)別的atp文件的轉(zhuǎn)換,特設(shè)計(jì)小型軟件如圖2所示。該軟件使用C語(yǔ)言編制,將bin文件按特定方式分離成D0~D7的向量文件。轉(zhuǎn)換后文件不僅包含了bin中D0~D7的信息,還增加了從并模式中其他管腳的輸入/輸出信息,提高編碼效率。圖3為轉(zhuǎn)換后的文件格式。根據(jù)圖4配置流程可以看出增加的信息包括外部輸入CCLK信號(hào),PROGRAM信號(hào)拉低,驗(yàn)證INIT是否變高,CRC校驗(yàn)后INIT與DONE信號(hào)的輸出驗(yàn)證。

3 基于ATE的FPGA測(cè)試

3.1 對(duì)FPGA進(jìn)行測(cè)試

由于本文的試驗(yàn)對(duì)象是XCV1000,芯片規(guī)模比較大。同時(shí)FPGA的測(cè)試需要多次“配置-測(cè)試”過(guò)程,對(duì)測(cè)試向量的深度要求比較高。所以本文以Teradyne的UltraFLEX為測(cè)試平臺(tái),該ATE的測(cè)試管腳數(shù)可達(dá)1 024個(gè),測(cè)試向量深度達(dá)256M,測(cè)試頻率可達(dá)2GHz,完全滿足市場(chǎng)上多數(shù)FPGA的測(cè)試要求。

圖2 轉(zhuǎn)換軟件

圖3 轉(zhuǎn)換后的文件形式

3.2 對(duì)FPGA進(jìn)行配置

使用2.3的方法將bin文件轉(zhuǎn)換成ATE識(shí)別的可配置文件。生成的配置文件導(dǎo)入到ATE后,可將其作為普通的功能碼進(jìn)行測(cè)試。為了驗(yàn)證FPGA是否完成配置,在結(jié)尾處增加一小段測(cè)試碼,即DONE信號(hào)輸出為高,INIT信號(hào)輸出為高,如圖4所示。若這兩個(gè)信號(hào)輸出正確說(shuō)明配置成功。為了觀察直觀與調(diào)試,本文使用的DUT在DONE信號(hào)的輸出增加了一個(gè)LED。

3.3 測(cè)試實(shí)現(xiàn)

FPGA配置完成后,F(xiàn)PGA便被配置為特定的功能,此時(shí)就可以作為普通邏輯器件進(jìn)行測(cè)試了,可進(jìn)行參數(shù)與功能測(cè)試。

4 測(cè)試結(jié)果與結(jié)論

該方法把配置作為一個(gè)測(cè)試項(xiàng),實(shí)現(xiàn)了FPGA的在線配置,且可以改變配置速度,對(duì)芯片進(jìn)行全面的分析與測(cè)試,施行比較簡(jiǎn)單。通過(guò)對(duì)XCV1000的測(cè)試表明,該方法可行、高效、通用性強(qiáng),對(duì)于實(shí)現(xiàn)FPGA的產(chǎn)業(yè)化具有重要意義。

圖4 配置流程

圖5 最終配置碼

[1] 薛宏,趙欣.FPGA測(cè)試技術(shù)研究[J].微處理機(jī),2008,2 279(2):11-14.

[2] 唐恒標(biāo),馮建華,馮建科.基于測(cè)試系統(tǒng)的FPGA邏輯資源的測(cè)試[J].微電子學(xué),2006,36(3):292-295.

[3] Xilinx, Inc. Virtex? 2.5 V Field Programmable Gate Arrays[C].

[4] 薛小剛,葛毅敏.Xilinx ISE 9.X FPGA/CPLD設(shè)計(jì)指南[M],北京,人民郵電出版社,2007:210-219.