雙抽頭CCD 圖像整合優化設計

李洪法 ,薛旭成,郭永飛,朱宏殷,2

(1.中國科學院 長春光學精密機械與物理研究所,吉林 長春130033;2.中國科學院 研究生院,北京100039)

1 引 言

隨著電子耦合器件( Charge Coupled Device,CCD) 在光電成像領域應用范圍的擴大,應用系統對CCD 的功能和性能要求越來越高,CCD 逐漸向大尺寸、小像元、高速度的方向發展。為了適應上述發展要求,許多CCD 在輸出數據時采用了多抽頭的結構形式[1-2]。這種結構形式的CCD 輸出的圖像呈多段式,如果直接使用,則最終的圖像將呈條段式,這與實際使用不相符合。另一方面,通常這種結構CCD 的多個抽頭間的數據輸出方向相反。因此,實際應用這種CCD 時,需要對其輸出的圖像數據進行重新整合。本文提出了一種利用XILINX VIRTEX 系列現場可編程門陣列( FPGA)的內部Block RAM 實現多抽頭CCD 圖像數據整合的方法。

2 基本原理

某系統使用的線陣CCD 共有4 096 個像元,采用雙抽頭輸出的工作模式,其圖像輸出原理示意圖如圖1 所示。

圖1 兩抽頭CCD 的圖像輸出示意圖Fig.1 Output sketch of double-tap CCD

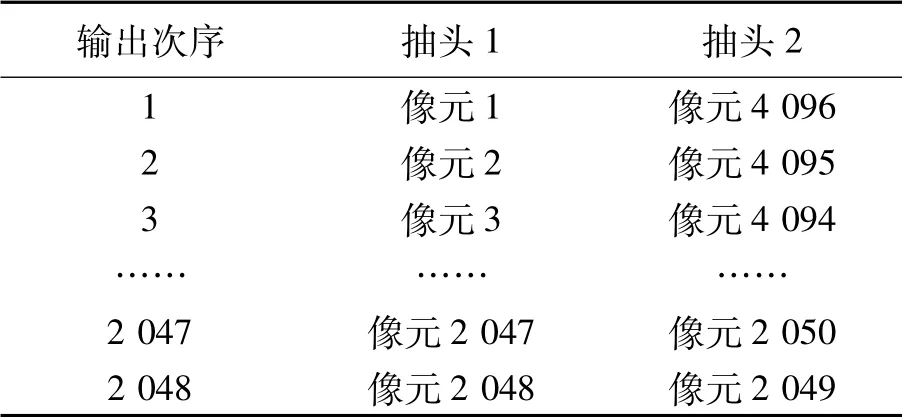

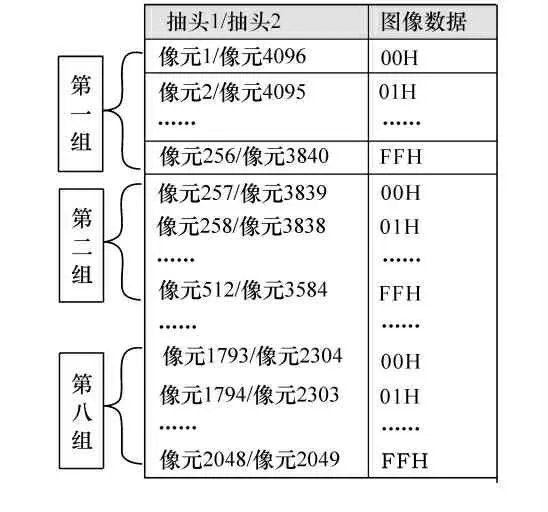

表1 CCD 各像元的輸出次序Tab.1 Pixel sequences of CCD output

當CCD 完成對景物積分后,該行的圖像數據從位于CCD 兩側的抽頭1 和抽頭2 同時輸出。每個抽頭輸出2 048 個像元的數據。但是抽頭1 輸出的圖像是正序,而抽頭2 輸出的圖像是逆序,即抽頭1 依次輸出像元1 ~像元2 048,抽頭2 依次輸出像元4 096 ~像元2 049[3]。兩個抽頭輸出的圖像像元順序如表1所示。

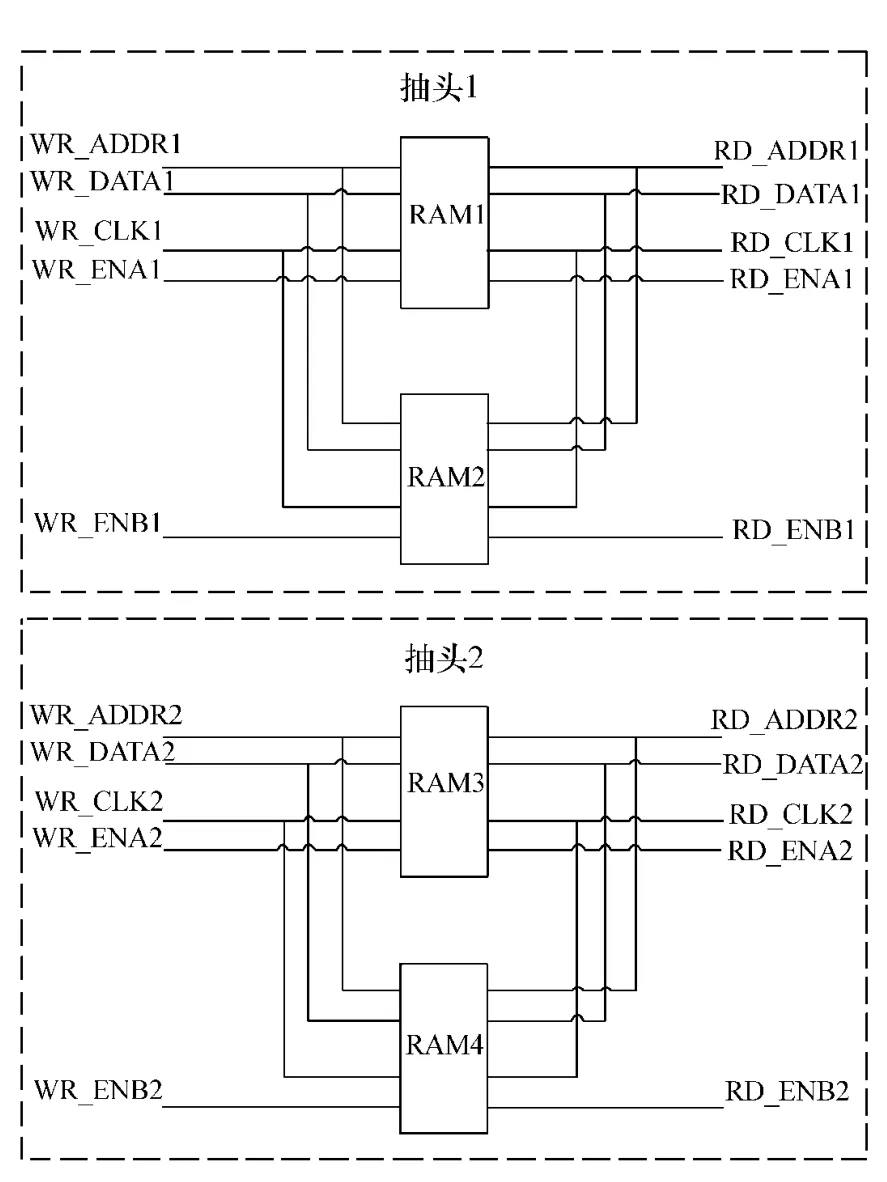

由于該CCD 是多抽頭輸出,其順序和正常景物的順序不一致,因此需要對其進行二次整合后再使用[4]。整合的要求是按CCD 的實際像元位置將兩個抽頭的數據合并為一路輸出,即把兩個抽頭的圖像數據合并為一路按像元1 ~像元4 096順序輸出圖像[5]。通常利用乒乓原理對兩個抽頭的數據進行緩存處理[6],其實現結構如圖2 所示。

圖2 傳統的乒乓操作整合結構Fig.2 Conformal structure of traditional Ping-Pang

在圖2 中,RAM1 和RAM3 分別用于緩存抽頭1 和抽頭2 的第1 行圖像數據,RAM2 和RAM4分別用于緩存抽頭1 和抽頭2 的第2 行圖像數據。如果輸入的圖像數據以8 bit 進行量化,則對于第2 小節中的CCD而言,RAM1 ~RAM4 都是容量為2 Kbit 的雙口RAM,因此在這種工作結構下,完成圖像數據的整合共需要8 Kbit 的雙口RAM。

圖2 中RAM 使用的工作原理如下:

(1) 在第N個行周期,將CCD 的第N行數據分別緩存進RAM1 和RAM3 中;

(2) 在第N+1 個行周期,在將CCD 的第N+1 行數據分別緩存進RAM2 和RAM4 中的同時,將之前緩存在RAM1 和RAM3 中的第N行圖像數據進行整合輸出至輸出端口;

(3) 在第N+2 個行周期,在將CCD 的第N+2 行數據分別緩存進RAM1 和RAM3 中的同時,將緩存在RAM2 和RAM4 中的第N+1 行圖像數據進行整合輸出至輸出端口;

(4) 在第4 個行周期以及后面的行周期中,重復上述步驟2 和步驟3 即可,直至停止數據采集。

采用上述方法可以實現對多抽頭CCD 圖像數據的整合,但是它的缺點是占用的RAM 資源量較大,輸出有延滯,這在一些對資源要求比較高的系統中是不合適的[7]。根據CCD 兩個抽頭輸出的圖像數據的特點,本文對上述RAM 使用結構進行了改進。

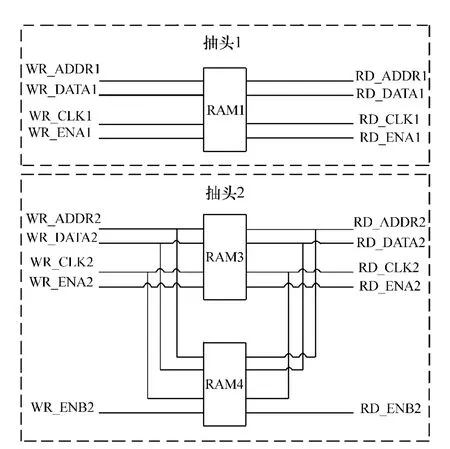

圖3 改進乒乓后的數據整合結構Fig.3 Conformal structure of improved Ping-Pang

由于抽頭1 的圖像數據與抽頭2 同時輸入,但在輸出時抽頭1 的圖像數據比抽頭2 的數據先輸出,且抽頭1 的數據在輸入時和輸出時沒有改變[8],因此可以通過調整工作時序使得采用一片RAM 即可完成抽頭1 的數據緩存。改進后的RAM 結構如圖3 所示。

圖3 中,抽頭1 占用了一片容量為2 Kbit 的RAM,抽頭2 用了兩片容量為2 Kbit 的RAM,合計共占用6 Kbit 大小的RAM,和改進前相比節省了25%的存儲空間[8]。

抽頭1 數據的像元順序在輸入時和輸出時一致,而且輸出時先于抽頭2 輸出。因此,如果寫入速率為CLK1X,讀出速率為CLK2X,則只要在寫入端完成一半的圖像數據寫入后,即可在完成寫入數據的同時也完成對抽頭1 數據的讀取。為了保證FPGA 內部對RAM 操作時有可靠的建立時間和保持時間,對抽頭1 數據完成了1025 個像元數據存儲后再進行讀取,詳細過程如下:

(1) 在第N個行周期中,在RAM1 和RAM3的寫入端,將CCD 數據以CLK1X 的速率分別緩存進RAM1 和RAM3 中; 在RAM1 輸出端,在寫完第1 026 個像元的數據后,以CLK2X 的速率將RAM1 中存儲的抽頭1 數據按順序進行輸出。將RAM1 中的數據讀完后,將RAM3 的數據按規定的順序進行輸出。

(2) 在第N+ 1 個行周期中,在RAM1 和RAM4 的寫入端,將CCD 數據以CLK1X 的速率分別緩存進RAM1 和RAM4 中; 在RAM1 輸出端,在寫完第1 026 個像元的數據后,以CLK2X的速率將RAM1 中存儲的抽頭1 數據按順序進行輸出。將RAM1 中的數據讀完后,將RAM4 的數據按規定的順序進行輸出。

(3) 在第N+2 個行周期以及后面的行周期中,重復上述步驟1 和步驟2 即可。

3 仿真實驗與結果分析

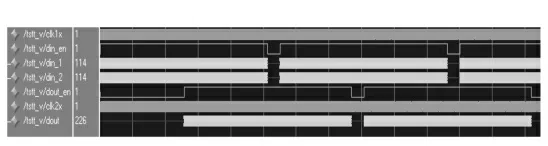

為了驗證改進后的RAM 結構,采用XILINX的VIRTEX 系列FPGA 搭建了一個軟件平臺[9]對其進行仿真驗證,如圖4 所示。其中自校圖形產生模塊用來模擬從CCD 輸出的兩個抽頭的數據,圖像整合模塊采用第2 節中介紹的RAM 結構實現將輸入的數據按照指定的順序重新整合[10],并將整合后的數據輸出,由此形成該仿真軟件的頂層原理圖,如圖5 所示。

圖4 仿真軟件方框圖Fig.4 Block diagram of simulation software

在圖5 中,自校圖形產生模塊zjtx 模擬CCD的抽頭1 和抽頭2 的輸出圖像,兩個抽頭的圖像格式相同。由于系統中所使用的CCD 共有4 096個像元從兩個抽頭分別輸出,因此每個抽頭上有2 048個像元數據輸出。自校圖形是數據由00H逐漸增加至FFH 的數據段 ,根據上面的分析可知,每個抽頭上這樣的數據段共有8 組,如表2所示。

表2 自校圖形模塊輸出格式Tab.2 Output format of self-check image module

圖5 圖像整合的頂層原理圖Fig.5 Top scheme of image conformity

圖像整合模塊由RAM1,RAM34,hecheng 和xzout 等子模塊構成。由于圖3 中的WR_ENA2和WR_ENB2 互相對立,即當WR_ENA2 有效時,WR_ENB2 無效;當WR_ENA2 無效時,WR_ENB2有效。因此可以將這兩個信號作為RAM 的寫地址線使用,即可以將圖3 中的RAM3 和RAM4 兩片RAM 更新為圖5 中的一片RAM—RAM34。這樣,自校圖形模塊產生的兩抽頭數據在hecheng子模塊的控制下,在RAM1 和RAM34 兩片RAM之間可進行乒乓存儲和讀取。最后,通過xzout 子模塊輸出整合后形成的有序圖像流。

圖6 ModelSim 仿真結果Fig.6 Simulation result of ModelSim

圖7 整合后行頭數據( 局部)Fig.7 Conformed data at the beginning of line

圖8 整合后抽頭接縫處數據( 局部)Fig.8 Conformed data at the join of two taps

在上述輸入圖像數據格式下,利用ModelSim軟件對上述模塊進行了仿真。仿真結果如圖6 所示。將其進行局部放大后,如圖7 ~圖9 所示,分別是整合后行首、抽頭接縫以及行尾處的局部放大圖。從圖中可以看出,輸出圖像實現了對輸入的兩抽頭數據按照CCD 像元1 ~4 096 的順序重新整合,完成了工作目標。

圖9 整合后行尾數據( 局部)Fig.9 Conformed data at the end of line

4 結 論

針對硬件資源占用率要求較高的CCD 圖像數據采集系統,提出了一種基于XILINX VIRTEX系列FPGA 的內部BLOCK RAM,利用改進的RAM 結構實現了對雙抽頭CCD 輸出圖像數據的整合。與傳統的乒乓操作方法相比,該方法可以節省25%的RAM 資源占用,大大降低了軟件對系統硬件資源的要求,有利于實現系統的集成化、小型化和輕量化,也有利于降低系統的成本。該方法在實際的工程中得到了成功應用,從運行結果看,該方法是有效和準確的。

[1] 胡琳.CCD 圖像傳感器的現狀及未來發展[J].電子科技,2010,23(6) :82-85.HU L. Current situations and future developments of CCD image sensors[J].Electronic Sci.&Technology,2010,23(6) :82-85.( in Chinese)

[2] HIDESHI A. Device technologies for high quality and smaller pixel in CCD and CMOS image sensors[C]//Proceeding of the Technical Digest International Electron Devices Meeting,2004:989-912.

[3] THEUWISSEN A J P. The hole role in solid-state imagers[J].IEEE T. Electron Devices,2006,53(12) :2972-2980.

[4] 王明富,楊世洪,吳欽章.大面陣CCD 圖像實時顯示系統的設計[J].光學 精密工程,2010,18(9) :2053-2059.WANG M F,YANG SH H,WU Q ZH. Design of large-array CCD real-time display system[J].Opt. Precision Eng.,2009,17(8) :2053-2059.( in Chinese)

[5] 徐欣,于紅旗,易凡,等.基于FPGA 的嵌入式系統設計[M].北京:機械工業出版社,2004.XU X,YU H Q,YI F,et al. Embedded System Design Based on FPGA[M]. Beijing:China Machine Press,2004.( in Chinese)

[6] 周賢波,馮龍齡.基于DSP 和FPGA 圖像采集技術的研究[J].光學技術,2006,32( 增) :141-143.ZHOU X B,FENG L L. A study on image acquisition technology based on DSP and FPGA[J].Opt. Technique,2006,32( S) :141-143.( in Chinese)

[7] 梁冰,易茂祥,顏天信.高性能線性CCD 開發平臺的研制[J]. 合肥工業大學學報( 自然科學版) ,2010,33( 10) :1579-1581.LIANG B,YI M X,YAN T X. Design of high-performance linear CCD development platform[J].J. Hefei University Technol.,2010,33(10) :1579-1581.( in Chinese)

[8] DUAN J H,DENG Y L,LANG K. Development of image processing system based on DSP and FPGA[C],ICEMI'07. 8th Int Conf on Electronic Measurement and Instruments,Aug 16-18 2007,Xi'an,China,2007:2791-2794.

[9] ZHANG F. A high-speed method of CCD image data storage system[J].IEEE Advanced Computer Control,2010,2(6) :45-48.

[10] ZHAO Y F,WANG Q Y. Digital image storage system based on 1M60 digital CCD[J].Electronics&Control,2007,14(5) :179-183.

[11] 王文華,何斌,任建岳.線陣CCD 成像系統自校圖形設計[J].光學 精密工程,2009,17(8) :2011-2016.WANG W H,HE B,REN J Y. Design of self-check figures in linear CCD imaging system[J].Opt. Precision Eng.,2009,17(8) :2011-2016.( in Chinese)