一種基于偏移源的頻率合成技術(shù)分析

陳煥東,牛 旭,劉立青

(中國(guó)電子科技集團(tuán)公司第五十四研究所,河北石家莊 050081)

0 引言

頻率合成技術(shù)有超過(guò)60年的發(fā)展歷史,各種頻率合成技術(shù)層出不窮。據(jù)報(bào)道,美國(guó)Phase Matrix公司在2009年發(fā)布了一種新的基于偏移源的頻率合成技術(shù)開發(fā)的頻率合成器[1],該頻率合成器相位噪聲和雜散信號(hào)指標(biāo)都非常出色,使得基于偏移源的頻率合成技術(shù)在近幾年逐漸成為一個(gè)研究熱點(diǎn)。

分析基于偏移源的頻率合成技術(shù)的相位噪聲和雜散信號(hào)產(chǎn)生原理,并通過(guò)實(shí)際應(yīng)用加以驗(yàn)證,對(duì)設(shè)計(jì)低相位噪聲和低雜散信號(hào)的頻率合成器有重要意義。

1 相位噪聲分析

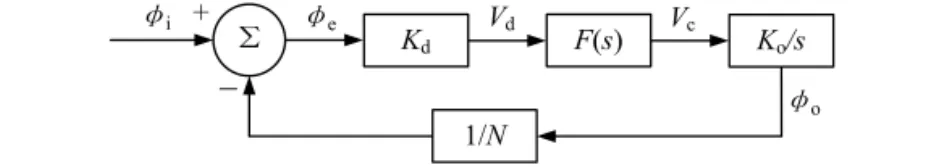

1.1 PLL線性模型

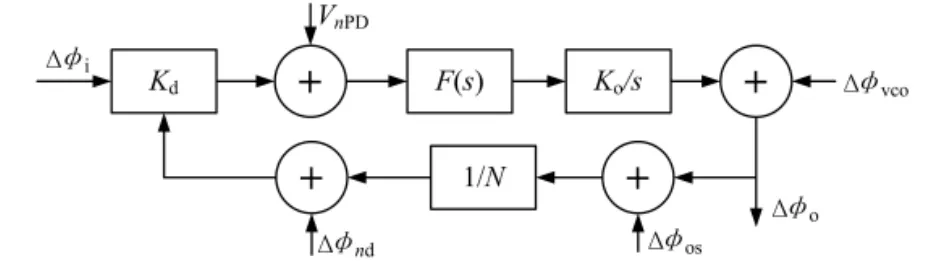

PLL已經(jīng)成為使用最廣泛的頻率合成技術(shù)之一,幾乎所有的頻率合成器都使用PLL。PLL是一種負(fù)反饋系統(tǒng),鎖定后鑒相器的2個(gè)輸入信號(hào)的相位φo/N和φi之間保持一個(gè)恒定的相位差φe。在鎖定后,可認(rèn)為PLL是線性的,其線性模型如圖1所示。

圖1 PLL線性模型

PLL閉環(huán)傳遞函數(shù)可表示為:

實(shí)際應(yīng)用中,常用估算公式如下:

式中,ωn為PLL自然角頻率。

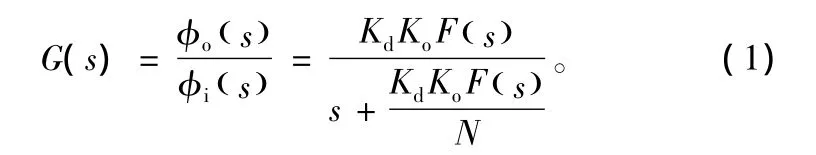

1.2 基于偏移源的PLL相位噪聲

如圖2所示,在PLL反饋支路中加入偏移源和混頻器構(gòu)成一種基于偏移源的PLL。除了偏移源,其他部分稱為主環(huán)。

圖2中PFD為鑒頻鑒相器,LF為環(huán)路濾波器。VCO信號(hào)fVCO、偏移源信號(hào)fos和鑒相信號(hào)fr之間的頻率關(guān)系為:

圖2 帶偏移源的PLL

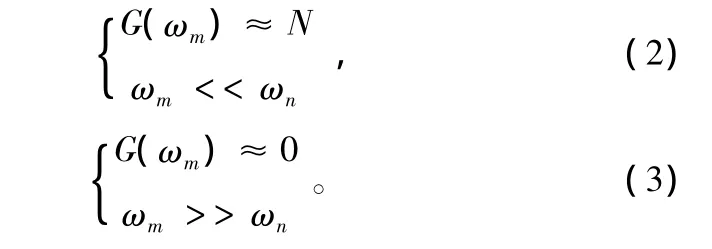

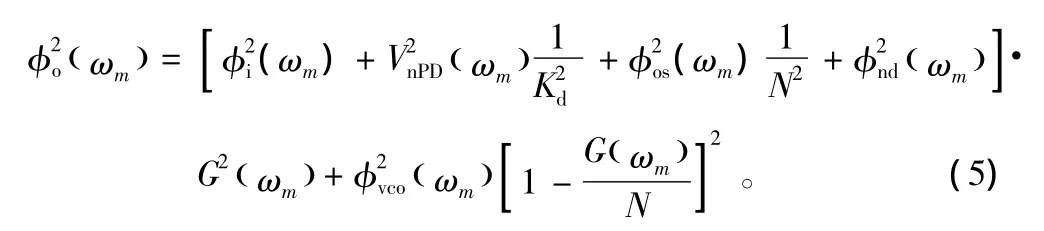

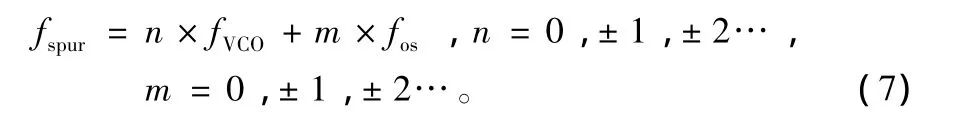

假設(shè)PLL中各個(gè)部分為理想無(wú)噪聲,加入等效噪聲源建立相位噪聲模型[1],對(duì)其進(jìn)行相位噪聲分析,如圖3所示。

圖3 加入偏移源的PLL相位噪聲模型

圖3中,Δφo為系統(tǒng)輸出相位抖動(dòng);Δφos為偏移源fos的相位抖動(dòng);Δφi為參考源相位抖動(dòng);VnPD為PD引入的噪聲電壓;ΔφVCO、Δφnd分別為VCO和N分頻器的相位抖動(dòng)。

由式(6)可以看出,經(jīng)過(guò)閉環(huán)響應(yīng)后,系統(tǒng)固有相位噪聲基底(ωm)惡化20lgN dB;加入偏移源后,偏移源相位噪聲(ωm)和環(huán)路分頻比N沒(méi)有關(guān)系。系統(tǒng)環(huán)路帶寬內(nèi)的相位噪聲由系統(tǒng)固有噪底、參考源相位噪聲、分頻比N和偏移源相位噪聲共同決定決定。

根據(jù)式(4),如果fos和fVCO頻率非常接近,那么分頻比N就很小。根據(jù)式(6),減小分頻比N后,系統(tǒng)固有相位噪聲基底就不再是決定系統(tǒng)相位噪聲的主要因素,偏移源相位噪聲成為決定系統(tǒng)相位噪聲的主要因素。

2 雜散信號(hào)分析

2.1 偏移源引入的雜散信號(hào)

頻率合成器中存在諸多非線性電路,如混頻器、分頻器和鑒相器等。當(dāng)多種頻率信號(hào)通過(guò)非線性電路時(shí)會(huì)發(fā)生交調(diào)響應(yīng),產(chǎn)生許多雜散信號(hào),當(dāng)雜散信號(hào)落入PLL環(huán)路帶寬內(nèi)時(shí),雜散信號(hào)會(huì)惡化。

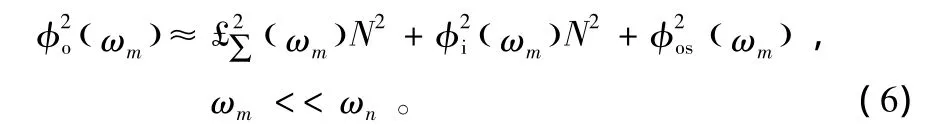

令雜散信號(hào)fspur為:

當(dāng)n和m的絕對(duì)值越小,并且fspur小于環(huán)路帶寬時(shí),雜散信號(hào)越惡劣。通常雜散信號(hào)出現(xiàn)在fVCO±fspur頻率上。

這種雜散信號(hào)主要是由于混頻器端口間隔離度有限,造成fVCO信號(hào)和fos信號(hào)在偏移源內(nèi)部發(fā)生交調(diào)響應(yīng)而產(chǎn)生雜散信號(hào)。當(dāng)這種雜散信號(hào)在VCO輸出頻率距離偏移源的鑒相頻率整數(shù)倍頻率非常近的時(shí)候尤為明顯。在混頻器和偏移源之間加入一個(gè)反向隔離度高的放大器是降低這種雜散信號(hào)比較好的方法。此外,偏移源和主環(huán)在空間布局和電源方面也要采取嚴(yán)格的隔離措施,以減小相互間的干擾。

2.2 DDS引入的雜散信號(hào)

為獲得微小頻率步進(jìn),往往要使用DDS。由于相位截?cái)啵邢拮珠L(zhǎng)和DAC非線性等因素造成DDS雜散信號(hào)輸出的不確定性,因此在一些PLL+DDS的方案中,DDS雜散信號(hào)是一個(gè)困擾設(shè)計(jì)師的難題。將DDS輸出作為PFD的參考輸入,根據(jù)式(6)可知,DDS引入的雜散信號(hào)經(jīng)過(guò)閉環(huán)相應(yīng)后要惡化20lgN dB。采用偏移源后,環(huán)路分頻比得到大大減小,甚至為1,所以由DDS引入的雜散信號(hào)經(jīng)過(guò)閉環(huán)響應(yīng)后惡化很小或者是無(wú)惡化。DDS遠(yuǎn)端雜散信號(hào)可以很輕松地被環(huán)路濾波器濾除。

3 關(guān)鍵技術(shù)

3.1 偏移源合成技術(shù)

偏移源可以是單一信號(hào)輸出或者是有一定帶寬的信號(hào)輸出。根據(jù)不同應(yīng)用偏移源的合成方式有很多種,可以采用PLL和梳狀譜發(fā)生器等。目的是獲得盡可能低的相位噪聲。

如果偏移源采用數(shù)字PLL,可以提高鑒相頻率,增大頻率步進(jìn),以降低環(huán)路分頻比,從而獲得低相位噪聲。要獲得更低的相位噪聲,可以采用模擬PLL。但無(wú)論是數(shù)字PLL還是模擬PLL在低相位噪聲和帶寬上相互制約,要獲得低相位噪聲往往難于實(shí)現(xiàn)較寬的帶寬。

采用梳狀譜發(fā)生器可以很輕松地獲得倍頻程的頻譜帶寬[3]和極低的相位噪聲。比如,使用梳狀譜發(fā)生器將100 MHz OCXO倍頻到4~8 GHz,倍頻次數(shù)40~80,相位噪聲理論惡化32 ~38 dB;OCXO在偏離載波100 kHz處相位噪聲為-170 dBc/Hz,所以經(jīng)過(guò)倍頻后8 GHz信號(hào)在偏離載波100 kHz處相位噪聲小于-130 dBc/Hz。

3.2 主環(huán)合成技術(shù)

因?yàn)橹鳝h(huán)的分頻比很小,噪底非常低,相位噪聲和雜散信號(hào)不再是主環(huán)要解決的主要問(wèn)題。其參考輸入可用微小頻率步進(jìn)對(duì)偏移源頻率間隔進(jìn)行“填充”,從而連續(xù)覆蓋所需的輸出帶寬,實(shí)現(xiàn)寬帶小步進(jìn)。鑒相器采用低噪底的 PLL芯片,例如ADF4002。混頻器采用寬帶高隔離度的混頻器,以提高主環(huán)和偏移源之間的隔離度。在一些情況下,還必須加入D/A轉(zhuǎn)換進(jìn)行頻率預(yù)選,避免發(fā)生錯(cuò)鎖。要特別注意式(4)中主環(huán)和偏移源頻率之間的關(guān)系,正確設(shè)置主環(huán)的鑒相極性。

4 工程應(yīng)用

結(jié)合工程實(shí)踐,介紹一種基于偏移源的頻率合成技術(shù)設(shè)計(jì)的C頻段頻率合成器,主要指標(biāo)要求如下:

輸出頻率范圍:4.6 ~5.4 GHz;

頻率步進(jìn):1 kHz;

相位噪聲:

≤-65 dBc/Hz(偏離載波0.1 kHz處);

≤-75 dBc/Hz(偏離載波1 kHz處);

≤-85 dBc/Hz(偏離載波10 kHz處);

≤-95 dBc/Hz(偏離載波100 kHz處);

雜散信號(hào):≤-70 dBc。

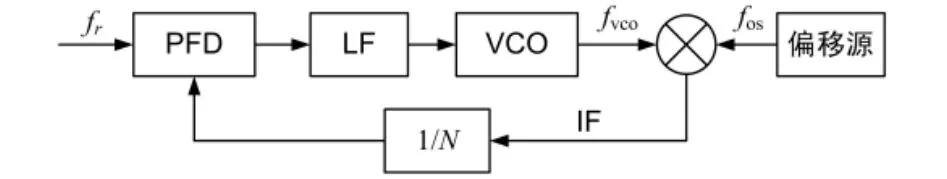

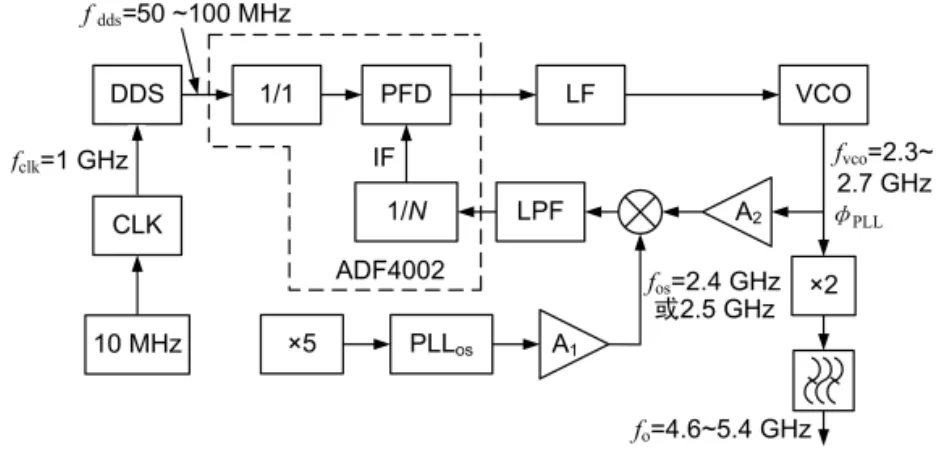

C頻段頻率合成器方案如圖4所示。將10 MHz參考源分2路,一路5倍頻后作為偏移源的參考;另一路作為1 GHz DDS時(shí)鐘源的參考。偏移源信號(hào)和2.3~2.7 GHz的VCO輸出信號(hào)進(jìn)行下混頻,混頻器使用HMC213,射頻端口和本振端口的隔離度大于40 dB。混頻后的中頻信號(hào)IF先經(jīng)過(guò)一個(gè)低通濾波器LPF,濾除遠(yuǎn)端的雜散信號(hào),LPF采用LTCC低通濾波器LFCN-1800;然后IF信號(hào)和DDS輸出信號(hào)fdds在ADF4002內(nèi)部進(jìn)行鎖相。最后經(jīng)2倍頻和濾波后輸出。由式(4)可得各頻率間關(guān)系:fVCO=fos±fdds× N 。fos取2.4 GHz或2.5 GHz;fDDS取50~100 MHz;當(dāng)N的取值為1時(shí),中頻IF為50~100 MHz;當(dāng) N的取值為2時(shí),中頻 IF為100~200 MHz。

圖4 C頻段頻率合成器方案

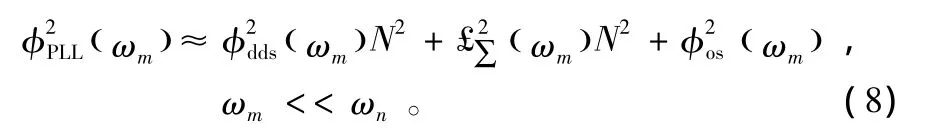

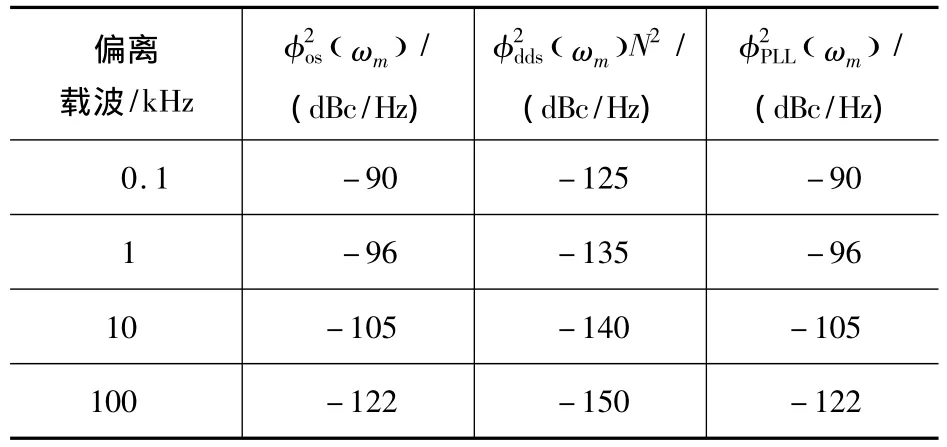

如果環(huán)路帶寬取3 MHz,最終主環(huán)頻率合成后在0.1~100 kHz處的相位噪聲(ωm)主要由fos的相位噪聲(ωm),fdds的相位噪聲(ωm)N2和主環(huán)噪底(ωm)N2三部分相迭加而成。

偏移源采用低噪底PLL芯片ADF4106去鎖一個(gè)2.4~2.5 GHz的低相位噪聲 CRO,鑒相頻率取50 MHz,環(huán)路帶寬取20 kHz。偏移源的實(shí)測(cè)相位噪聲( ωm)如表1所 示,其中( ωm)N2為 -135 dBc/Hz。

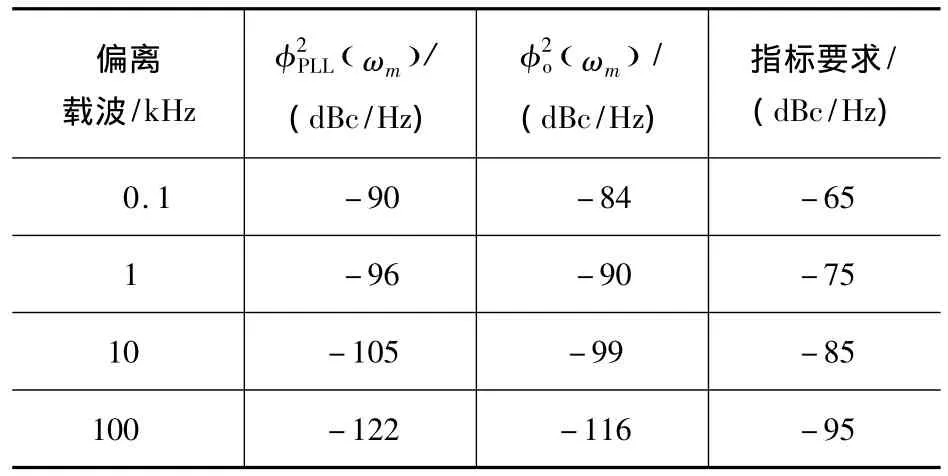

表1 C頻段頻率合成器各部分相位噪聲理論迭加

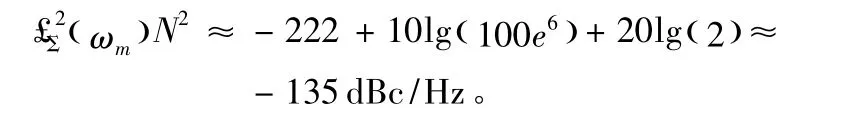

主環(huán)采用低噪底PLL芯片ADF4002,其噪底為-222 dBc/Hz;當(dāng)環(huán)路分頻比N為2,鑒相頻率為100 MHz時(shí),主環(huán)噪底(ωm)N2為:

DDS窄帶輸出無(wú)雜散信號(hào)動(dòng)態(tài)范圍(SFDR)小于 -90 dBc[2],主環(huán)分頻比最大為 2,所以 DDS 雜散信號(hào)對(duì)系統(tǒng)的影響可以忽略;分別在混頻器和偏移源之間,混頻器和 VCO之間加入一級(jí)放大器HMC308,其增益為18 dB,輸出壓縮點(diǎn)大于17 dBm,反向隔離度為35 dB;一方面可以將fVCO信號(hào)放大至混頻器本振信號(hào)要求的信號(hào)強(qiáng)度,另一方面很容易提高主環(huán)和偏移源間的隔離度;此外對(duì)主環(huán)和偏移源之間從空間布局和PCB布局上進(jìn)行嚴(yán)格的分腔隔離設(shè)計(jì),以減小相互間的干擾,實(shí)測(cè)雜散信號(hào)≤ -70 dBc。

5 性能測(cè)試結(jié)果分析

完成調(diào)試后對(duì)C頻段頻率合成器進(jìn)行測(cè)試,實(shí)測(cè)主環(huán)輸出相位噪聲(ωm)的結(jié)果如表2所示。

表2 C頻段頻率合成器相位噪聲對(duì)比

可以看出實(shí)測(cè)結(jié)果和理論迭加結(jié)果一致,這表明采用偏移源的頻率合成方案,系統(tǒng)噪底非常低,在這種情況下系統(tǒng)噪底不再是決定相位噪聲的主要因素,其相位噪聲主要由偏移源相位噪聲決定。2倍頻后系統(tǒng)輸出相位噪聲(ωm)如表2所示,系統(tǒng)輸出相位噪聲測(cè)試結(jié)果遠(yuǎn)優(yōu)于指標(biāo)要求。此外,雜散信號(hào)≤-70 dBc。采用基于偏移源的頻率合成技術(shù)實(shí)現(xiàn)了低相位噪聲,低雜散信號(hào)設(shè)計(jì)。

6 結(jié)束語(yǔ)

采用基于偏移源的頻率合成技術(shù),可以大大降低主環(huán)的環(huán)路分頻比,從而降低主環(huán)的噪底,這是該技術(shù)的核心。在毫米波段,偏移源采用取樣脈沖鎖相技術(shù),在偏離載波100 kHz處相位噪聲已經(jīng)做到-105 dBc/Hz。綜上所述,采用基于偏移源的頻率合成技在低相位噪聲和低雜散設(shè)計(jì)上有明顯的優(yōu)勢(shì)。 ■

[1]QuickSynTM Microwave Frequency Synthesizer. Phase Matrix Inc[S],2009.

[2]AD9912 Datasheet.Analog Device Inc[S],2007.

[3]楊新功,宋慶輝.超寬帶低相位噪聲頻率合成器的實(shí)現(xiàn)[J].無(wú)線電通信技術(shù),2006,32(3):39 -41.

[4]白居憲.低噪聲頻率合成[M].西安:西安交通大學(xué)出版社,1995.

[5]胡麗格,楊志國(guó),閔 潔.一種L波段的小步進(jìn)頻率合成器[J].無(wú)線電工程,2007,37(6):60-61.

[6]溫明艷.多環(huán)頻率合成器抗干擾研究[J].無(wú)線電通信技術(shù),2002,28(5):29-31.