WSI Polycide工藝的研究

朱賽寧,聶圓燕,陳海峰

(中國電子科技集團公司第58研究所,江蘇 無錫 214035)

1 引言

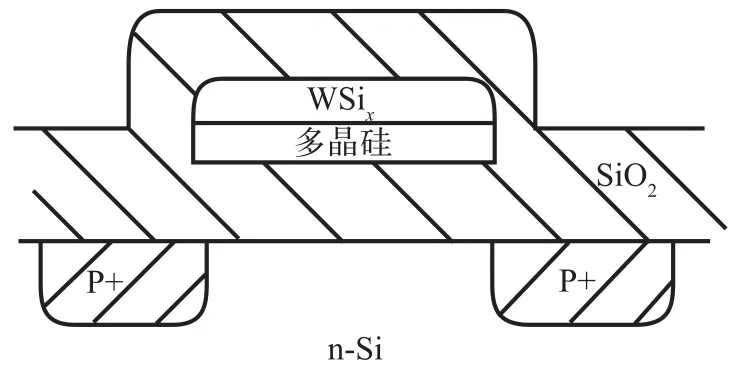

在MOS集成電路中,通常采用多晶硅作為柵電極及互連材料,它決定了特征尺寸。但隨著集成度的迅速提高,器件尺寸按比例縮小,線條越來越窄(≤1μm),節深越來越淺(<200nm),使得目前用作柵電極和互連的多晶硅薄層電阻大大增加,引起電路功耗和噪聲增加,限制了集成電路的速度。特別是在存儲器電路生產中,比如DRAM、FLASH和SRAM器件工藝過程中,需要降低多晶硅柵的電阻率從而提高器件的速度[1]。而多晶硅電阻率相對較高(33Ω/方~55Ω/方),所以在相關器件的制造中,可以通過在多晶硅上淀積一層WSI并經退火工藝后形成的Polycide復合柵結構來改進多晶硅柵的電阻率(Polycide結構如圖1所示)。可以使薄膜電阻降低一個數量級,從而能降低電阻壓降和R-C持續時間。有人對多晶硅化物和多晶硅器件性能進行了比較[2],結果發現,多晶硅化物結構兼備了SiO2-多晶硅及與硅化物互連的優點,同時又降低了表面薄層電阻和接觸電阻,使之既具備多晶硅柵的穩定可靠特性,又具備硅化物的高電導率特性,從而具有較好的工藝兼容性,所以得到了廣泛采用。

圖1 Polycide復合柵結構示意圖

但是在實際的工藝生產中,WSI膜層容易出現剝落、圓斑及色差等異常情況,嚴重的剝落會對后續工藝帶來顆粒、沾污,進而影響產品的成品率[3]。因此,研究WSI薄膜脫落的影響因素以及相應的解決措施具有重要意義。本文主要研究了WSI Polycide工藝流程中各種因素對WSI膜層的影響,并尋求WSI Polycide工藝相關的最優化條件。

2 原理

本文用Precision 5000設備淀積硅化鎢膜層,采用WF6-SiH4-H2反應體系,這是因為WF6具有很低的沸點19.5℃,與H2及SiH4的反應溫度低,使用方便,而且用WF6體系淀積具有非常好的選擇性[4]。薄膜的化學組分主要依賴于反應氣體的流量比及淀積溫度,主要反應為:WF6+ SiH4→WF6+SiF4+H2,反應溫度400℃。

3 實驗

樣品制備的常規流程如下:硅片通過氧化生長12.5nm柵氧SiO2,然后用LPCVD設備生長350nm多晶,再進行清洗后淀積一層150nm的WSI,然后爐管退火后進行多晶摻雜、多晶光刻、多晶腐蝕形成電路圖形,接著進行RTA退火及N+推結后進行Spacer淀積、致密、腐蝕、氧化等工藝流程,最后通過顯微鏡鏡檢觀察形貌。

但是在實際的生產過程中,通過顯微鏡鏡檢,發現產品片在做完Spacer氧化后硅片表面出現了不同程度的WSI剝落、色斑、圓斑等異常情況,針對這種現象,需要進行實驗來優化WSI工藝,達到最優效果。

由于在通常的工藝制造中,薄膜上很強的局部應力可能會造成襯底變形,甚至高的膜應力會導致開裂和分層,膜應力還可在襯底傳遞硅缺陷,進而導致可靠性問題[5]。而WSI膜層的應力為109數量級,且退火會使應力進一步變大,考慮到可能是應力的原因導致WSI膜層剝落、開裂,我們通過FLX5400應力儀薄層應力測量設備來測量這種形變。通過分析由于薄膜淀積造成的襯底曲率半徑(翹曲度)變化來進行應力測試。

對WSI膜層應力產生影響的主要有三個因素:

(1)WSI前清洗步驟;

(2)WSI淀積后爐管退火溫度;

(3)在WSI淀積后再淀積一層Cap Layer介質層,即淀積一層薄SiO2層,因為SiO2膜層應力為-109數量級,在一定程度上能緩解WSI膜層造成的高應力。

通過改變這些因素中的工藝條件進行整個Polycide工藝流程,測試各個工序后硅片膜層的應力及翹曲度變化,最后在Spacer氧化后通過顯微鏡鏡檢觀察硅片表面形貌。

4 結果與討論

4.1 WSI淀積前清洗對WSI的影響

本工藝線正常的清洗步驟為:10︰1HF漂SiO2→3#液→1#液→2#液清洗,目的是為了使WSI淀積前硅片表面光滑,無有機物、無機物、金屬及其他顆粒、沾污。另取一片做對比的圓片,在常規清洗后再加一步反濺,目的是去除硅片表面的自然氧化層。

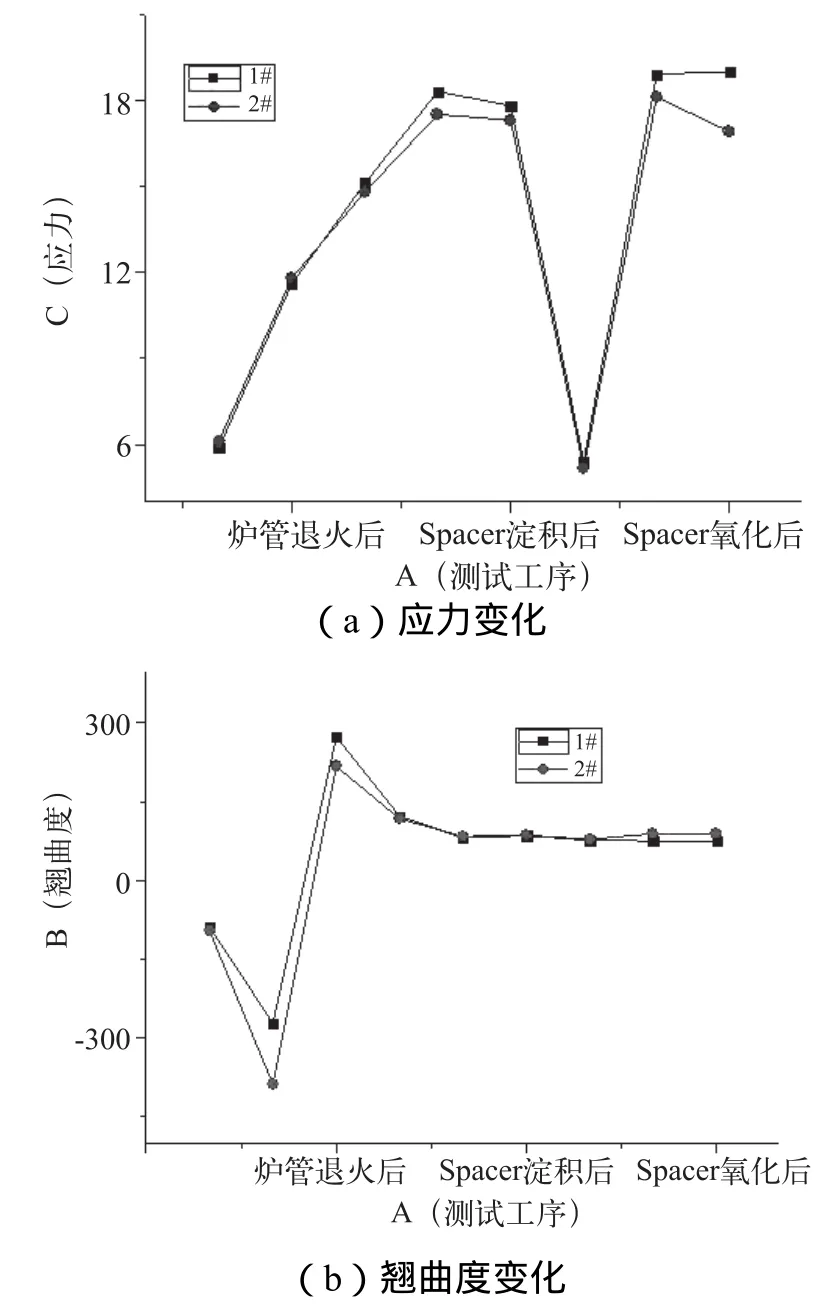

圖2給出了WSI淀積前正常清洗和加反濺的應力變化和翹曲度變化的趨勢,其中1#片正常清洗,2#片加反濺。從圖中看出,在整個工藝過程中,爐管退火前后的圓片翹曲度變化最大,圓片的應力先上升后下降(Spacer致密后最小),且標準清洗工藝和反濺工藝的圓片之間的應力差別不大。但是,加反濺的2#圓片Spacer氧化后出現了嚴重的剝落情況。圖3為加反濺的2#圓片Spacer氧化后的圖片,其中圖3(a)為表觀圖片,可以看到圓片的邊緣一圈明顯異常,呈現白色剝落狀;圖3(b)為顯微鏡鏡檢照片,圖中白色絲狀物為剝落翹起的WSI層。

圖2 WSI淀積前正常清洗和加反濺的變化

4.2 淀積后爐管退火溫度對WSI膜層應力的影響

退火溫度從700℃/30min改至900℃/30min和1050℃/30min,硅片應力的改變差別較大。從圖4我們可以看到隨著退火溫度變高,退火前后應力變化就越大,到1050℃/30min退火條件時剝落已非常嚴重,影響后續工藝的進行。

4.3 Cap Layer層對WSI膜層應力及翹曲度的影響。

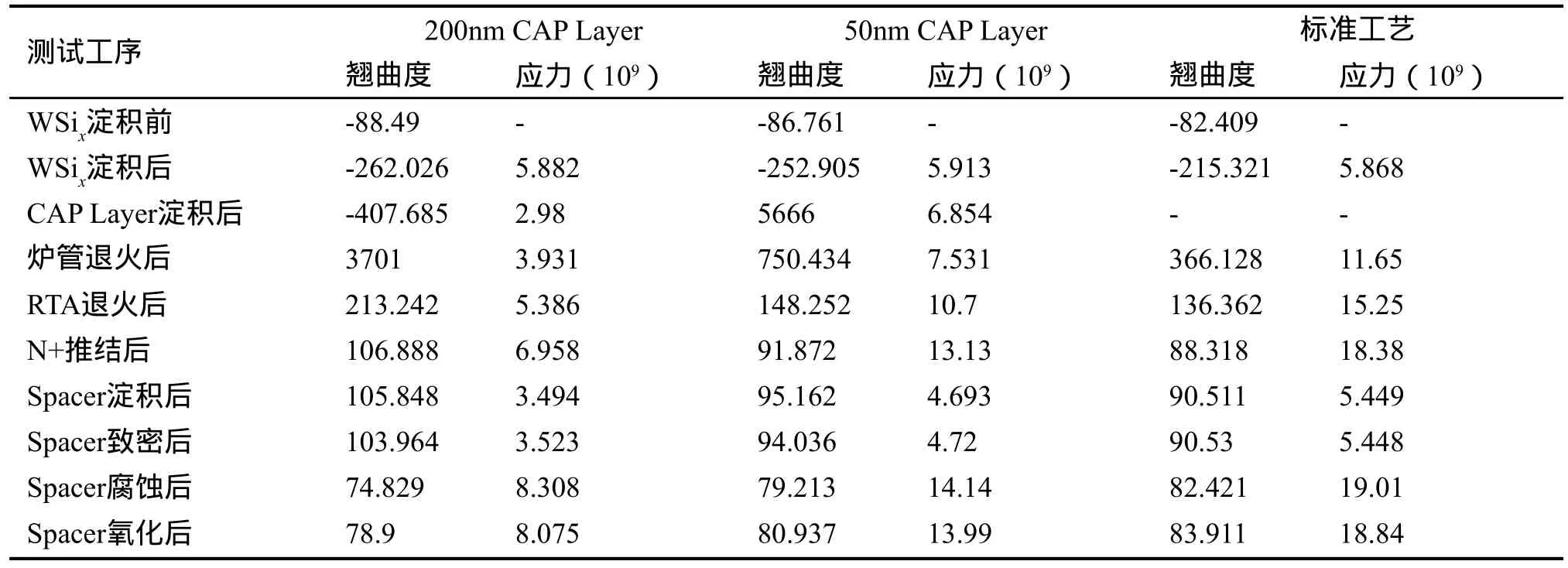

加Cap Layer層對WSI膜層應力及翹曲度的影響的具體數據如表1所示。

圖3 反濺工藝的圓片Spacer氧化后表面出現異常

圖4 爐管退火溫度對WSI膜層應力的影響

表1 Cap Layer層對WSI膜層應力及翹曲度的影響

圖5(a)、(b)為Cap Layer層對WSI膜層翹曲度及應力的影響圖,可以看到在WSI Polycide工藝過程中加入Cap Layer層在爐管退火前后翹曲度會發生大的變化,并且硅片在Spacer氧化后的應力比標準工藝的小且Cap Layer越厚應力越小,對WSI膜層的剝落有很大改善。但是Cap Layer太厚對Polycide復合柵的刻蝕帶來了很大影響,從而使復合柵腐蝕后表觀形貌較差,對后續的器件性能有較大影響,經實驗證明50nm的Cap Layer在不影響后續工藝的基礎上對WSI應力改善效果最明顯。

圖5 Cap Layer層對WSI膜層影響

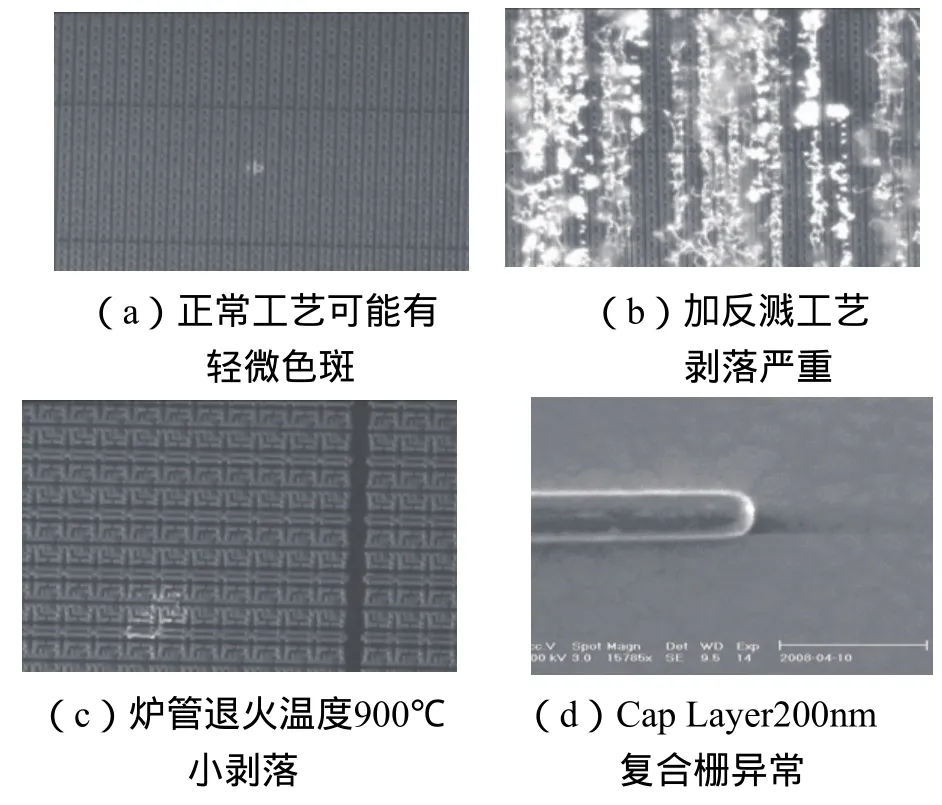

圖6展示了WSI Polycide工藝流程不同條件下形成的多晶柵顯微鏡形貌圖片:(a)是正常工藝的顯微鏡形貌圖,電路中可能產生輕微圓斑和色斑;(b)是正常工藝加反濺的顯微鏡形貌圖,膜層嚴重剝落;(c)是爐管退火溫度為900℃/30min的形貌圖,有輕微剝落;(d)是加Cap Layer 200nm復合柵腐蝕后打毛的SEM照片,而打毛對器件性能有較大影響;(e)是Cap Layer層厚度為50nm的條件下形成的圖形,復合柵形貌較好,無剝落。

圖6 各種條件硅片表面形貌圖

5 結論

本文研究了WSI Polycide工藝流程中不同條件對WSI膜層的影響。通過實驗比較及顯微鏡形貌分析發現WSI Polycide工藝中對WSI膜層表面性質影響主要表現為由應力產生的表面形變,而清洗、退火溫度高低及增加Cap Layer層都會對應力有一定影響,其中加Cap Layer層對膜層的應力改善最明顯,最終獲得了WSI Polycide工藝的優化條件:淀積前10∶1HF漂SiO2→3#液→1#液→2#液清洗+700℃/30min退火+50nm Cap Layer層。運用該優化條件完成的工藝流程,防止了后續流程中WSI的剝落、色斑等異常,且WSI的表面形貌和膜層性能均能達到CMOS制造的要求。本文對半導體器件中WSI Polycide工藝開發具有一定的參考價值。

[1]王陽元,T.I.卡明斯,趙寶瑛,等.多晶硅薄膜及其在集成電路中的應用[M].北京:科學出版社,2000.

[2]B.L.Crowder and S.Zirinsky.IEEE Trans.Electron Devices[J].1979,ED-26,369.

[3]崔錚.微納米加工技術及其應用[M].北京:高等教育出版社,2005.

[4]王永發,張世理,等.化學汽相淀積硅化鎢體系熱力學研究[J].電子學報,1989.

[5]Michael Quirk著,韓鄭生,等譯.半導體制造技術[M].北京:電子工業出版社,2004.