高清視頻信號長線傳輸的相位自動補償方法

郝學元

(南京郵電大學電子科學與工程學院,江蘇 南京 210046)

責任編輯:薛 京

在很多工程應用中,需要用普通網線長線傳輸視頻信號,視頻信號中的紅綠藍三基色模擬信號變成三對差分信號經過差分芯片驅動后,能進行長線傳輸,但由于網線中不同線對之間在雙絞時,實際長度并不一樣,特別是線纜長了后,不同線對之間的相位差較大,造成了視頻信號顯示時相位的不同步,影響成像質量[1]。傳統的模擬信號相位補償方法大多為調整傳輸線上的匹配電阻,在實現相位補償的同時,信號的幅度受到影響。為此,提出一種相位自動補償方法,實現不同傳輸長度下,紅綠藍三色信號的相位同步。

1 補償原理

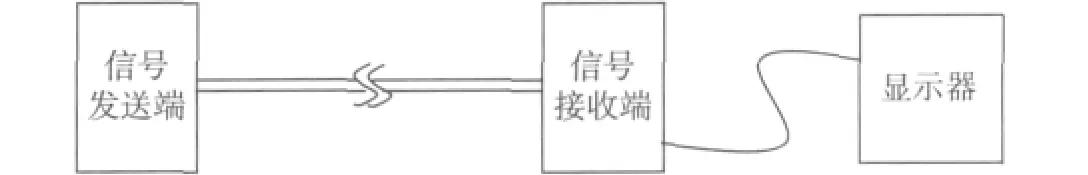

高清視頻信號長線傳輸系統包括信號發送端、雙絞線、信號接收端和顯示器,如圖1所示。雙絞線有4對,其中3對傳輸的是紅綠藍三基色的模擬信號。在系統傳輸長度一定的條件下,模擬信號的延時與數字信號的延時相同,外部的溫度、濕度等因素雖對延時也有影響,但相對幾百米長度的傳輸線,顯得微不足道,且3對線受影響程度相同。因此,造成視頻信號相位差的主要因素是傳輸線線長,所以在傳輸線線長發生變化時,必須要進行相位補償。

圖1 高清視頻傳輸系統結構圖

相位自動補償的原理為在信號發送端增加電子開關,上電時電子開關設置為相位自動補償模式,在此模式下,由發送端產生3個同頻同相位的脈沖信號,經差分電路后轉換成3路同相位的脈沖信號對輸出,經雙絞線傳輸,遠程信號接收端自動測量3個脈沖信號的相位差,將差值回傳,通過信號發送端控制模擬延遲芯片的寄存器設置值,將實際延遲的值在發送端提前,形成自動補償。

2 自動補償方法與設計

相位自動補償需在信號發送端添加自動相位補償工作模式,在信號接收端添加相位差測量電路;實現在補償工作模式下的補償值測量與回傳。

2.1 發送端標準同相位的產生

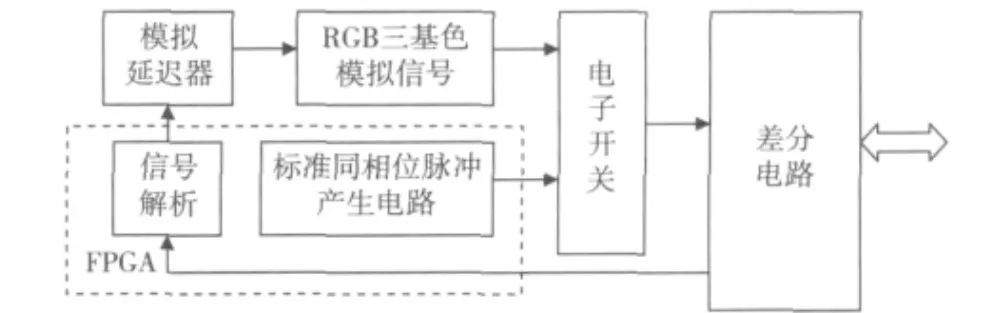

帶自動補償功能的發送端電路結構如圖2所示。在原發送端基礎上增加電子開關、標準同相位脈沖產生電路和對應的信號解析電路。

圖2 發送端電路結構

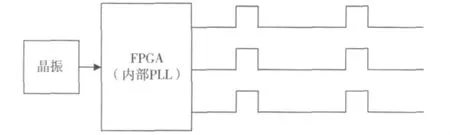

系統初次工作時,電子開關進入自動補償模式,與標準同相位脈沖產生電路相連。在本地端由FPGA產生脈沖。產生的脈沖信號周期為1 ms,脈沖寬度為100 μs,如圖3所示。把此信號作為標準源,通過高速差分轉換芯片ISL3259EFPGA工作時計數時鐘經內部PLL倍頻至333 MHz,可使得在處理回傳補償值時達到步進時間寬度為3 ns的補償步進。

圖3 標準同相位脈沖

2.2 接收端自動補償設計

接收端的電路結構如圖4所示,主要由電子開關、解碼電路、差分電路、相位差測量電路4部分組成。不需補償時,信號經電子開關進入解碼電路,解出視頻信號后送顯示器輸出;進入自動補償模式時,信號經電子開關進入差分電路與相位差測量電路。

圖4 接收端電路結構

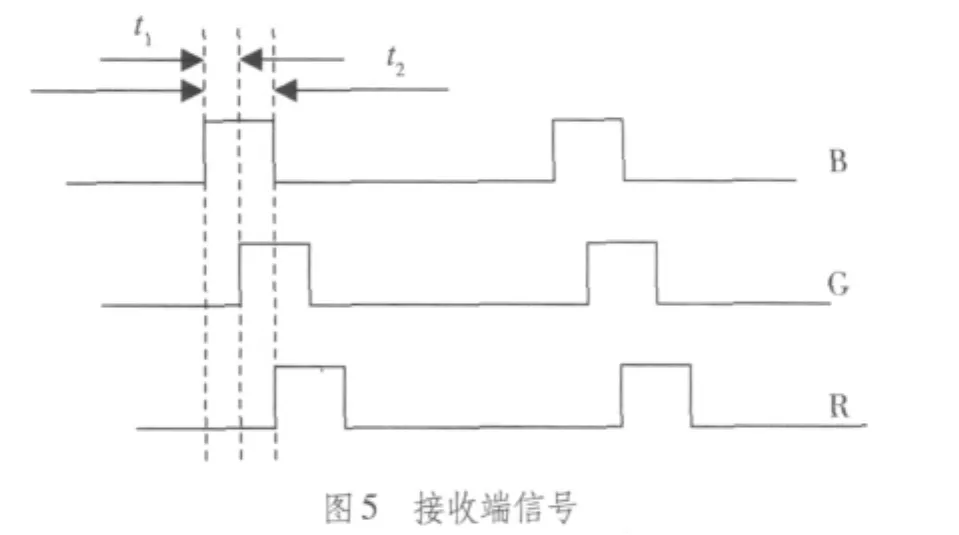

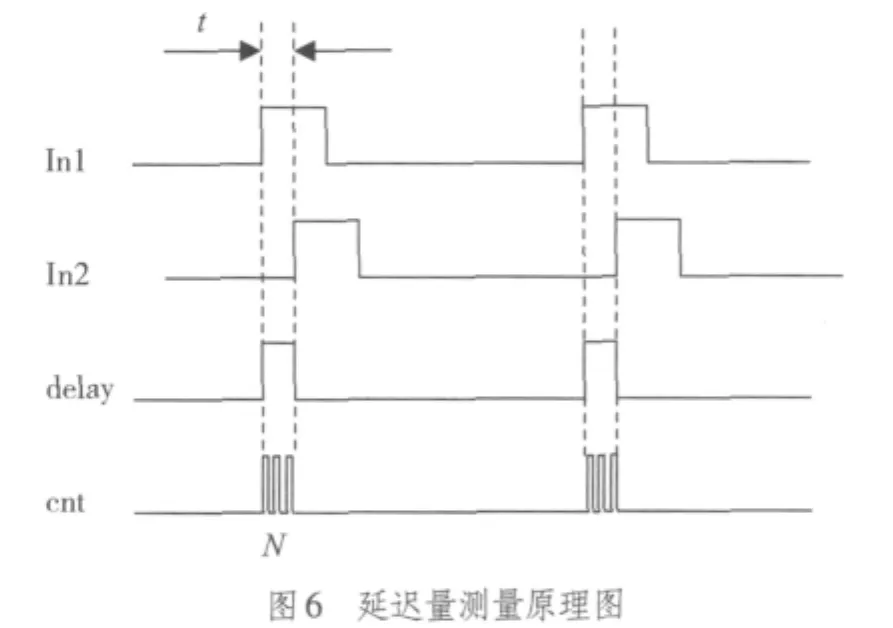

發送端的3標準脈沖信號經幾百米的差分傳輸后,在接收端會產生明顯的相位差,如圖5所示。經差分電路轉換恢復出的3個脈沖信號之間出現延遲,G信號比B信號延遲t1,R信號比B信號延遲t2。在線長不同的現場,延遲時間t1,t2不同,當線長改變時必須對系統進行相位補償。為得到t1,t2值,通過高速FPGA器件設計數字化相位差測量電路,捕捉到納秒級延遲量,時序原理[2]如圖6所示。輸入信號In1,In2,經組合邏輯得到延遲信號delay,以delay信號使能高速計數器,對FPGA內部高速時鐘計數,得到整數值N,即為信號In2對信號In1的延遲量,t=N×CLK,N為整數,設置計數器為5位,N取值為0~31。接收端所用FPGA內部時鐘與發送端相同,均為333 MHz,步進3 ns,可以記錄0~93 ns的延遲,反映出500 m以內線長的相位差。

相位差N值以數字量形式經差分電路傳回發送端。

2.3 發送端延遲線補償

發送端針對接收到的N值,將其送入模擬延遲芯片的寄存器,使得模擬信號在輸出時提前將延遲值補上以彌補長線后產生的相位差。針對標準脈沖信號,通過發送端N值的補償也可在接收端收到同頻同相位的脈沖信號。為驗證N值的準確性,通過脈沖信號的恢復加以觀察。

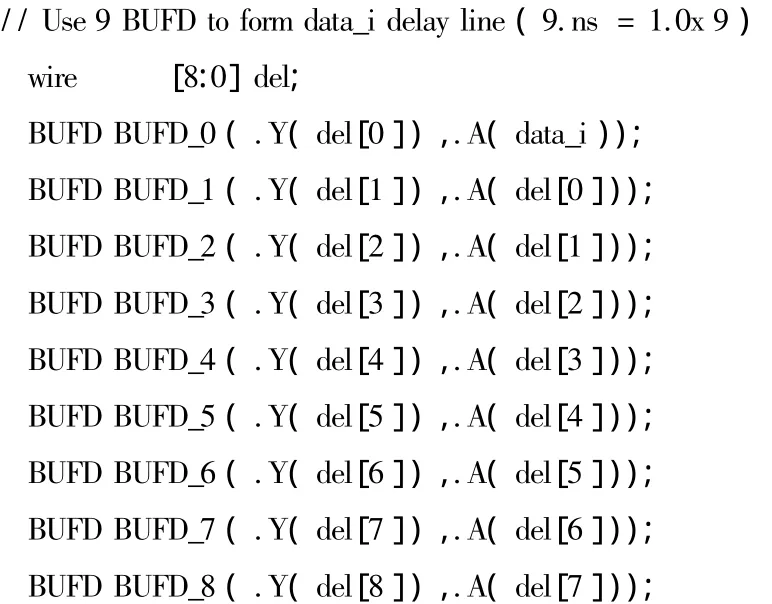

發送端利用FPGA的門電路延遲實現脈沖信號的相位補償。FPGA門電路的延遲時間在芯片的手冊中有明確的說明,以Xilinx公司的XC3S400芯片[3]為例,每個BUFD門電路的延長時間為1.0 ns,要實現N=3 ns,9 ns的延遲輸出,代碼為:

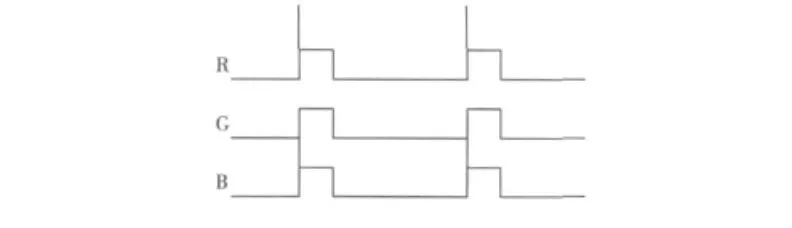

延遲補償后的信號經長線傳輸,在接收端差分電路變換后經示波器捕捉,如圖7所示,完全能夠實現相位補償。

圖7 補償后的脈沖信號

3 視頻信號實際補償效果

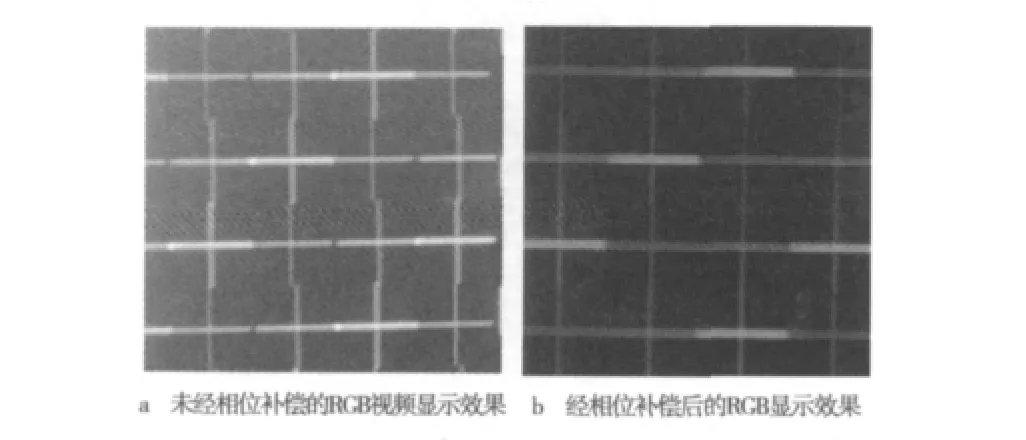

對于工程實踐中傳輸的視頻模擬信號,用此方法進行相位自動補償。在發送端接200 m雙絞網線和接收端相連,發送端輸出無相位差的紅綠藍標準信號,經傳輸后,在接收端拍攝到的顯示器截圖如圖8a所示。啟動相位自動補償功能后,針對同一位置拍攝的顯示器截圖如圖8b所示。

圖8 效果對比圖

在圖8的效果對比中,圖8a是未經相位補償的RGB視頻顯示效果,它們在相位上的相差可以從豎直方向上看出,紅綠藍的豎線都沒有重合,紅信號比綠信號滯后,綠信號比藍信號滯后,在畫質上會出現拖尾現象;右側是經過自動補償的RGB顯示效果,紅綠藍的豎線完全重合,即消除了相位差,畫質會顯得更清晰。目前,此技術方法已經用在長線視頻傳輸中,效果良好。

[1]郝學元,張靜.視頻延長信號的自動校色方法[J].自動化技術與應用,2011,30(9):14-16.

[2]陳尚松,雷加,郭慶.電子測量與儀器[M].北京:電子工業出版社,2009:126-127.

[3] Xilinx corporation.Spartan-3 FPGA family:data sheet[EB/OL].[2012-02-02].http://www.xilinx.com/support/documentation/data_sheets/ds099.pdf.